Формирователь импульсов записи

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в электрически программируемых полупостоянных ЗУ, использующих инжекцию горячих носителей для записи информации в ячейки памяти накопителя. Цель изобретения - повышение надежности устройства . Поставленная цель достигается тем, что в формирователь введены третий ключевой транзистор 13 и запоминающий транзистор 12 с соответствующими связями . При достижении напряжения на щине записи необходимого уровня открывается транзистор 13 и через транзистор 4 тока смещения поддерживает на затворе транзистора записи 1 необходимый уровень. 1 з. п. ф-лы 1 ил. к

СОЮЗ COBF .ИХ

COUMAë!!ñTÐ."1×ÅcHÈÕ

РЕСГ!УБЛИ .{

"; SU 1297114

А1 (50 4 G 11 С 5 02

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ фю

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ (2l) 3877709/24-24 (22) 29.03.85 (46) 15.03.87. Бюл. № 10 (72) В. П. Сидоренко, Н. Б. Груданов и А. А. Хоружий (53) 681.327.6 (088.8) (56) Патент США № 4223394, кл. G 11 С 11/40, 1980.

Патент Великобритании № 2099649, кл. G 11 С 5/02, 1982. (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

ЗАПИСИ (57) Изобретение относится к вычислительной технике и предназначено для использования в электрически программируемых полупостоянных ЗУ, использующих инжекцию горячих носителей для записи информации в ячейки памяти накопителя. Цель изобретения — повышение надежности устройства. Поставленная цель достигается тем, что в формирователь введены третий ключевой транзистор 13 и запоминающий транзистор 12 с соответствующими связями. При достижении напряжения на шине записи необходимого уровня открывается транзистор 13 и через транзистор 4 тока смещения поддерживает на затворе транзистора записи 1 необходимый уровень. 1 з. п. ф-лы

1 ил.

1297114

10 уровня напряжения 11 и запоминающий тран- >о зистор 12, а также третий ключевой транИзобретение относится к вычислительной технике и предназначено для использования в электрически программируемых полупостоянных ЗУ, использующих инжекцию горячих носителей для записи информации в ячейки памяти накопителя.

Целью изобретения является повышение надежности устройства.

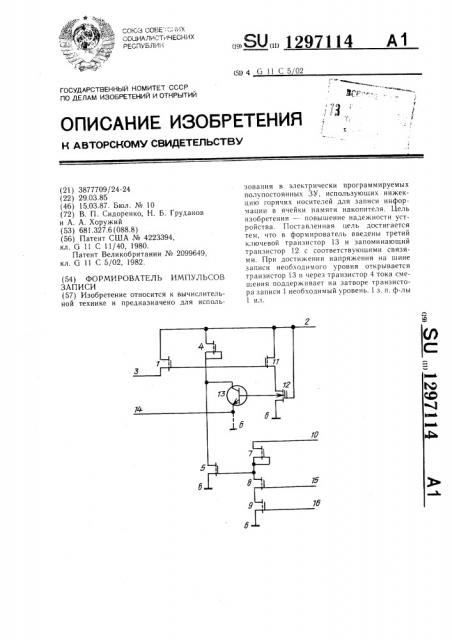

На чертеже представлена электрическая схема формирователя.

Устройство содержит транзистор записи

1, сток которого подключен к шине записи

2, исток соединен с общей числовой шиной

3, транзистор тока смещения 4 и первый ключевой транзистор 5 включенные последовательно между шиной записи 2 и шиной нулевого потенциала 6, нагрузочный транзистор 7, транзистор выборки 8 и второй ключевой транзистор 9, включенные последовательно между шиной питания 10 и шиной нулевого потенциала 6, транзистор сдвига зистор п — р — п типа 13, эмиттер которого подключен к шине отрицательного напряжения смещения 14, управляющие входы

15 и 16. Эмиттер транзистора 13 может быть также подключен к шине нулевого потенциала 6.

Формирователь работает следующим образом.

В режиме записи на шину записи 2 подается высоковольтное напряжение записи (V„ ), достаточное для создания условий канальной инжекции горячих носителей и их захвата на плавающий затвор программируемых ячеек памяти. Если в это время на управляющий вход 15 подается напряжение высокого уровня с устройства дешифрации числовых шин, примерно равное величине напряжения питания на шине 10, а на управляющем входе 16 также устанавливается напряжение высокого уровня (примерно равное напряжению питания), транзистор 8 и второй ключевой транзистор 9 переходят в открытое состояние, и, таким образом, затвор первого ключевого транзистора 5 подключен к шине 6 через последовательно включенные транзисторы 8 и 9. При этом первый ключевой транзистор 5 находится в закрытом состоянии и на затвор транзистора 1 и затвор транзистора 11 через транзистор 4 передается напряжение записи с шины 2, которое переключает транзисторы 1 и 11 в открытое состояние. На стоковую область запоминающего транзистора 12 через открытый транзистор 11 передается напряжение, примерно равное разности напряжения записи на шине 2 и порогового напряжения транзистора 11 (V — VT, где

V — величина порогового напряжения транзистора 11) . Когда указанное напряжение на стоке транзистора 12 превышает величину напряжения лавинного пробоя данной стоковой области, в стоковом р — п пере25

ЗО

4О

55 ходе транзистора 12 происходит лавинный пробой и возникает инжекция дырок в подложку кристалла ИС, которая приводит к положительному смещению области подложки вблизи транзистора 12. Так как подложка транзистора 12 является базой биполярного транзистора и — р — и типа 13, то в результате смещения положительным уровнем напряжения локальной области подложки, а следовательно и базы биполярного транзистора 13, он переключается в проводящее состояние. В результате протекания тока в цепи транзистора 13 напряжение на затворе транзистора 11 уменьшается до величины напряжения, при котором через транзистор 11 на стоковую область транзистора 12 передается напряжение, равное напряжению лавинного пробоя р — и перехода стоковой области ячейки, Величина напряжения на затворе транзистора 11 в этом случае примерно равна Ъ + Ъ т, где V, напряжение лавинного пробоя стокового р — п перехода транзистора 12. Напряжение указанной величины одновременно подается

»а затвор транзистора 1, который обеспечивает передачу ча общую числовую шину

3 напряжения, примерно равного . которое через последующие цепи дешифрации битовых шин передается на стоковую область выбранной ячейки памяти в накопителе ЗУ.

Таким образом, напряжение записи на стоковых областях ячеек памяти накопителя

ЗУ ограничивается на уровне напряжения

V которое определяется напряжением начала лавинного пробоя р — и перехода стока транзистора 12, и как следствие исключается работа ячеек памяти накопителя в области лавинного пробоя.

Однако в накопителе реального ЗУ может иметь место разброс величины напряжения лавинного пробоя для различных ячеек памяти, что связано с различием таких структурных параметров как длина и ширина канала, толщина изолирующих окислов, которые в значительной степени влияют на величину напряжения лавинного пробоя стоковой области ячейки и которые возникают в процессе изготовления ЗУ.

Посредством подачи отрицательного напряжения в пределах от минус 0,18 до минус

0,6 B на шину отрицательного напряжения смещения 14 напряжение на затворе транзистора 1 может быть уменьшено на требуемую величину и таким образом исключен лавинный пробой при записи в ячейки памяти накопителя с минимальным напряжением лавинного пробоя стоковой области.

Когда напряжение на стоке транзистора

12 при записи не превышает величину напряжения лавинного пробоя р — n перехода стоковой области, на затвор транзистора

1 через транзистор 4 передается напряжение, равное напряжению записи на шине 2, так как транзистор 13 находится в закрытом состоянии.

1297114

Формула изобретения

Составитель С. Королев

Редактор Н. Горват Техред И. Верес Корректор А. Зимокосов

Заказ 595 55 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

При условии подачи напряжения низкого уровня, примерно равного потенциалу шины 6, на один из входов 15 или 16 на затвор транзистора 5 подается напряжение, равное напряжению питания на шине 10, через транзистор 7. Транзистор 5 переключается в открытое состояние, затвор транзистора 1 соединяется с шиной 6 и напряжение записи не передается на общую числовую шину

3, так как транзистор 1 находится в закрытом состоянии.

Аналогичное состояние реализуется в устройстве подачи напряжения записи на стоковую область ячейки памяти при работе ЗУ в режиме считывания информации с накопителя. В данном режиме на входе

16 постоянно поддерживается напряжение низкого уровня, примерно равное потенциалу на шине б, и независимо от уровня напряжения на входе 15 транзистор 1 находится в закрытом состоянии. Таким образом полностью исключено влияние устройства на работу усилителей считывания информации, которые подключаются к общей числовой шине.

Биполярный транзистор и — р — и типа

13 изготавливается в едином технологиче- ском процессе одновременно с изготовлением ячеек памяти накопителя и элементов функциональных узлов обрамления. Конструкция транзистора 13 включает подложку, которая является базой данного транзистора и одновременно подложкой интегральной схемы запоминающего устройства и транзистора 12 в формирователе импульсов записи на ячейки памяти накопителя, а также диффузионные области и+ типа, охватывающие по периметру область подложки, в которой расположен транзистор записи 12. При этом внутренняя п+ диффузионная область является эмиттером, а внешняя — коллектором биполярного транзистора 13.

1. Формирователь импульсов записи, содержащий транзистор тока смещения, транзистор сдвига уровня напряжения, транзистор выборки, первый и второй ключевые транзисторы, нагрузочный транзистор и транзистор записи, сток которого подключен к шине записи, исток является выходом устройства, а затвор соединен с затвором транзистора сдвига уровня напряжения и с истоком и затвором транзистора тока смещения, сток которого подключен к шине записи, сток первого ключевого транзистора соединен с затвором транзистора записи, исток — с шиной нулевого потенциала, а затвор — с затвором и истоком нагрузочного транзистора, сток которого под ключен к шине питания, а исток — к стоку транзистора выборки, затвор которого является первым управляющим входом уст20 ройства, а исток соединен со стоком второго ключевого транзистора, затвор которого является вторым управляющим входом устройства, а исток соединен с шиной нулевого потенциала, отличающийся тем, что, с целью повышения надежности устройства, в него введены третий ключевой транзистор и — р — n-типа и запоминающий транзистор, управляющий затвор которого подключен к шине записи, исток — к шине нулевого потенциала, сток — к истоку транзистора сдвига уровня напряжения, сток которого подключен к шине записи, коллектор третьего ключевого транзистора соединен с затвором транзистора записи, эмиттер подключен к шине отрицательного напряжения смещения, а база соединена с подложкой запоминающего транзистора.

2. Формирователь по п. 1, отличающийся тем, что, с целью его упрощения, эмиттер третьего ключевого транзистора подключен к шине нулевого потенциала.