Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - расширение диапазона выходного тока Усилитель содержит транзисторы 1 и 2 одной структуры 1-го дифференциального каскада, транзисторы 3 и 4 др. структуры 2-го дифференциального каскада, отражатели 7 и 8 тока генераторы 11 и 12. Вновь введены прямосмещенные диоды 5 и 6, отражатели 9 и 10 тока. 1 ил. (Л Вб/ход

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А1 (19) (11) д1) 4 Н 03 F 3/45

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3963399/24-09 (22) 05. 10,85 (46) 15.03.87. Вюл, № 10 (72) В.Я,Татарин (53) 621,375,024 (088,8) (56) Патент Франции ¹ 2527399, кл. Н 03 F 1/56, 1983. (54) ДИФФЕРЕНЦИАЛЪНЬЙ УСИЛИТЕЛЪ (57) Изобретение относится к радиотехнике, Цель изобретения — рас ширение диапазона Выходного токае

Усилитель содержит транзисторы 1 и 2 одной структуры 1-го дифференциального каскада, транзисторы 3 и 4 др. структуры 2-го дифференциального каскада, отражатели 7 и 8 тока; генераторы 11 и 12. Вновь введены прямосмещенные диоды 5 и 6, отражатели 9 и 10 тока. 1 ил.

1297209

Изобретение относится к радиотехнике и электротехнике, в частности к усилителям с дифференциальным входом.

Цель изобретения — расширение диапазона выходного тока.

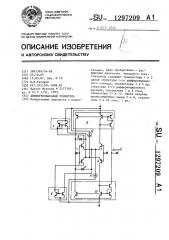

На чертеже представлена электрическая принципиальная схема предлагаемого дифференциального усилителя, Дифференциальный усилитель содержит первый и второй транзисторы 1 и 2 одной структуры первого дифференциального каскада, первый и второй тринзисторы 3 и 4 другой структуры второго дифференциального каскада, первый прямосмещенный диод 5, второй прямосмещенный диод 6, первый и второй отражатели 7 и 8 тока, третий и четвертый отражатели 9 и 10 тока, первый .и второй генераторы )1 и 12 тока.

Дифференциальный усилитель работает следующим образом, Входной дифференциальный сигнал действует на входы дифференциального усилителя. Допустим, что этот сигнал токов, что сильнее открывается первый транзистор 1 (по сравнению с

: вторым транзистором 2) В этом случае сильнее открывается и второй транзистор 4, коллекторный ток которого попадает на вход управления четвертого отражателя 10 тока, вызывая увеличение тока на его выходах по сравнению с состоянием, когда дифференциальный сигнал равен нулю, Очевидно, что ток на выходах третьего отражателя 9 тока уменьшается.

Поэтому ток на втором выходе четвертого отражателя 10 тока станет больше тока на втором выходе третьего отражателя 9 тока, первый прямосмещенный диод 5 открывается и разностной ток попадает в эмиттеры первого и второго транзисторов

1 и 2. Поскольку первый транзистор 1 открыт входным сигналом больше, чем второй, то разностный ток первого прямосмещенного диода 5 попадает на вход управления первого отражателя 7 тока, а с его выхода— в эмиттеры транзисторов 3 и 4, позволяя тем самым нарастать току в коллекторе: второго транзистора 4, а значит и на первом выходе четвертого отражателя 10 тока, т.е. на выходе дифференциального усилителя.

Такой процесс будет продолжаться до тех пор, пока на выходе дифференциального усилителя не установится напряжение, заданное входным дифференциальным сигналом и цепями отрицательной обратной связи (не показаны). Разностный ток третьего и четвертого отражателей 9 и 10 тока через первый прямосмещенный диод 5 нарастать не сможет, поскольку это вызвало бы через цепи отрицательной обратной связи падение дифференциального сигнала на входах дифференциального усилителя. Сквозной ток, проходящий через нагрузку на выходе, задается величиной токов первого и второго генераторов 11 и 12 тока и не может превышать их величины, поскольку нет механизмов, увеличивающих его. Если бы часть разностного тока через первый прямосмещенный диод 5 ответвлялась вторым транзистором 2 и протекала через его коллектор и управляющий вход третьего отражателя 9 тока, то это привело бы к уменьшению раэностного тока по абсолютной величине, и, соответственно, к возрастанию дифференциального сигнала на входах (через цепи отрицательной обратной связи)настолько, что весь разностный ток протекал бы через первый транзистор 1.

В случае появления на входе дифференциального усилителя дифференциального сигнала противопо ложного знака процесс возрастания тока на выходе протекает симметрично, т. е. 0 увеличивается ток на выходах третьего отражателя 9 тока, а на выходах четвертого отражателя 10 тока он уменьшается. В этом случае открывается второй прямосмещенный диод 6 у5 и разностный ток через него и первый транзистор 3 втекает во вход управления второго отражателя 8 тока, что увеличивает ток на его выходе, и, соответственно, на выходах

50 третьего отражателя 9 тока. Коэффициенты передачи по току в третьем и четвертом отражателях 9 и 10 тока с входа управления на первый выход можно взять значительно большими едини55 цы, а с входа управления на второй выход — равным единице, Это позволит получать на выходе дифференциального усилителя значительные токи при пренебрежимо малых токах через первый

129720 налах.

Составитель Н,Дубровская

Редактор Ю.Середа Техред М.Ходанич . Корректор М.Самборская

Заказ 794/60 . Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная,4

I..и второй дифференциальные каскады на транзисторах 1, 2 и 3, 4, т,е. предлагаемый двухтактный усилитель мощности обладает большим КПД.

Кроме того, преимуществом предлагаемого усилителя является его полная симметрия, что уменьшает нелинейные искажения в выходных сигФормула изобретения

Дифференциальный усилитель, содержащий первый дифференциальный каскад, выполненный на первом и вто-..15 ром транзисторах, имеющих одну структуру, коллектор первого транзистора соединен с входом управления первого отражателя тока, а эмиттеры транзисторов объединены и подключе- 20 ны .к выходу первого генератора тока, и второй дифференциальный каскад, выполненный на первом и втором транзисторах, имеющих другую структуру, коллектор первого транзистора соединен с входом управления второго отражателя тока, а эмиттеры транзисторов объединены и подключены к выходу второго генератора тока, при этом бызы первых транзисторов первого и второго дифференциальных каскадов объединены и являются одним входом дифференциального усилителя, 9 4 а базы вторых транзисторов объединены и являются другим входом дифференциального усилителя, о т л и— ч а ю шийся тем, что, с целью расширения диапазона выходного тока, введены третий и четвертый отражатели тока, между объединенными эмиттерами транзисторов первого дифференциального каскада и объединенными эмиттерами транзисторов второго дифференциального каскада введены последовательно соединенные прямосмещенные первый и второй диоды, точка соединения которых подключена к вторым выходам третьего и четвертого отражателей тока, выход первого отражателя тока соединен с объединенными эмиттерами транзисторов . второго дифференциального каскада, выход второго отражателя тока соединен с объединенными эмиттерами транзисторов первого дифференциального каскада, коллектор второго транзистора первого дифференциального каскада соединен с входом управления третьего отражателя тока, коллектор второго транзистора второго дифференциального каскада соединен с входом управления четвертого отражателя тока, при этом первые выходы третьего и четвертого отражателей тока объединены и являются выходом дифференциального усилителя.