Цифровой фильтр с симметричной конечной импульсной характеристикой

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано при создании устройств цифровой обработки сигналов в реальном масштабе времени. Целью изобретения является повышение помехоустойчивости цифрового фильтра с симметричной конечной импульсной характеристикой. Цифровой фильтр с симметричной конечной импульсной характеристикой содержит первый и второй блоки 1 и 2 памяти, первый и второй счетчики 3 и 4 адреса , счетчик 5 начального состояния, комбинационнЕяй сумматор 6, умножитель 7, накапливающий сумматор 8, третий блок 9 памяти и третий счетчик 10 адреса. Счетчики 3,4 и 5 выполнены по модулю, равному порядку фильтра. Цель изобретения достигается введением счетчика 5, устанавливающего синхронно счетчики 3 и 4 в начальное состояние, что позволяет восстановить нормальную работу устройства после сбоя счетчика 3 или 4 в каждом новом цикле счета. 3 ил. 2 табл. to (Л L Ю СО ND efjuff.l

COOS СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 Н 03 Н 17/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К д ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТаЕННЫй HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3966145/24-24 (22) 10,10 ° 85 (46) 15.03.87. Бюл. ¹ 10 (72) А.Г.Галкин, IO.Ô.Петров и В.А.Солонников (53) 62-50 (088.8) (56) Авторское свидетельство СССР № 649126, кл. Н 03 Н 7/12, G 06 Р 7/38, 1972 (54) ЦИФРОВОЙ ФИЛЬТР С СИММЕТРИЧНОЙ

КОНЕЧНОЙ ИМПУЛЬСНОЙ ХАРАКТЕРИСТИКОЙ (57) Изобретение относится к радиотехнике и может быть использовано при создании устройств цифровой обработки сигналов в реальном масштабе времени. Целью изобретения является повышение помехоустойчивости цифрового фильтра с симметричной конечной

„„SU„„12 7212 A i импульсной характеристикой. Цифровой фильтр с симметричной конечной импульсной характеристикой содержит первый и второй блоки 1 и 2 памяти, первый и второй счетчики 3 и 4 адреса, счетчик 5 начального состояния, комбинационный сумматор 6, умножитель 7, накапливающий сумматор 8, третий блок 9 памяти и третий счетчик 10 адреса. Счетчики 3,4 и 5 выполнены по модулю, равному порядку фильтра. Цель изобретения достигается введением счетчика 5, устанавливающего синхронно счетчики 3 и 4 в начальное состояние, что позволяет восстановить нормальную работу устройства после сбоя счетчика 3 или 4 в каждом новом цикле счета. 3 ил .

2 табл.! 12972

Изобретение относится к радиотехнике и может быть использовано при цифровой обработке сигналов в реальном масштабе времени °

Цель изобретения — повышение помехоустойчивости.

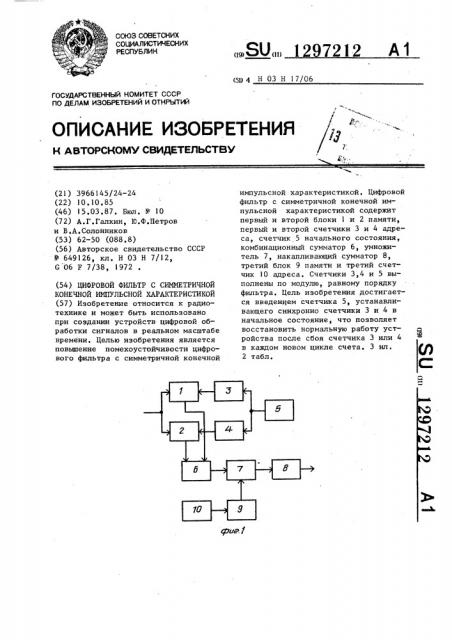

На фиг.1 представлена блок-схема предлагаемого цифрового фильтра с симметричной конечной импульсной характеристикой; на фиг.2 — схема, по !О ясняющая работу предлагаемого устройства в течение первых четырех циклов; на фиг.3 — схема, поясняющая ðàботу известного устройства в течение первых четырех циклов. !

На фиг.1 приняты следующие обозначения: первый и второй блоки 1 и 2 памяти, первый и второй счетчики 3 и 4 адреса, счетчик 5 начального состояния, комбинационный сумматор 6, умножитель 7, накапливающий сумматор

8, третий блок 9 памяти, третий счетчик 10 адреса, Устройство работает следующим образом, Цикл работы устройства включает два этапа. В течение первого этапа осуществляется запись отсчетов входного сигнала в блоки 1 и 2 памяти, а в течение второго — вчитывание отсчетов и их дальнейшая обработка.

В течение первого этапа состояние счетчика 5 начального состояния записывается в счетчики 3 и 4 адреса и таким путем определяется адрес ячеек обоих блоков памяти, в которые записывается отсчет входного сигнала.

Счетчики 3 — 5 считают по модулю N равному порядку фильтра, причем в течение второго этапа счетчик 3 осуществляет прямой счет, а счетчики 4 и 5 — обратный.

На первом такте второго этапа состояние счетчика 3 остается неизмен- 45 ным, а состояние счетчика 4 уменьшается на единицу и осуществляется считывание записанных отсчетов сигнала иэ обоих блоков памяти (начального из блока 1 памяти и конечного из блока 2 памяти). ha последующих тактах второго этапа счетные импульсы подаются одновременно на оба счетчика адреса и продолжается считывание пар отсчетов сигнала с обоих блоков памя- 55 ти. Каждая пара отсчетов суммируется в комбинационном сумматоре 6, полученная сумма умножается в умножителе

7 на соответствующий коэффициент, ко12 2 торый считывается из блока 9 памяти по адресу, формируемому счетчиком 10.

Полученные произведения накапливаются в накапливающем сумматоре 8. Накопленные значения поступают на выход устройства и в это же время счетный импульс подается на счетчик

5, содержимое которого уменьшается на единицу и начинается первый этап следующего цикла с новым начальным состоянием.

Цифровой фильтр с симметричной конечной импульсной характеристикой в отличие от известного устройства (фиг.3) может иметь четный или нечетный порядок N. Б первом случае из обоих блоков памяти считывается N/2

N — 1 пар отсчетов а во втором (- ††)

Э

N-! пар отсчетов. Последний (— — — + 1)

2 отсчет считывается только из блока 1 памяти и чере=", умножитель поступает в накапливающий сумматор.

Таким образом, счетчики 3 и 4 в начале каждого цикла синхронно устанавливаются в нужное состояние с помощью счетчика 5. Следовательно, после единичного сбоя одного из счетчиков 3 или 4 нормальная работа восстанавливается уже в следующем цикле работы. .Если в известном устройстве (фиг,3) единичный сбой одного из счетчиков 3 или 4 приводит к тому, что все N отсчетов выходного сигнала окажутся неправильными, то в данном устройстве в аналогичной ситуации появится только один неправильный отсчет выходного сигнала. Поэтому помехоустойчивость предлагаемого устройства в Н раз вьппе, чем у известного.

Кроме того, использование идентичных счетчиков 3 — 5 позволяет снизить затраты на конструирование и изготовление предлагаемого устройства. Следует отметить также, что счетчик 5 работает в N раз медленнее, чем счетчики 3 и 4 и поэтому его помехоустойчивость вьппе или может быть сделана выше.

Работу устройства поясним примером для случая седьмого порядка (и = 7).

На фиг.2 представлены состояния для четырех последовательных циклов работы устройства. В табл,1 указаны

3 12972 состояния счетчиков 3 — 5, обозначенные соответственно как К1, К2 и КЗ.

Два блока памяти содержат по 7 ячеек (номера от 0 до 6) . Входящие двойные стрелки указывают адреса, по которым осуществляется запись отсчетов входного сигнала, выходящие двойные стрелки — адреса, по которым вы-. полняется считывание, Пунктирные стрелки указывают последовательность fp и направление изменения адресов при считывании пар отсчетов сигнала из блоков памяти.

Работа устройства начинается с состояния счетчика 5, равного О. Это 15 число со счетчика 5 переписывается в счетчики 3 и 4 и по этому адресу записывается отсчет входного сигнала в нулевые ячейки обоих блоков 1 и 2 памяти. Далее состояние счетчи- 20 ка . 4 уменьшается на единицу и становится равным (О-1)mod 7=6. После этого счетчик 3 начинает считать в прямом направлении, а счетчик 4— в обратном. Образуются пары адресов 25 (О,б),(1,5),(2,4), по которым иэ блоков 1 и 2 памяти считываются saпомненные отсчеты сигнала (табл.1 столбцы 2 и 3). Последний отсчет 3 считывается только из блока 1 памя- 30 ти. На этом цикл обработки заканчивается. Состояние счетчика 5 уменьшается на единицу и новый цикл начинается с начального адреса (О-1)шой 7

6 (фиг.2) 35

Для сравнения на фиг,3 представлены состояния для тех же циклов работы известного устройства прототипа, а в табл.2, формируемые счетчиками адреса. При выбранном порядке N=j 40 первый блок памяти должен содержать

И+1=4 ячейки (адреса от О до 3), а второй блок памяти должен содержать

М=З ячейки (адреса от 0 до 2). Первый счетчик (К 1)считает по модулю 4,4> а второй (К 2) — по модулю 3.

12 ным его техническим преимуществом по сравнению с известным. Как видно из табл.2 (столбец 3) из-за различных модулей счетчиков адреса в известном устройстве не возможно осуществить контроль правильности работы простыми средствами.

Формула изобретения

Таблица 1

Состояние счетчиков при работе предлагаемого устройства

К1+ К2

КЗ

К2

К1

Цифровой фильтр с симметричной конечной импульсной характеристикой, содержащий уиножитель, накапливающий сумматор, первый и второй блоки памяти, адресные входы которых соединены соответственно с выходами первого и второго счетчиков адреса, а выходы— соответственно с первым и вторым входами комбинационного сумматора, и последовательно соединенные третьи счетчик адреса и блок памяти, о т— л и ч а ю шийся тем, что, с целью повышения помехоустойчивости, введен счетчик начального состояния, выход которого соединен с входами параллельной записи первого и второго счетчиков адреса, первый и второй входы умножителя соединены соответственно с выходами комбинационного сумматораи третьего блока памяти, выход — с входом накапливающего сумматора, а информационные входы первого и второго блоков памяти объединены. (11)mod 7 4

О (9)mod 7 2

В столбце 4 табл.1 и в столбце 3 табл.2 представлена сумма состояний счетчиков 3 и 4 предлагаемого и из- 50 вестного фильтра соответственно. Для предлагаемого-устройства внутри цикла работы для всех тактов эта сумма остается постоянной, Это свойство может быть использовано для контроля 55 правильности его работы.

Возможность контроля правильности работы предлагаемого устройства -прос тыми средствами является дополнитель5 1297212

Продолжение табл,1 б

Продолжение табл.2 (9)шой 7 2

0

0 (10) шой 7=3

О

О

Таблица 2

Состояние счетчиков при работе

1 известного устройства

Kl + К2

К2

О

2 (7)mod 70 (7)mod 7 0 (7)mod 7"О

2 (8)mod 7=1 (8)mod 7=1

r т

1297212

Фиг. 2

Составитель В.Башкиров

Техред М.Ходанич

Редактор Ю.Середа

Корректор M.Ñàìáoðñêàí

Заказ 794/60 Тирах 902 подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4cb

Производственно-полиграфическое предприятие, r.Óæro:,ñ,, ул,Проектная,4