Цифровой фильтр

Иллюстрации

Показать всеРеферат

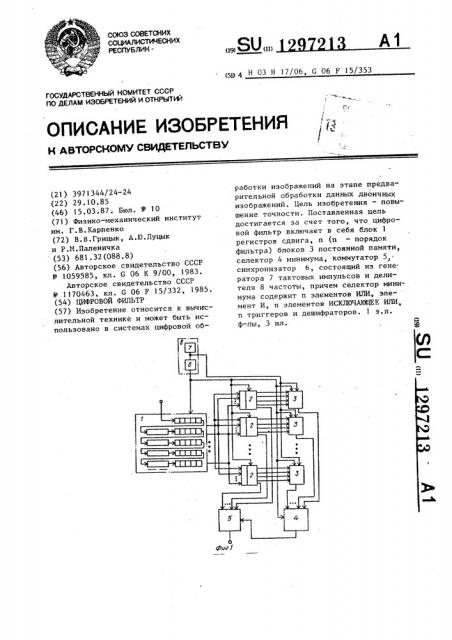

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки изображений на этапе предварительной обработки данных двоичных изобргокений. Цель изобретения - повышение точности. Поставленная цель достигается за счет того, что цифровой фильтр включает в себя блок 1 регистров сдвига, п (п - порядок фильтра) блоков 3 постоянной памяти, селектор 4 минимума, коммутатор синхронизатор 6, состоящий из генератора 7 тактовых импульсов и делителя 8 частоты, причем селектор минимума содержит п элементов ИЛИ, элемент И, п элементов ИСКЛЮЧАКШЩЕ ИЛИ, п триггеров и дешифраторов. 1 з.п. ф-лы, 3 ил. Q N3 х ю ;«:

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕаЪ БЛИК (19) (11) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3971344/24-24 (22) 29.10.85 (46) 15.03.87. Бюл. Р 10 (71) Физико-механический институт им. Г.В.Карпенко (72) В.В.Грицык, А.10.Луцык и P.È.Ïàëåíè÷êà (53) 681.32(088,8) (56) Авторское свидетельство СССР

Ф 1059585, кл. G 06 К 9/00, 1983.

Авторское свидетельство СССР

М 1170463, кл. G 06 F 15/332, 1985. (54) ЦИФРОВОЙ ФИЛЬТР (57) Изобретение относится к вычислительной технике и может быть использовано в системах цифровой об(59 4 Н 03 Н 17/06, G 06 F 15/353 работки изображений на этапе предварительной обработки данных двоичных изображений. Цель изобретения — повышение точности. Поставленная цель достигается за счет того, что цифровой фильтр включает в себя блок 1 регистров сдвига, и (n — порядок фильтра) блоков 3 постоянной памяти, селектор 4 минимума, коммутатор 5, синхронизатор 6, состоящий из гене. ратора 7 тактовых импульсов и делителя 8 частоты, причем селектор минимума содержит и элементов ИЛИ, элемент И, и элементов ИСКЛЮЧАНЖ(ЕЕ ИЛИ, и триггеров и дешифраторов. 1 з.п. ф-лы, 3 ил.

1 129721

Изобретение относится к вычислительной технике и технической кибернетике и может быть использовано в системах цифровой обработки на этапе предварительной обработки данных двоичных изображений.

Цель изобретения - повышение точности коррекции двоичных изображений путем обеспечения оптимальной двухмерной фильтрации изображений, искаженных импульсным шумом..

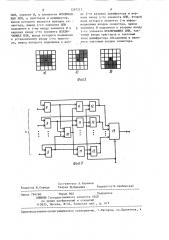

la фиг.! показана структурная схема предлагаемого цифрового фильтра; на фиг.2 — в пределах окна (апертуры) размерами 5х5 три локальные области усреднения, общее число которых равно девяти, на фиг.3 — структурная схема селектора минимума.

0nтимальный фильтр содержит блок

1 регистров сдвига, состоящий из

4 3+5 двоичных разрядов, где f — количество элементов !отсчетов) изображения в одной строке, т.е. длина строки изображения, и блоков 2 постоянной памяти (ПЗУ) (и — порядок фильт25 ра), и регистров 3 сдвига, селектор

4 минимума, коммутатор (мультиплексор) 5, синхронизатор б, состоящий из генератора 7 тактовых импульсов и делителя 8 частоты.

Селектор минимума (фиг.3) содержит и элементов ИЛИ 9, и-входовой элемент

И 1 О,,п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

ll, n триггеров 12, дешифратор 13, Данное устройство осуществляет оптимальную фильтрацию двоичного изображения с использованием алгоритма локального усреднения по одной из девяти возможных областей в пределах окна размерами 5х5. Первая 4О из областей, которая иллюстрируется на фиг.2а, является симметричной и состоит из девяти точек. Остальные восемь попарно пересекающихся областей соответствуют восьми возмож. 45 ным направлениям и содержат по семь элементов каждая. На фиг.26 показана область второго направления, а на фиг.2в — область пятого направления.

Эти восемь областей усреднения соот- 50 ветствуют восьми угловым фрагментам различных уравнений. Для каждой точки входного двоичного изображения !9;(1,3) вычисляются локальные средние значения по точкам .этих областей: 55

1, — — E a(i,1) 0,5

< к ..

К 1» к а„

О, в противном случае.

rgle k = 1,9;

M k-я область усреднения;

Q — количество точек k-й области усре,цнения (u,=9,и 7 при

m=2 9); а — среднее значение по Е-й обк ласти.

Затем вычисляются локальные дисперсии и по этим девяти областям следующим образом: 2

d„- — (g(i,j)-à i, k =1,9, 4 к,.

j1

Значения результата оптимальной фильт— рации f(i,j) определяются выражением

f(i,j) =d где р=:агр ш1п {d ), 1 «k«9

I .å. решение принимается по минимуму локальной .дисперсии.

Цифровой фильтр работает следующим образом.

Элементы входного двоичного изображения в процессе строчной развертки изображения последовательно поступают на вход блока 1 регистра сдвига, состоящего из (4 f,+ 5) разрядов.

Частота следования элементов изображения определяется частотой импульсов синхронизации на первом выходе синхронизатора 6, который является выходом делителя 8 частоты. Частота импульсов на выходе делителя часто— ты в четыре раза меньше частоты ГТИ

7. При поступлении тактового импульса с синхронизатора на тактовый вход

1 сдвигом блока 1 проходит сдвиг в нем информации на один разряд и запись очередного элемента входного иэображения в первый разряд регистрации. В каждом такте работы устройства в 25 разрядах блока 1 сдвиговых регистров, которые показаны на фиг.l формируется окрестность текущего элемента иэображения (окно) размерами 5х5. Локальные средние значения а„ и локальные дисперсии дк, где k = l,п вычисляются таблично с помощью и ПЗУ 2. Входы k-ro

ПЗУ 2 соединены с выходами тех разрядов блока 1 регистра сдвига> в которых хранятся элементы изображения k-й локальной области. Например, п разрядов адресного входа первого

ПЗУ 2 соединены с выходами центральных разрядов блока 1 регистра сдвп1а иэ окна размерами 5х5. Содержимое

3 129721 ячеек памяти ПЗУ 2 программируется таким образом, что в первый разряд одного слова k-го ПЗУ 2 записывается значение локального среднего а, а в остальные четыре разряда слова записывается двоичный код локальной дисперсии d„. Таким образом, в каждом такте работы устройства на выходах всех ПЗУ 2 формируются двоичные коды локальных средних значений 10 и дисперсий двоичного изображения для девяти заданных областей. Код

i-й локальной дисперсии подается на параллельный вход i-го регистра 3 сдвига и при поступлении тактового импульса с первого выхода синхронизатора 6 происходит его запись в этот регистр 3 сдвига. С последовательного выхода всех регистров 3 сдвига сигналы, соответствующие пер- 20 вым (старшим) разрядам локальных дисперсий, параллельно поступают на входы селектора 4 минимума. Селектор 4 минимума предназначен для определения двоичного кода номера той локаль-2 ной области изображения, для которой в заданном такте работы устройства локальная дисперсия минимальна.

Перед началом определения минимума входной последовательности п чисел, все п триггеров 12 устанавливаются в состояние "On путем синхрониэирующего импульса от синхронизатора

6. В каждом такте работы селектора минимума, который задается ГТИ 7, в синхронизаторе 6 определяется i-й разряд минимума чисел (на выходе элемента И 10) путем анализа с помощью n eMeH on HJIH 9, п-входового элемента И 10 и и элементов ИСКЛЮЧАЮ40

ЩЕЕ ИЛИ 51 i-х разрядов всех и чисел.

При этом в нулевом состоянии остаются только триггеры 12, соответствующими числами, которые являются кандидатами на минимум после анали45 за 1-ro разряда все чисел. После тактов работы селектора минимума, где

m — количество разрядов входных чиI сел (в данном случае m=4) с помощью дешифратора 13 выполняется преобразование входного п ðàçðÿäíoãî кода номера минимального числа в позиционный двоичный код, состоящий из

j1opzN) Разрядов (где f ) — знак, обо 55 значающий округление до ближайшего целого числа, не меньшего данного).

Триггер 12 (или триггеры, если имеется несколько одинаковых минимальных

3 4 чисел), который соответствует минимуму остается в состоянии "0, а остальные триггеры !2 будут в состоянии "1". Такой преобразователь кода может быть реализован в виде ПЗУ, на и-разрядный адресный вход которого подается код выходных значений п триггеров 12. Код номера .минимального значения дисперсии по и локальным областям, состоящий из четырех разрядов, поступает на управляющий вход мультиплексора 5. В результате этого, на выходе мультиплексора 5 по— является локальное среднее значение по той же области, для которой дисперсия минимальна, и это значение является очередным элементом выходного изображения устройства. формула изобретения

1. Цифровой фильтр, содержащий блок регистров сдвига, и (n — порядок фильтра) блоков постоянной памяти и коммутатор, причем i-й (i=1,n) выход блока регистров сдвига подключен к входам i-го разряда адреса всех блоков постоянной памяти, входы считывания которых объединены с тактовым входом блока сдвиговых регистров и подключены к первому выходу синхронизатора, а информационный вход блока регистров сдвига является информационным входом фильтра, о т л и ч а юшийся тем, что, с целью повышения точности, в него введены и регистров сдвига и селектор минимума, выход которого подключен к управляющему входу коммутатора, выход которого является информационным выходом фильтра, 1-й информационный вход коммутатора подключен к выходу первого разряда i-го блока постоянной памяти, выходы разрядов кроме первого i-го блока постоянной памяти подключены к входам соответствующих разрядов

i-го сдвигового регистра, выход которого подключен к i-му информационному входу селектора минимума, тактовый вход которого объединен с тактовым входом i-ro регистра сдвига и подкпючен к первому выходу синхрони затора, второй выход которого подключен к входу управления сдвигом

i-го регистра сдвига.

2. Цифровой фильтр по и. l, о т л и ч а ю шийся тем, что селектор минимума содержит п элементов

1297213 айаг 2

Составитель А.Баранов

Редактор IO.Середа Техред Я.gpданич . Корректор M.Ñàìáoðñêàÿ

:Заказ 794/60 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, 0-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,, г.ужгород, ул.Проектная, 4

К1Н элемент И, п элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, и триггеров и дешифратор, выход которого является выходом се- i лектора, выход i-го элемента ИЛИ подключен к i-му входу элемента И и первому входу -го элемента ИСКЛЮ-

ЧАЮЩЕЕ ИЛИ, выход которого подключен к установочному входу i-го триггера, выход которого подключен к входу i-го разряда дешифратора и первому входу i ãî элемента ИЛИ, второй вход которого является д-м информационным входом селектора, выход элемента И подключен к второму входу

i ãî элемента ИСКЛОЧАРЩЕЕ ИЛИ, тактовые входы триггеров и тактовый вход дешифратора объединены и являются тактовым входом селектора.