Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования аналоговой величины в равнозначную форму кода с иррадиональньтми отрицательными основаниями. Цель изобретения - повышение быстродействия и расширение области применения. Аналого-цифровой преобразователь содержит входную шину 1, ключ 2 выборки, аналоговьй запоминающий элемент 3, ключ 4 сброса, буферный каскад 5, сумматор 6, блок 7 эталонных величин, первьм и второй блоки 8, 9 ключей, первьй и второй распределители 10, , 11 рмпульсов, блок 12 компараторов, блок 13 управления, шину 14 тактовых импульсов, выходные шины 15. Введение второго блока 9 ключей, первого и второго распределителей 10, 11 импульсов , ключей 2 и 4, аналогового запоминающего элемента 3 и буферного каскада 5 и изменение алгоритма работы позволило повысить быстродействие за счет одновременного определения сразу двух разрядов выходного кода и расширить область применения (Л ю со ГчЭ го 4 pi/e.f

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1

„„SU„„1297224 (11) 4 Н 03 М 1/26

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,: д

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3963082/24-24 (22) 14. 10.85 (46) 15.03.87. Бюл. - 10 (72) А.П.Стахов, Н.А.Соляниченко, В.В.Замчевский, Г.Ф.Фролов и С.И.Золотарев (53) 681.325(088.8) (56) Гуревич В.З. и др. Импульснокодовая модуляция в многоканальной телефонной связи. M. Связь, 1973, с. 135.

Лаврентьев В.Н. и др. Аналого-цифровые преобразователи двухстороннего уравновешивания. Киев: Знание, 1982, с.15, рис.4. (54) АНАЛОГО-11ИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования аналоговой величины в равнозначную форму кода с иррациональными отрицательными основаниями. Цель изобретения — повышение быстродействия и расширение области применения. Аналого-цифровой преобразователь содержит входную нину 1, ключ 2 выборки, аналоговый запоминающий элемент 3, ключ 4 сброся, буферный каскад 5, сумматор 6, блок 7 эталонных велиария, первый и второй блоки 8, 9 ключей, первый и второй распределители 10,, 11 импульсов, блок 12 компараторов, блок 13 управления, шину 14 тактовых импульсов, выходные шины 15. Введение второго блока 9 ключей, первого и второго распределителей 10, 11 импульсов, ключей 2 и 4, аналогового запоминающего элемента 3 и буферного каскада 5 и изменение алгоритма работы позволило повысить быстродействие за счет одновременного определения сразу двух разрядов выходного кода и расширить область применения

1297?24

Г (+1 +Р+г

d =at +сг в самосинхронизирующихся системах передачи информации за счет преобразования аналоговой величины в равно1

Изобретение относится к вычислительной технике и цифровой передаче информации и может быть использовано для преобразования аналоговой величины в равнозначную форму кода с иррациональными отрицательными основаниями (ИОО).

Цель — повышение быстродействия и расширение области применения за 10 счет обеспечения возможности преобразования аналоговой величины в равнозначную форму кода с иррациональными отрицательными основаниями.

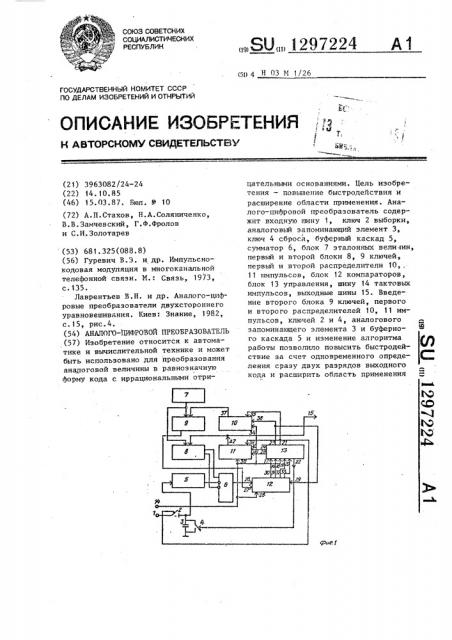

На фиг.1 приведена функциональная 15 схема аналого-цифрового преобразователя; на фиг.2 — функциональная схема блока управления; на фиг.3 — схема блока компараторов; на фиг.4— схема первого распределителя импуль- 20 сов; на фиг.5 — схема второго распре— делителя импульсов; на фиг.б — графсхема алгоритма работы аналого-цифрового преобразователя.

Аналого-цифровой преобразователь (фиг. 1) содержит входную шину 1, ключ 2 выборки, аналоговый запоминающий элемент 3, ключ 4 сброса, буферный каскад 5, сумматор 6, блок 7 эталонных величин, первый и второй 30 блоки 8 и 9 ключей, первый и второй распределители 10, 11 импульсов, блок

12 компараторов, блок 13 управления, шину. 14 тактовых импульсов, выходные шины 15. 35

Блок 13 управления содержит тактовый вход 16, входы 17 — 20 с первого по четвертый, выход 21 — 25 с первого по пятый, блок 12 компараторов содержит первый и второй информационные входы 26, 27, вход 28 опроса, управляющий вход 29, выходы 30 — 33 с первого по четвертый. Первый распределитель 10 импульсов содержит тактовый вход 34, первый и второй входы

35, 36, выходы 37; второй распределитель 11 импульсов содержит тактозначную форму кода с иррациональны.".— ми основаниями. 1 з.л. A-лы, б ил,, 3 табл. вый вход 38, выходы 39 — 41 с первого по третий, выходы 42.

Блок I 3 управления (фиг. 2) содер— жит элементы 43 — 49 с первого по седьмой, элемент ИЛИ-HF 50, первый и второй элементы ИЛИ 51, 52, инверторы 53 — 55 с первого по третий,элемент И-HF. 56, триггеры 57, первый и второй формирователи 58, 59 импульсов, делитель 60 частоты.

Блок 12 компараторов (фиг.3) содержит компараторы 61 — 66, триггеры

67 — 70, элемент ИПИ 71, элемент

2И-ИПИ-HE 72, первый и второй инверторы 73, 74, элемент И 75.

Первый распределитель 10 импульсов (фиг.4) содержит регистр 76 сдвига, формирователи 77 — 79 коротких импульсов с первого по третий, элемент ИЛИ 80, элемент И 81, триггер

82, элемент 83 задержки.

Второй распределитель 11 импульсов (фиг.5) содержит делитель 84 частоты на 2, двоично-десятичный счетчик 85, дешифратор 86, инверторы

87 — 97, элементы И 98 - 107, регистр 108.

Аналоro-цифровой преобразователь работает следующим образом.

В аналого-цифровом преобразователе на основе кодов с иррациональными основаниями веса разрядов определяются рекурентным соотношением где сг. — вес f-го разряда;

p=0;1; 2...

Аналого-цифровой преобразователь работает цо алгоритму, приведенному на фиг.б.

Рассмотрим работу преобразователя. Пусть веса разрядов кода с иррациональным основанием при р = 1 равны: г„= 0,000; <, = 0,001;

= 0,001р < = 0,002; " = o 003;

3 I 2972 — 0021; у =0034; y=0,055;ó

Сумматор 6 построен по схеме диф5 ференциального сумматора. При этом на инвертирующий вход сумматора подается с выхода буферного каскада 5 входной сигнал, к соответствующим входам группы инвертирующих входов 10 сумматора 6 подключены первые выходы первого блока 8 ключей, а к соответствующим входам группы неинвертирующих входов сумматора 6 — вторые выходы первого блока 8 ключей, при этом15 оказывается, что эталонные величины, соответствующие весам четных разрядов, подключаются через первый блок

8 ключей к неинвертирующим входам сумматора 6, а эталонные величины, соответствующие весам нечетных разрядов, — через первый блок 8 ключей к инвертирующим входам сумматора б.

Таким образом, весам, соответствующим четным разрядам, искусственно 25 присваивается знак "-", что позволяет производить кодирование в кодах

ИОО без применения второго (отрицательного) источника опорного напряжения. 30

В табл.1 приведен пример преобразования входного сигнала, равного 5В.

В начале преобразования в блоке

13 управления при помощи первого формирователя 58 импульсов вырабатывается строб-импульс, который устанавливает в нулевое состояние счет чик 85 и регистр 108 второго распре- 4р делителя 11 импульсов, записывает

"1" в старший разряд регистра 76 первого распределителя 10 импульсов, замыкает ключ 2, в результате чего в аналоговый запоминающий элемент 3 45 записывается напряжение, равное входному. Затем по первому тактовому импульсу первый распределитель 10 импульсов замыкает ключ (i-1)-ro разряда во втором блоке 9 ключей и на др вход 27 блока 12 компараторов поступает (i-1)-й разряд, в это время ча вход 26 блока 12 компараторов подано входное напряжение с сумматора 6.Ло концу тактового импульса результаты сравнения записываются в триггеры

67 — 70 и поступают в блок 13 управ.ления, который вырабатывает значения .а,. и а „ разрядов выходного кода.

24

В рассматриваемом случае на первом такте в результате прохождения по первой ветви алгоритма (блоки 1, 2, 3, 4, .5,фиг.б} определяются значения а„= 1, а, = 0.

Эти значения разрядов выходного кода записываются в регистр 108 второго распределителя 11 импульсов и включают ключ в первом блоке 8 ключей, соответствующий весу, разряда. Так как этот разряд нечетный, то он подключается на неинвертирующий вход сумматора 6, в результате чего на его выходе получается разность U

Во втором такте аналогично, как и в первом, производится сравнение полученного U„; с весом 16-го разряда.

По результату сравнения блок 13 правления вырабатывает две единицы, которые включают соответствующие разряды на сумматор 6, аналогично предыдущему случаю, но так как они подаются на разные входы сумматора (неинвертирующий и инвертирующий), то в результате вычитания получается напряжение, равное V, т.е. весу ! Р пятнадцатого разряда (-1 597+0,987

= -0,610), далее это напряжение вычитается из У

Х1

Луть соответствует третьей ветви алгоритма (блоки 6, 8, 10, фиг.б).

В следующем, третьем, такте преобразования происходит сравнение с e. весом, для этого "1" в регистре 76 первого распределителя 10 импульсов необходимо дополнительно сдвинуть на один разряд. Это достигается следующим образом.

Лри появлении на выходах 24 и 25 блока 13 управления двух "1" триггер

57 устанавливается в единичное состояние, а второй формирователь 78 импульсов первого распределителя 10 импульсов формирует по его переднему фронту короткий импульс, который и сдвигает "1" в регистре дополнительно на один разряд.

При появлении двух нулей на выходе блока 13 управления следующие два ключа в блоке 8 ключей не включаются и суммирование не производится (соответствуют 4 ветви алгоритма блоки 12, 11, фиг.6). Триггер 57 блока 13 управления вновь устанавливается в нулевое состояние, а третий формирователь 79 коротких импульсов первого распределителя 10 импульсов по перепаду иэ " 1" в "0" сигнала с

5 1? 97224 триггера 57 блока 10 управления вырабатывает короткий импульс, который устанавливает триггер 82 первого распределителя 10 импульсов в нулевое состояние. В единичное состояние этот триггер устанавливается после прохождения одного тактового импульса. Таким образом, пропускается один такт и на.следующем этапе преобразования сравнение производится с ;,-ным разрядом, как того тоебует алгоритм. В дальнейшем преобразование производится, как и в описанных тактах.

Таким образом, получается код

1011001001100110011Î

Веса разрядов кода ИОО следующие:

6 изобретения

Формула ч, = 0,000; ч, = 0,001; v„= -0,001;

Ч = 0,002; ч = -0,003 V = 0 005- .= -0,008; 4У = 0,013; V9 = — 0,021; у = 0,034, „ = -0,055; ц,„ = 0,089;

Суммируя веса, соответствующие "1", в полученном коде получаем число 5, т.е преобразованное верно.

В табл.2 и 3 приводятся два приме— ра, показывающие преобразование отрицательного входного напряжения И „

= — 4 В и нулевого входного напряжения. Преобразование производится аналогичным образом.

По концу цикла преобразования блок

13 управления вырабатывает импульс сброса, который устанавливает триггер

57 в "О", замыкает ключ 4 и аналоговый запоминающий элемент 5 разряжается до нуля. Затем цикл повторяется снова.

Таким образом, по окончании процесса кодирования в регистре 108 второго распределителя 11 импульсов сформирован равнозначный выходной код (см.табл. 1-3), количество единиц в котором равно количеству нулей, что резко сужает спектр такой кодовой посылки и убирает постоянную составляющую в ее спектре, а это необ1 ходимо для передачи информации в самосинхронизирующихся волоконно-оптических линиях связи.

Таким образом, в каждом такте ра" боты формируются два разряда выходного кода, что обеспечивает повышение быстродействия преобразователя.

1. Аналого-цифровой преобразователь, содержащий блок эталонных величин, выходы которого подключены к соответствующим информационным входам первого блока ключей, первые выходы которого подключены к соответствующим входам группы инвертиру10 ющих .входов сумматора, вторые выходы подключены к соответствующим входам группы неинвертирующих входов сумматора, вьгход которого подключен к первому, информационному входу бло15 ка компараторов, блок управления, отличающийся тем, что, с целью повышения быстродействия и расширения области применения за счет обеспечения возможности преобразова-.

20 ния аналоговой величины в равнозначную форму кода с иррациональными отрицательными основаниями, введены буферный каскад, ключ выборки, анало— говый запоминающий элемент, ключ сброса, первый и второй распределители импульсов, второй блок ключей, информационные входы которого под-ключены к соответствующим выходам блока эталонных величин, управляющие

ЗО входы подключены к соответствующим выходам первого распределителя им— пульсов, выход подключен к второму информационному входу блока компараторов, вход стробирования которого объединен с тактовыми входами блока

35 управления, первого и второго распределителей импульсов и является шиной тактовых импульсов, первый, второй, третий и четвертый выходы подключе40 ны соответственно к первому, второму, третьему и четвертому входам блока управления, первый выход которого подключен к первым входам первого и второго распределителей импульсов

45 и к управляющему входу ключа выборки, информационный вход которого является входной шиной, выход через буферный каскад подключен к инвертир ющему входу сумматора и шине нуле50 вого потенциала через аналоговый запоминающий элемент, параллельно которому подключен ключ сброса, управляющий вход ключа сброса подключен к второму выходу блока управления, 55 третий выход которого подключен к управляющему входу блока компараторов и второму входу первого распределителя импульсов, четвертый и пятый выходы подключены соответственно к вто12972

Номер такта

Выполняемые операции

Номер ветви

Значения разрядов выходного алгориткода ма

3 4

> - V,, 5> 2,584, да, i = i — 2 = 17

U„=U„; -v, = 5 — 4 181 =0819

2 Б . >-y, 0,819 >0,987, нет, U . > О, да 1

U =U -ч. =0987-0610=0,209, i=i-2=15 1

Xi К1 i-e

U =U i=i-2=13

Ki Ki рому и третьему входам второго распределителя импульсов, выходы которого подключены к соответствующим управляющим входам первого блока ключей и являются выходными шинами устройства.

2. Преобразователь по п.1, о тл и ч а ю шийся тем, что блок управления выполнен на семи элементах И, первом и втором элементах

ИЛИ, элементе ИЛИ-НЕ, первом, втором и третьем инверторах, элементе

И-НЕ, первом и втором формирователях импульсов, триггере, делителе частоты, вход которого объединен с входом первого инвертора и первым входом пятого элемента И и является тактовым входом блока управления, выход первого инвертора подключен 20 к второму входу пятого элемента И, выход которого подключен к первому входу шестого элемента И, выход которого подключен к первому входу третьего элемента И, второй вход под- ключен к выходу первого формирователя импульсов и является первым выходом блока управления, вход первого формирователя импульсов подключен к выходу делителя частоты и объединен З0 с входом второго формирователя импульсов, выход которого является вторым выходом блока управления и подключен к входу обнуления триггера, прямой выход которого является тре- 35

3 U . .>-, 0,209 > -0,233, да

8 тьим выходом блока управления и подключен к первому входу элемента И-НЕ, выход которого через третий инвертор подключен к первому входу второго элемента ИЛИ, второй вход элемента

И-НЕ является третьим входом блока управления, третий вход подключен к выходу второго инвертора, вход которого объединен с первым входом первого элемента И и является первым входом блока управления, второй вход первого элемента И подключен к инверсному выходу триггера, выход подключен к первому входу второго элемента И, второй вход которого является вторым входом блока управления, выход является четвертым выходом блока управления и подключен к первым входам элемента ИЛИ-НЕ, четвертого элемента И и первому входу седьмого элемента И, второй вход которого является четвертым входом блока управления, выход подключен к второму входу второго элемента ИЛИ, выход которого является пятым выходом блока управления и подключен к вторым входам элемента ИЛИ-НЕ и четвертого элемента И, выходы которых подключены соответственно к первому и второму входам первого элемента ИЛИ, второй вход которого объединен с информационным входом триггера, а выход подключен к второму входу третьего элемента И, выход которого подключен к тактовому входу триггера.

Таблица 1

1297224

Продолжение табл. 1

U. = U.=

Хч Хе ю

= 0,209 — 0,233 = -0,024

U. =U. х1 х> х1 О

U» - -- (--о,оо1) = o oo1, 10 U„,. + Ч,, да, Таблица 2

Номер ветви

Выполняемые операции

Номер такта алгорит4 U„.)-V., 0209> 0144, да, i =i — 2=11

5 U„,. ъ —, -0,024 > 0,055, нет, U„. > О, нет

-/-0,055/=0,031, 1. =:i — 2 = 9

Ю . — О, 031 О, 034 — 0,003, х — х — 2 — 7

7 U„, -,, -0,003 > 0,008, нет, U О, нет

U„,. = -0,003 — (-0,008) = 0,005, i = i — 2 = 5

8 U ) - у„, 0,005 ) 0,005, да, U„, =.0005 — 0005 = О, i = i — 2 =: 3

9 U . .>-9, нет, U о О, нет, 2 xi

U ; = U„, — О = 0,001 — 0,000 = 0,001.

1 U. >-У,, нет, U . .>О, нет, Х1 11 xi ох Пх -, =4 — (-2,584) = -1,416,(С17) .1 -1

Значения разрядов выходноro кода

2 U . >-Ч., нет, П . > О, нет, yi

U„. = U„,. - v. = -1,146 — (-0,987) =-0,429(v15) 3 U„, -Ч., нет, U„> О, нет, х V -, = -0,429 — (-0,377) = -0,052(4 13) 1

4 U„. >- Ч,, нет, U„,. > О, нет, U„; = U„., -v,., = -0,052 — (-0,144) = 0,092(911) U„. -Ч-,,, да, U =U Ч; (Ч9) U U . - M. = 0,003 — 0,013 = -0,01 (Ч7) О

9 U„.> Ч;,, нет, U„,> О, нет, U„,. = U„., -Ч;, = -0,002 + 0,001 = -0,00 I (У1) 10 П„. >Y,. „, нет, U„>0, нет

Ux. = 0,003

7 U.) -Ч; д, нет, xi

8 Ох,.>-Ч;, да, (Ч 3) 1297224

Продолжение табл.2

О

О

О

1297224

13

Таблица 3

Номе такт

Номер ветви

Выполняемые операции алгоритма

0 нх О

0„. U„; -Т;, = -0,61 — (-0,377) = -0,233 (Ч13) 1 кi

4 U„,. >- Р;, нет

5 U >-<р,., нет, 7 0х :,, нет

8 U„,.>- Ч;, нет

Uz,. r-Ч... иет, U„; > О, да, U . U . -, = Π— 1,597. — 1 597 (17)

xi х1 1-д

-1,597 — (-0,987) =- -0,61 (Ч15) U „. -0,233 — (-О, 144) = -0,089 (У11) U„,. -0,089 — (-0,055) = -0,034 (99) 6, U«>-Ч1, нет о

U„0эО34 (Ов021) = -0,013 (f 7) U„; -0,013 — (-0,008) = -0,005 (Ч5) U» -0,005 — (-0,003) = -О, 002 (х 3) Значения разрядов выходного кода

1297224

9 U, >- ч,., нет

10 U; <;, да

1 (U„= -0,002 + 0,001 = -0,001 (К 11

Продолжение табл 3

3 (4

1297224

Фиг.4

1297224

1297224

Составитель В.Першиков

Редактор Н.Швццкая Техред А.Кравчук Корректор JI.Пилипенко

Заказ 795/б1 Тираж 902 . Подписное

ВНИКЛИ Государственного коийтета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.Ужгород, ул.Проектная,4