Устройство для синхронного детектирования сигналов с фазовой манипуляцией

Иллюстрации

Показать всеРеферат

Изобретение относится к радиосвязи . Цель изобретения - повьппение помехоустойчивости за счет компенсации синфазной составляющей сосредоточенной помехи. Устройство содержит синхронный детектор (СД) 1, узкополосный фильтр 2, перемножитель 3, блок 4 формирования двоичной последовательности. Вновь введены перемножитель 5, два вычитающих блока 6 и 8, СД 7. Устройство обеспечивает компенсацию мешающего воздействия синфазной составляющей мощной сосредоточенной помехи при синхронном детектировании сигналов с фазовой манипуляцией. I ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 H 04 L 27/20 ф г.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А BTOPGKOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР по делАм изОБРетений и ОткРытий (21) 3963384/24-09 (22) 05.10,85 (46) 15.03.87.Бюл.й 1О (72) В.Г.Вишняков, С.А.-Гавриленко и С.С.Ковров (53) 621.396.626 (088.8) (56) Авторское свидетельство СССР

Ф 172369, кл. Н 03 D 3/02, 1963. (54) УСТРОЙСТВО ДЛЯ СИНХРОННОГО ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ (57) Изобретение относится к радиосвязи. Цель изобретения. — повышение помехоустойчивости за счет компенсации синфазной составляющей сосредоточенной помехи. Устройство содержит синхронный детектор (СД) 1, узкополосный фильтр 2, перемножитель 3, блок 4 формирования двоичной последовательности. Вновь введены перемножитель 5, два вычитающих блока 6 и 8, СД 7. Устройство обеспечивает компенсацию мешающего воздействия синфазной составляющей мощной сосредоточенной помехи при синхронном детектировании сигналов с фазовой манипуляцией. I ил.

1 12972

Изобретение относится к радиосвязи и может быть использовано в системах связи с фазовой манипуляцией.

Цель изобретения — повьппение помехоустойчивости за счет компенсации синфазной составляющей сосредоточенной помехи.

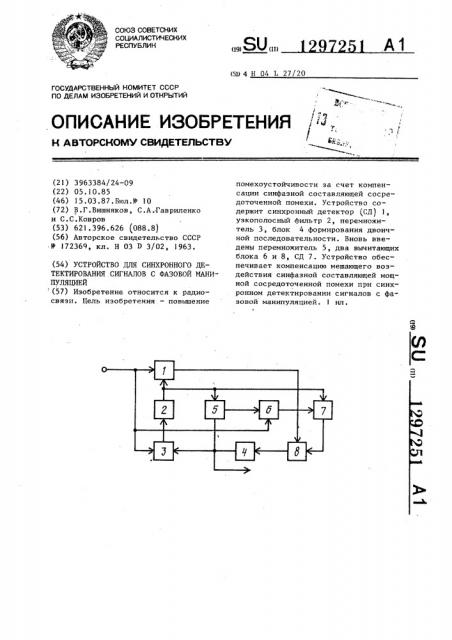

На чертеже изображена структурная электрическая схема предложенного устройства. 1О

Устройство для синхронного детек.тирования сигналов с базовой манипуляцией содержит первый синхронный детектор 1, узкополосный фильтр 2, первый перемножитель 3, блок 4 фор- 15 мирования двоичной последовательнос-. е ти, второй.перемножитель 5, первый вычитающий блок 6, второй синхронный детектор 7, второй вычитающий блок 8.

Устройство работает следующим об- 20 разом.

При отсутствии сосредоточенной помехи в канале и правильных решениях о передаваемых символах на выходе формирования двоичной последовательности блока 4, совпадающих с законом манипуляции сигнала по фазе, после их перемножения с входным фаэоманипулированным сигналом на выходе перемножителя 3 образуется неманипулированный сигнал, который после узкополосной фильтрации фильтром 2 имеет вид (t) = U сов(((t +q )

35 где U(— амплитуда сигнала;

У, — частота сигнала," с — начальная фаза сигнала.

При этом узкополосный фильтр 2 должен быть настроен на частоту сиг- щ нала М,.

Сигнал вида (1) подается в качестве опорного сигнала на второй вход первого синхронного детектора 1, где осуществляется синхронное (когерент- 45 ное) детектирование полезного сигнала. В результате на выходе первого синхронного детектора 1.образуется сигнал вида

П (t) = Х,П, соя(а,t- u,t + (2)

+с, — ц;) который при соответствующем соотношении сигнал/шум определяет правиль55 ные решения на выходе блока 4 формирования двоичной последовательности. Одновременно с этим иа выходе

51 2 второго перемножителя 5 формируется сигнал вида. (I„, = U, сов (и,t+y,+ (1-b(t)) — 1,(3) г (t) = Х,U(.+ Х 11сU„cos(pt +

+ (×с Чп)) (4) где g =Я; Я„ — частота биений между сигналом и помехой; — начальная фаза помехи; — коэффициент передачи первого синхронного детектора 1.

9п

Одновременна с этим помеха, пройдя первый вычитающий блок 6 в начальные моменты времени практически беэ изменений и перемножаясь с опорным сигналом вида (1), на выходе второго синхронного детектора образует сигнал вида

U (t) =K 1JñJJï соз f 52 t + сПг. г с и где Кг " коэффициент передачи второго синхронного детектора 7. где b(t)= i 1 — манипуляционная двоичная последовательность на выходе блока 4 формирования двои ной последовательности;

bä (t) = 1 1 — закон манипуляции входного сигнала.

Тогда, при совпадении b(t) с

Ь (t) на выходе первого вычитающего блока 6 образуется лишь шум, который во втором синхронном детекторе 7 перемножается с опорным сигналом вида 1,1) и интегрируется. Так как корреляция шума в полосе приема и опорного сигнала близка к нулю, то результат синхронного детектирования сигнала на выходЫ первого синхронного детектора 1 проходит на вход блока 4 формирования двоичной последовательности практически без изменений.

При наличии сосредоточенной помехи в полосе приема, частота которой не попадает в полосу пропускания узкополосного фильтра 2, на выходе первого синхронного детектора 1 сиг-! нал имеет вид

Как видно из сравнения выражений (2) и (6), предлагаемое устройство обеспечивает компенсацию мешающего воздействия синфазной составляющей мощной сосредоточенной .помехи при синхронном детектировании сигналов с фазовой манипуляцией.!

Составитель О.Геллер

Редактор Н.!11выдкая Техред Л.Сердюкова Корректор С.Шекмар

Заказ 797/62 Тираж 639 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.ужгород, ул. Проектная, 4, !! 3 12972

При равенстве K< = К, вычитая сигналы вида (4) и (5), на выходе второго вычитающего блока 8 получаем (6) Формула изобретения !5

Устройство для синхронного детектирования сигналов с фазовой манипуляцией, содержащее блок формирования двоичной последовательности, выход которого соединен с первым вхо- 20 дом первого перемножителя, второй вход которого соединен с первым входом первого синхронного детектора, второй вход которого подключен к выходу узкополосного фильтра, вход

25 которого подключен к выходу первого перемножителя, о т л и ч а ю щ е ес я тем, что, с целью повышения помехоустойчивости за счет компенсации синфаэной составляющей сосредоточенной помехи, введены два вычитающих блока, второй синхронный детектор и второй перемножитель, выход которого соединен с первым входом первого вычитающего блока, второй вход которого соединен с первым входом . первого синхронного детектора, второй вход которого соединен с первым входом второго синхронного детектора и с первым входом второго перемножителя, второй вход которого подключен к выходу блока формирования двоичной последовательности, вход которого подключен к выходу второго вычитающего блока, первый вход которого подключен к выходу второго синхронного детектора, второй вход которого подключен к выходу первого вычитающего блока, при этом выход первого синхронного детектора соединен с вторым входом второго вычитающего блока.