Линейный интерполятор

Иллюстрации

Показать всеРеферат

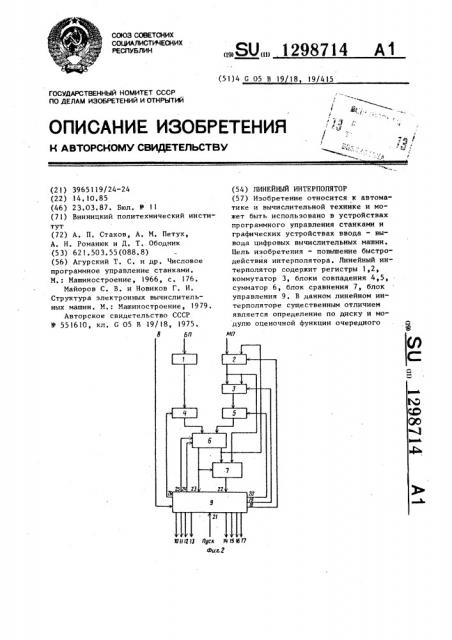

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах программного управления станками и графических устройствах ввода - вывода цифровых вычислительных машин. Цель изобретения - повьш1ение быстродействия интерполятора. Линейный интерполятор содержит регистры 1)2, коммутатор 3, блоки совпадения 4,5, сумматор 6, блок сравнения 7, блок управления 9. В данном линейном интерполяторе существенным отличием является определение по диску и модулю оценочной функции очередного Mf7 а Ё (Л Ю)П2и Пуск П15№П Фиг.2

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)4 G 05 В 19 18 19/415

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

7г / ф % ф

Н ABTOPCHOIVIY СВИДЕТЕЛЬСТВУ

51IQ13 Пуск и t5 617

Фиа8

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3965119/24-24 (22) .14.10.85 (46) 23.03 ° 87. Бюл, У 11 (71) Винницкий политехнический институт (72) А. П. Стахов, А. М. Петух, А. Н. Романюк и Д. Т. Ободник (53) 621,503.55(088.8) (56) Агурский Т. С. и др. Числовое программное управление станками.

М.: Машиностроение, 1966, с. 176.

Майоров С. В. и Новиков Г. И.

Структура электронных вычислительных машин. М.: Машиностроение, 1979.

Авторское свидетельство СССР

В 551610, кл. G 05 В 19/18, 1975.

В БП

„„SU„„1298714 А 1 (54) ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах программного управления станками и графических устройствах ввода — вывода цифровых вычислительных машин.

Бель изобретения — повьппение быстродействия интерполятора. Линейный интерполятор содержит регистры 1,2, коммутатор 3, блоки совпадения 4,5, сумматор 6, блок сравнения 7 блок управления 9 ° В данном линейном интерполяторе существенным отличием является определение по диску и модулю оценочной функции очередного мп

12987 двойного комбинированного перемещения эа два такта работы, Это достигается введением коммутатора, формирующего как одиночное (в цикле подготовки), так и удвоенное (в цикле интерполя" ции) значение меньшего приращения, и блока сравнения, обеспечивающего сравнение модуля оценочной функции с меньшим приращением. Значение оценочной функции определяют только

14. для первой четверти квадранта и в дальнейшем обеспечивается. преобразование полученных перемещений. для других областей посредством простых операций инверсии и коммутации, ре лиэуемых в блоке управления в зависимости от соотношения приращений.

Погрешность аппроксимации не превышает шага дискретизации. 1 з.п. ф-лы, 6 ил., 1 табл. I

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах программного управления стенками и графических устройствах ввода-вывода цифровых вычислительных машин, Цель изобретения — повышение быстродействия интерполятора.

На фиг. 1 показан отрезок аппроксимируемой прямой в первой четверти квадранта и полученный на основе инверсии перемещений данного отрезка— соответствующий отрезок во второй четверти квадранта; на фиг. 2 структурная схема предлагаемого ли15 нейного интерполятора; на фиг ° 3— отрезок аппроксимируемой прямой; на фиг. 4 — функциональная схема реализации блока управления; на фиг. 5 " граф-схема алгоритма функционирования

20 блока управления; на фиг. 6 — функциональная схема реализации сумматора, В основе изобретения лежит возможность однозначного определения перемещений за два такта работы интерполятора по знаку и модулю оценочной функции.

Вывод функций для определения перемещений производится только для

30 значений первой четверти первого квадранта. Трансформация полученных результатов на остальные четверти производится согласно следующим правилам.. 35

Для получения отрезка прямой с а углом наклона — необходимо проинверЪ тировать последовательность приращеЬ-а 40 ний, соответствующих отрезку . На2 фиг. 2 показан пример получения от11 резка прямой с наклоном — на основе

15 известных приращений для прямой с уг4 лом наклона -- путем инвертирования

15 последних. Отрезку прямой с углом

4 наклона — rro ведомой координате

15 соответствует последовательность приращений 0 1000 1000 1000 10, где 1 соответствует диагональному шагу. Инверсия приведенной последовательности (101110111011101) соответствует отрезку прямой с углом наклона

11 причем погрешности аппроксимации

15 указанных прямых совпадают, Укаэанное свойство позволяет путем инверсии получать отрезки прямых во второй четверти квадранта по известным последовательностям приращений соответствующих прямых с первой четверти.

Взаимная перекоммутация последовательностей приращений, формируемых в первой половине квадранта с координаты Х íà Y и с Y на Х, обеспечивает симметричное воспроизведение отрезка прямой во второй половине квадранта относительно биссектрисы угла по заданному отрезку в первой половине квадранта.

При интерполяции отрезка прямой единичными приращениями при 1 4 Х() (д71испольэуется оценочная функция: при U > 7i О, перемещение по оси X u

U; „> =U;, — (h Y1; при Ul> (О, перемещение по Х и Б;+1 „=Б; + ((2!X t— !

+1т1+1 11 — (hY l (, т. е, выполняется диагональный шаг по ведомой координате. В ис3 12987 ходном состоянии значение оценочной функции равно БП (большое приращение).

Во время интерполяции прямой в первой четверти квадранта вслед за перемещением по направлению, характеризуемому меньшей проекцией, т.е. выполнении диагонального шага, обязательно следует перемещение по направлению, характеризуемому большей проекцией. Это объясняется тем, что после выполнения диагонального шага к значению оценочной функции прибавляется значение !!ЬХ I — I д Yll . Поскольку для рассматриваемого случая f5 (первая четверть первого квадранта)

j n Х (vi 2 I n Y l очередное значение оценочной функции после выполнения диагонального шага всегда будет больше О, т,е. следующим выполняется шаг 20 по ведущей координате при отсутствии перемещения по ведомой координате, Таким образом, по ведомой координате возможны следующие сочетания шагов:

01, 10, 00, где 1 соответствует на- 25 личию перемещения, а О отсутствию перемещения. Если очередное значение оценочной функции положительное и выполняется условие U;. — 2ЮУ 7 О, то очередные два перемещения произ- 30 водятся только по оси X. Если же имеет место условие U;- — 2 пУ 6 О, то по ведомой координате возможно сочетание перемещений 10 или 01, причем при 0; -2!AY((), nY выполняется перемещение 10, а при tU;>. -2tnYI(< (DY — перемещение 01.

Линейный интерполятор (фиг ° 2) содержит первый 1 и второй 2 регистры координатных перемещений, коммута-4р тор 3, первый 4 и второй 5 блоки сов— падения, накопительный сумматор 6, блок 7 сравнения, вход 8 линейного интерполятора, блок 9 управления с выходами 10-20, .вход 21 "Пуск" линей-45 ного интерполятора, входы 22-26 блока управления, Блок управления (фиг. 4) содержит триггер 27, узел 28 постоянной памяти, первый регистр 29, триггер 30, 50 второй регистр 31, генератор 32 импульсов. Сумматор (фиг. 6) содержит первый 33 и второй 34 комбинационные сумматоры, регистр 35, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 36. 55

Регистры координатных приращений

1 и 2 служат соответственно для хранения большего и меньшего приращения!

4 4 координат, определяющего отрабатываемый отрезок прямой.

Большее приращение (БП) записывается в регистр 1 по входам, явля ющимся первыми входами устройства.

Выход регистра 1 соединен со входами первого блока 4 сравнения, выход которого соединен с первыми входами накопительного сумматора 6, а управляющий вход — с первым выходом блока

9 управления, Меньшее приращение (МП) записывается в регистр 2 по входам, являющимся вторыми входами устройства. Вторые входы регистра 2 прира щения соединены с информационными выходами сумматора 6 приращения.

Вход записи регистра 2 координатного приращения соединен с вторым выходом блока 9 управления. Вход регистра 2 соединен с первыми и вторыми входами коммутатора 3, управляющий вход ко- торого соединен с первым выходом блока управления.

На первые входы коммутатора 3 подается значение, равное содержимому регистра 2 координатных приращений, а на вторые — удвоенное значение содержимого регистра 2. Последнее достигается монтажным соединением, для чего i-й выход регистра 2 координатных приращений соединяется с (i+1) входом коммутатора 3, а младший разряд коммутатора 3 заземляется.

Блок 7 сравнения обеспечивает сравнение модуля суммы, полученной в накопительном сумматоре 6, с содержимым второго регистра 2 координатных приращений, поступающих на входы блока 7 сравнения. При единичном значении знакового разряда, сумматора 6 и содержимом регистра 2 координатных приращений, большем модуля суммы, формируемой сумматором 6, на выходе блока 7 сравнения появляется уровень логической единицы, В противном случае — на выходе блока 7 сравнения формируется уровень логического нуля.

Триггер 27 устанавливается в состояние лог. единицы при БП = DY и в состояние лог. нуля при БП=ЬХ, Выходы 10-13 блока 9 управления являются выходами Х интерполятора, и выходы 14-17 — выходами Y.

Отсутствие перемещения по соответствующей координате эа время интерполяционного тока обозначено через О, а наличие — через 1, Уровень логической единицы на выходах

5 12987

10-17 блока 9 управления обозначает двойные комбинированные перемещения:

По координате Х По координате 7

10-00 14-00

11-01 I5-О1

12-10 16-10

13-11 17-11

Блок 9 управления, анализируя значение знакового разряда сумматора б и выхода блока 7 сравнения, задает 10 направление генерируемого двойного перемещения и характер следующей за ним арифметической операции по расчету очередного значения оценочной функции в соответствии с формулами: 15 при П;. > 0 — перемешивание 00 по оси 7 и

U .= U ° — 2 217 <2,j

У при U;. 0 и IUD,.1 - 1д71 -- переме- 20 щение 01 по оси 7 и — д + (a<<-д );

1 при U;„. < 0 и fU;,;1 >r 1ЛYI — лереме-! щение 1О по оси Y u 25

U. Е .,1 = U1- ---ДУ -(DX -ДУ) °

f+Z,,1+1 1,f

Перемещение по оси Х производится в каждом интерполяционном такте. .Интерполятор работает следующим 30 образом, Модули проекций, задающих отрезок прямой, записываются в регистр 1 (большее приращение БД) и регистр 2 (меньшее приращение МП), При этом в триггер 27 записывается логическая единица при LlX = БП и ноль при D Y=

=-БП „

По сигналу "Пуск" начинается процесс воспроизведения отрезка прямой. 10

Модули проекций через коммутаторы 3 и блоки совпадения 5 и 4 пода атся в сумматор 6 для проведения операции

БП-МП, В блоке 7 сравнения полученное значение БП-МП, хранящееся в накопительном сумматоре 6, сравнивается со значениями МП, При БП вЂ” ЫП 3 МП, что соответствует появлению логического пуля на выходе блока 7 сравнения, блок 9 управления на своем выхо- 50 де 18 формирует сигнал логического нуля, который не является активным сигналом записи в регистр 2. При

HM — IIII МП значение разности переэаписывается в регистр 2, Этому случаю со о тв е т с тв уе т фор миро в а. ние ло гических единиц на выходе блока 7 сравнения и выходе 18 блока 9 управления. условие БП вЂ” МП (МП при дХ = БП onl4 6 ределяет принадлежность генерируемого отрезка прямой к второй четверти первого квадранта„ Для обеспечения воспроизведения указанного вектора путем инверсии последовательности приращений по ведомой координате соответствующего Вектора в первой четверти квадранта необходимо, чтобы последний имел следующие значения модулей проекций: д Х = БП, дУ = БПМП, что и обеспечено на первом подготовительном такте работы интерполятора. При этом блок 9 управления должен обеспечить в дальнейшем инвертирование последовательности приращений по ведомой координате. На этом заканчивается подготовительный этап, предшествующий собственно процессу интерполяции. Причем сумматор

6 принимает значение содержимого регистра 1 после выполнения подготовительных операций, т.е. Up = БП. !

Поскольку эквивалентными трансформациями с учетом соответствующих признаков интерполяция сводится к генерации отрезков прямых в первой четверти первого квадранта, то процесс получения выходных последовательностей интерполятора по значениям входных приращений рассматривается только для указанной области, для которой дХ = БП, дУ = МП, 2д 1 д Х, В цикле интерполяции в первом такте в сумматоре 6 производится вычисление разности Uð — 2 ° дY что обеспечивается формированием логических единиц на выходах 19 и 20 блока

9 управления, а также подачей логической единицы на вход сумматора 6.

Блоком 7 сравнения проводится сопоставление полученного модуля оценочной функции, хранящегося в сумматоре 6, с модулем NII, хранящимся в регистре 2 координатных приращений.

Блок 9 управления в зависимости от значения знакового разряда сумматора

6, формируемого на его выходе, уровней сигналов„ поступающих с выхода блока 7 сравнения, и значения сигнала, поступающего с выхода триггера

27, формирует выходные сигналы, соответствующие двойным перемещениям по обоим направлениям. Б зависимости от значения знакового разряда сумматора 6 формируется новое значение оценочной функции, определяющей очередные двойные перемещения, При положительном значении модуля оценочной функции ее новое значение оп7 129 ределяется согласно выражению Ul+ =

=U. — 2дУ, а при отрицательном— согласно выражению U „= U. -dY+(aX-nY).

На фиг, 3 изображен отрезок аппроксимируемой прямой с дХ=7, BY=3.

Вычисление оценочной функции и формирование комбинированных двойных . перемещений производится следующим образом:

U = 7 — перемещение отсутствует, 2BY = 6, БП = ЛХ=7;

U = 7-6 = Π— перемещение 00 по ведомой координате (вых. 14, вых. 13);

Uã = 1-6. = -5, .l Ug l !У переме щение 10 по ведомой координате (вых. 16, вых. 13);

= -5-3 + (7-3) = -4, !Uql dY— перемещение !0 по ведомой координате (вых. 16, вых. 13);

U = -4-3 + (7-3) = -3, IU4

= dY — перемещение 10 по ведомой координате (вых ° 16, вых. 13).

Блок 9 управления может быть синтезирован различными известйыми методами.

В исходном состоянии регистры 29 и 30, а также триггер 30 обнулены.

По сигналу "Пуск" начинает работу генератор 32 импульсов. Для обеспечения принципа единой временной организации синхронизация регистров 23 и 31 осуществляется от различных фронтов. С каждым тактовым импульсом из узла 28 постоянной памяти обеспечивается выборка управляющего сигнала по адресу, хранящемуся в регистре

31 и определяемому входными сигналами 22,23,27 блока и состоянием триггера 30. Управляющее слово записыва° Э ется в регистр 29. Нулевой уровень сигнала "Пуск" определяет окончание процесса интерполяции и устанавливает в ноль триггер 30 и регистр 31.

Схема алгоритма функционирования блока 9 управления приведена на фиг. 4. Содержимое узла 28 постоянной памяти блока 9 управления, составленное в соответствии с алгоритмом функционирования, приведено в таблице. Таблица приведена только для случая ДХ > 0 У, где d . Х, йУ вЂ” проекции приращений аппроксимируемого отрезка соответственно на оси Х и Y.

Случаю г!Х ) ЛУ соответствует значение О в колонке, определяющей старший разряд адреса адресного прост8714 8 на 45 с максимальной точностью (погрешность аппроксимации равна О), в

50 то время как н известном устройстве этого достичь нельзя.

Формула и з о б р е т е н и я

5 !

О !

45 ранства ПЗУ, поскольку значение сигнала на входе 23 — нулевое, Случаю

ДУ йХ соответствует 1 н указанной колонке. Таблица, определяющая содержимое узла постоянной памяти для данного случая, совершенно аналогична приведенной, эа исключением разрядов, определяющих выходные сигналы, Значение указанных разрядов получают путем взаимной перестановки колонок Ql — С!4 и колонок Qs-QS в таблице, т ° е, обеспечивается взаимная перекоммутация выходных сигналов с координат X íà У, Накопительный сумматор 6 работает следующим образом, В каждый момент времени на информационный вход регистра 35 подается значение, равное сумме операндов, поступающих от блоков 4 и 5, а также с выхода регистра 35, При появлении переднего фронта на входе 24 сумматора значение суммы подается на выход регистра и при нулевом значении знакового разряда — на выход блока. При единичном значении знакового разряда блок 36 элементов ИСКЛЮЧАЮЩЕЕ.

ИЛИ обеспечивает инвертирование значения суммы, поступающей с выхода регистра 35, т ° е, обеспечивается выдача модуля суммы.

Погрешность аппроксимации не превышает шага дискретизации, Быстродействие приведенного линейного интерполятора превышает быстродействие известного устройства в 2 раза.

Это объясняется тем, что в последнем значение оценочной функции вычисляется только для одного единичного перемещения по обеим координатам. В предлагаемом линейном интерполяторе значение оценочной функции вычисляется сразу же для двойного перемещения по обеим координатам.

Кроме того> в нем достигается воспроизведение прямых с углом накло1. Линейный интерполятор, содержащий первый и второй регистры, первый и второй блоки совладения, выходы которых подключены к первому и второму входам сумматора соответственно, !

298714 выход первого регистра соединен с первым входом первого блока совпадения, вход первого регистра соединен с первым входом линейного интерполятора, второч вход которого подключен к первому входу второго регистра, .отличающийся тем, что, с целью повышения быстро" действия интерполятора, в него вве" дены блок управления, коммутатор и щ блок сравнения, выход которого подключен к первому входу блока управления, второй вход которого соединен с первым выходом сумматора и с первым входом блока сравнения, второй вход которого подключен к второму выходу сумматбра и к второму входу второго регистра, третий вход — к выходу второго регистра и к информационным входам коммутатора, управ- gg ляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к третьему входу второго регистра, третий выход - к первому входу второго блока сравнения, подключенного вторым входом к выходу коммутатора, четвертые выходь1 блока управления соединены с третьими входами сумматора, пятыи выход — с вторым входом первого бло- др ка совпадения, третий вход блока управления подключен к третьему входу линейного интерполятора, вход Пуск" которого соединен с входом "Пуск блока управления, пятые и шестые выходы KQTopoI О яВляются Выходами IIH нейного интерполятора. о

2.Интерпопятор по и. 1, о т л и— ч а ю шийся тем, что блок управления содержит генератор импульсов, первый и второй регистры, два триггера и узел постоянной памяти, первые выходы которого подключены к первым входам первого регистра, выходы которого являются пятыми и шестыми выходами блока управления, вторые выходы узла постоянной памяти соединены с информационными входами второго регистра, управляющий вход которого соединен с инверсным выходом генератора импульсов, прямой выход которого подключен к управляющему входу первого регистра, а вход— к входу "Пуск" линейного интерполятора и к установочным входам первого триггера и второго регистра, первый, второй, третий и четвертый выходы которого подключены к соответствующим первым входам узла постоянной памяти, второй вход которого соединен с выходом первого триггера, третий и четвертый входы — соответственно с первым и вторым входами блока управления, пятый вход узла постоянной памяти соединен с выходом второго триггера, вход которого является третьим входом блока управления, вторые выходы первого регистра подключены к соответствующим выходам блока управления, второй выход узла постоянной памяти соединен с управляющим входом первого триггера, D-вход которого соединен с третьим входом узла постоянной памяти.

1298714

ev !

О

1!! ! ае! ХХ

А ol x

v в!! 46 х а .,Х О

-о и

Ф 1 -еч

--5, oc9 vs

v 4ч

1 О

Ф ° ° D4

° В ° 1 {4

М М v !

Ю о v

° ° \1! о о о о о о о о о о о о о о о о о о, о о о о ь о

О о о, о о о о о о о о о о о о о о о о о о о о о о о о о о о

lo о о î î о о о е! ам з с у х вэ !а

e !! ь а О а и а5 мо

v ц

5 !"- ба и с! en! о о о о о

Ф Х 6Х!

О

04

--5, -ь vw

М О

° °

- ..%

М М v !! а

Э О !!

Х О

° ) Щ

3" k и 5w!

2987 I4!

4 х м

Д IC

<й м В о а

Ф 11

И 1 ° ° СЧ О

К 1 и м

0, и о

1 о о

О о о о о о о о о о о о о о о о о

I C э о о х х и же

I о к5

0 а о о о о о о о о о о о о о о о о о о о о о о о о о о о о о o a о о о о о о о о о о

Э

5 $

1 1В о о о о о о О О о о о

С7 о v+

II о и р, Г4

w o

1 298714

1 2 3 Ч 5 6

Ч

О 2

Фиг. 3

1298714

1 298714

12987! 4

Рлока 7

Фиг. 6

Составитель И. Швец

Редактор Н. Егорова Техред: А.Кравчук Корректор Л, Пилипенко

Заказ 2246 Тираж 863 Подписное

В11ИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул„ Проектная, 4