Устройство сбора дефектоскопической информации

Иллюстрации

Показать всеРеферат

Изобретение относится к средствам сбора и обработки дефектоскопической информации в установках неразрушающего контроля и может быть непользовано для автоматической ультразвуковой дефектоскопии протяженных изделий. Цель изобретения - повышение точности контроля. Устройство позволяет повысить производительность , сохраняя высокий уровень достоверности контроля при использова S 20 II сриг1 НИИ вычислительной системы автоматического вычисления координат, типов и параметров дефектов. Устройство освобождает процессор вычислительной системы от функции ввода дефектоскопических данных, осуществляя быструю загрузку дефектоскопической информации в один из двух блоков памяти, в то время как второй блок памяти подключен к шинам адреса, данных и управления процессора вычислительной системы, который ведет обработку дефектоскопических данных, ранее накопленных в соответствующем блоке памяти . Устройство содержит измерительный блок 1, первый 2 и второй 3 счетчики импульсов, первый 4 и второй 5 j регистры, первый 6 и второй 7 блоки. памяти, первый 8 и второй 9 коммутаторы , первый 10 демультиштексор, первый элемент ИЛИ 11, распределитель импульсов 12, третий 13 счетчик импульсов , мультиплексор 14, второй 15 демультиплексор, четвертый 16 счетчик импульсов, второй элемент ИЛИ 17, счетный триггер 18. 5 ил. .. сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (51)4 G 05 В 23 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3964218/24-24 (22) 09.10.85 (46) 23.03.87. Бюл. Ф (71) Курский политехнический институт (72) С.А.Якиревич, В.Э.Дрейзин, С.А.Филист и В.А.Кудинов (53) 621.396(088.8) (56) Залесский В.В. и др. Система . цифровой регистрации результатов ультразвуковой дефектоскопии. — "Дефектоскопия", 1977, Ф 3, с. 125.

Авторское свидетельство СССР

В 926593, кл . G 01 Ы 29/04, 1982 ° (54) УСТРОЙСТВО СБОРА ДЕФЕКТОСКОПИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение относится к средствам сбора и обработки дефектоскопической информации в установках неразрушающего контроля и может быть использовано для автоматической ультразвуковой дефектоскопии протяженных изделий. Цель изобретения — повышение точности контроля. Устройство позволяет повысить производительность, сохраняя высокий уровень достоверности контроля при использовании вычислительной системы автоматического вычисления координат, типов и параметров дефектов. Устройство освобождает процессор вычислительной системы от функции ввода дефектоскопических данных, осуществляя быструю загрузку дефектоскопической информации в один из двух блоков памяти, в то время как второй блок памяти подключен к шинам адреса, данных и управления процессора вычислительной системы, который ведет обработку дефектоскопнческих данных, ранее накопленных в соответствующем блоке памяти. Устройство содержит измерительный блок 1, первый 2 и второй 3 счет-. д чики импульсов, первый 4 и второй 5 регистры, первый 6 и второй 7 блоки памяти, первый 8 и второй 9 коммутаторы, первый 10 демультиплексор, пер- С, вый элемент ИЛИ 11, распределитель импульсов 12, третий 13 счетчик импульсов, мультиплексор 14, второй 15 демультиплексор, четвертый 16 счетчик импульсов, второй элемент ИЛИ 17, 1 счетный триггер 18. 5 ил. х=x — 1

1 х. (i = 2,3,...М)

Если амплитуда эхо-импульса превышает значение U„, то компаратор 28 устанавливает RS-триггер 30 в "единичное состояние. В этом состоянии

55 триггер 30 разрешает прохождение сигнала через элемент И 31 Синхронизатор многоканального дефектоскопа с определенной задержкой по отношению к зондирующему сигналу вырабатывает

1 12987

Изобретение относится к неразрушающему контролю и может быть исполь— зовано в сканирующих системах ультразвуковой дефектоскопии, содержащих вычислительное устройство для определения типов, размеров и. координат дефектов.

Цель изобретения — повышение точ.,ности контроля.

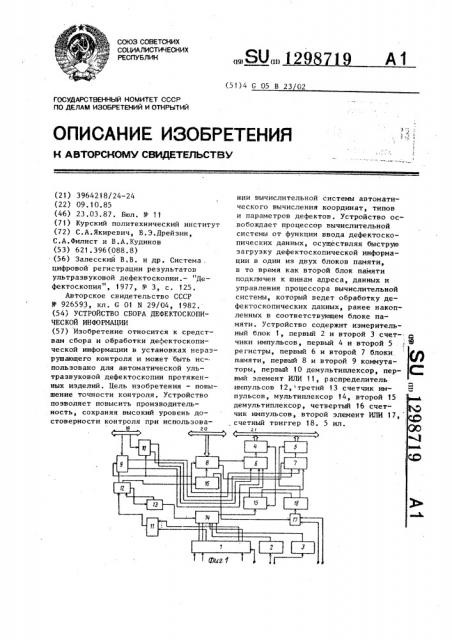

На фиг.1 представлена блок-схема устройства, на фиг.2 — схема распределителя импульсов, на фиг.3 — схема измерительного блока, на фиг. 4 — схема коммутатора для одного разряда; 15 на фиг.5 — схема демультиплексора для одного разряда.

Устройство (фиг.1) содержит измерительный блок 1, первый счетчик 2 импульсов (счетчик продольной координаты), второй счетчик 3 импульсов (счетчик поперечной координаты), первый регистр 4 (трехстабильный буфер данных), второй регистр 5 (трехстабильный буфер данных), первый 6 и второй 7 блоки памяти, первый коммутатор 8 (коммутатор адреса), второй коммутатор 9 (коммутатор записи), первый демультиплексор,i 0, первый 30 элемент ИЛИ 11, распределитель 12 импульсов, третий счетчик 13 импульсов, мультиплексор 14, второй демультиплексор 15, четвертый счетчик 16 импульсов (счетчик адреса), второй элемент ИЛИ 17, счетный триггер 18, шину

19 управления, шину 20 адреса, информационную шину 21.

Распределитель 12 импульсов (фиг.2) содержит мультивибратор 22, элемент И 23, счетчик 24 импульсов, дешифратор 25, RS-триггер 26.

Измерительный блок 1 (фиг,3) содер* т измерительные кан 27! 27н каждый иэ которых состоит из компара- 45 тора 28, источника 29 порогового напряжения, RS-триггера 30„ элемента

И 31, аналого-цифрового преобразователя 32, регистра 33 и пикового детектора 34.

Коммутаторы 8 и 9 (фиг.4) содержат в каждом разряде два первых элемента ИЛИ 35, и 35 д, четыре элемента

И 36 и 36, 36, и 36 и два вторых элемента ИЛИ 37„ и 37 .

Демультиплексоры IO и 15 (фиг.5) содержат в каждом разряде элемент

ИЛИ 38 первый 39 и второй 40 элементы И.

19 2

Устройство сбора дефектоскопичес,— кой информации работает следующим образом, Первичные преобразователи сканирующего устройства (не показаны) движутся вдоль поверхности контролируемого изделия. Счетчики 2 продольной и 3 поперечной координат фиксируют с дискретностью аХ продольную координату и с дискретностью 3Y — поперечную координату первичного преобразователя первого канала. Первичные преобразователи остальных каналов расположены на известном расстоянии (по двум координатам) от первого первичного преобразователя: 1 1 хр где i = 2,3,..., М вЂ” номер канала.

Если (Х„, У,) координаты первого первичного преобразователя, то координаты других преобразователей могут быть легко получены по формулам

У вЂ” У„ l„, Синхронизатор многоканального дефектоскопа вырабатывает с определенной частотой зондирующие сигналы, поступающие на первичные преобразователи, которые преобразуют их в ультразвуковые импульсы, поступающие через имерсионную среду в контролируемое иэделие. При наличии дефекта первичный преобразователь принимает отраженный эхо-сигнал и на соответствующем выходе многоканального дефектоскопа формируется эхоимпульс. По мере приближения к дефекту будет выработана пачка зондирующих сигналов и соответственно получена пачка эхо-импульсов. Таким образом, на входы измерительного блока 1 поступают пачки эхо-импульсов с частотой, равной частоте зондирования. Амплитуда поступившего эхоимпульса запоминается пиковым детектором 34 и параллельно сравнивается компаратором 28 с пороговым значением U„.

3 12987 синхро-импульс, сигнализирующий о поступлении эхо-импульса. Синхро-им- пульс поступает на синхро-вход измерительного 1 блока и через элемент

И 31 включает аналого-цифровой преоб5 разователь (АЦП) 32 и обнуляет регистр 33. АЦП 32 преобразует в цифровой код значение амплитуды эхо-импульса, запомненное на пиковом детекторе 34. По окончании преобразования 1р

АЦП 32 вырабатывает импульс "Конец преобразования", по которому происходит запись цифрового кода амплитуды эхо-импульса в регистр 33, осуществляется обнуление пикового детектора

34 и установка триггера 30 в "нулевое состояние. Импульс Конец преобразования" является сигналом "Конец измерения", выдаваемьм измерительным блоком 1 ° Если эхо-импульс по какому-20 либо каналу отсутствует или его значение меньше величины U„ то триггер 30 остается в "нулевом" состоянии и синхроимпульс не проходит на

АЦП 32. В результате АЦП 32 не рабо- 25 тает, а в регистре 33 устанавливается нулевой код. Итак, после появления синхрою пульса и окончания преобразования АЦП 32 на выходных регистрах

33 находится или цифровой код амплитуды эхо-импульса, поступившего с данного канала, или нулевой код.

Ввод данных с выходных регистров

33 измерительного блока 1 и счетчиков

2 и 3 в блоки 6 и 7 памяти происходит 35 следующим образом.

Состояние счетного триггера 18 задает определенную коммутацию входов и выходов блоков 4, 5, 8, 9, 10, 15.

Примем для определенности, что счет- 40 ный триггер 18 находится в "нулевом" состоянии. В этом случае выход блока

6 памяти через регистр 4 (трехстабильный буфер данных) подключен к шине данных вычислительной системы (буфер 4 открыт). Первый выход демультиплексора 15 заблокирован и вы дает на вход блока 6 памяти нулевой код. Коммутатор 8 подключает шину 20 адреса вычислительной системы к ад-г ресному входу блока 6 памяти, а коммутатор 9 подает выход "Запись" с шины 19 управления вычислительной системы на вход "Запись" блока 6 памяти.

Первый выход демультиплексора 10 под-55 ключает выход "Чтение" шины 19 управления вычислительной системы на вход

"Чтение" блока 6 памяти. В свою очередь, выход блока 7 памяти отключен

19 4 регистром 5 (трехстабильным буфером данных) от информационной шины 21 вычислительной системы (выход буфера

5 находится в высокоимпедансном состоянии). Второй выход демультиплексора 15 подключает выход мультиплексора

14 на вход блока 7 памяти. Коммутатор 8 адреса подключает выход счетчика !6 к адресному входу блока 7 памяти, а с коммутатора 9 подает второй выход распределителя 12 на вход "Запись" блока 7 памяти. Второй выход демультиплексора 10 заблокирован и выдает нулевой потенциал на вход

"Чтение" блока 7 памяти.

Описание коммутации показывает, что "нулевое" состояние счетного триггера !8 позволяет вычислительной системе вести обмен информацией с блока 6 памяти, в то время как информация с измерительного блока 1 записывается в блок 7 памяти. Рассмотрим этот процесс более подробно.

Если хотя бы по одному каналу сработало АЦП 32 измерительного блока

1, то импульс Конец измерения" через первый элемент ИЛИ 11 поступает на вход запуска распределителя 12 импульсов. В результате триггер 26 устанавливается в единичное состояние .и разрешает прохождение тактовых импульсов с мультивибратора 21 через элемент И 23 на вход счетчика 24.

Счетчик 24 имеет четыре состояния:

"нулевое — исходное состояние, состояние "1", по которому происходит наращивание счетчика 13, состояние

"2", по которому на блок 7 памяти чеоез коммутатор 9 подается сигнал

"Запись, состояние 3, по которому происходит наращивание счетчика 16.

Счетчик 24, получая тактируемые импульсы, последовательно проходит все эти состояния, дешифратор дешифрирует их и на его выходах появляется последовательность импульсов.

Первый импульс изменяет на единицу состояние счетчика 13, который управляет мультиплексором 14. Каждое состояние счетчика 13 переключает определенный вход мультиплексора 14 на выход. В результате информация с измерительного блока 1 или счетчиков

2 и 3 через мультиплексор 14 и демультиплексор 15 поступает на вход блрка 7 памяти. Второй импульс с распределителя 12 импульсов является сигналом "Запись" для блока 7 памяти.

1) -1

D - 2

D †.3 з продольная координата; поперечная координата; код амплитуды эхо-импульса или нулевой код (1 канал); код амплитуды эхо-импульса или нулевой код (2 канал), D — 4

D -N+ 2 — код амплитуды эхо-импуль- 40

К+ са или нулевой код (N канал) .

Отмети%,.что наличие нулевого кода говорит о том, что данный канал не получил эхо-импульса. 45

Информация вводится в блок 7 паг мяти указанными Массивами до тех нор, пока не произойдет переполнение счетчика 16. В этом случае счетчик 16 переходит в исходное состояние и выдает сигнал переполнения, который через второй элемент ИЛИ 17 изменяет состояние счетного триггера 18. Счетный триггер, находясь в "единичном" состоянии, осуществляет перекоммутацию входов и выходов блоков 4, 5,, 8, 9, 10 и 15 таким образом, что теперь уже блок 7 памяти связан с информационной шиной 21 шиной 20 адреса и

5 12987

Содержимое счетчика 16 адреса через коммутатор 8 подключено к адресному входу блока 7 памяти. По адресу, хранимому в счетчике 16 происходит запись информации, поступившей на вход блока 7 памяти. Третий импульс с распределителя 12 импульсов увеличивает содержимое счетчика 16 на единицу, тем самым подготавливая следующий адрес записи. Счетчик 24 возвращается f0 в "нулевое" состояние. Цикл записи окончен. Число циклов записи подсчитывается счетчиком 13 и равно N+2, где N — число каналов в измерительном блоке 1. В первом и втором цикле за- 15 писи происходит ввод в блок 7 памяти содержимого счетчиков 2 и 3. Далее в каждом следующем цикле осуществляется ввод информации с очередного выходного регистра 33 измерительного 20 блока 1.

Таким образом, если по поступлении синхроимпульса от многоканального дефектоскопа сработало хотя бы одно

АЦП 32 измерительного блока 1, то в .5 запоминающее устройство будет записан следующий массив D:

19 6 шиной 19 управления вычислительной системы, а блок б памяти подключен через соответствующие блоки к измерительному блоку 1, счетчику 16, счетчикам 2 и 3, распределителю 12 импульсов. Описанный процесс ввода данных будет теперь осуществляться в блок б памяти.

В то время, как дефектоскопическая информация вводится в блок 6 памяти, вычислительная система считывает накопленные данные из блока 7 памяти и обрабатывает их. При этом процесс ввода и считывания дефектоскопических данных может протекать параллельно, так как входы, выходы и управляющие сигналы обоих блоков 6 и 7 памяти; развязаны блоками 4, 5, 8, 9, 10 и

15. Рассмотрим процесс считывания данных из блоков б и 7 памяти вычислительной системой. Примем для определенности, что считывание происходит из блока 7 памяти, т.е. счетный триггер 18 находится в "единичном" состоянии, Адрес ячейки блока 7 памяти с шины 20 адреса через коммутатор 8 поступает на адресный вход блока 7 памяти. Сигнал "Чтение" с шины 19 управления очерез второй выход демультиплексора 10 поступает на вход "Чтение" блока 7 памяти, при этом первый выход демультиплексора 10 выдает нулевой потенциал на вход "Чтение" блока б памяти. В результате с выхода блока 7 памяти информация через открытый регистр 5 поступает на шину данных и фиксируется процессором вычислительной системы, при этом регистр 4 находится в высокоимпедансном состоянии и отключает выход блока 6 памяти от информационной шины 2 данных. Прочитав информацию из ячейки блока 7 памяти, процессор вычислительной системы обнуляет эту ячейку.

При этом сигнал "Запись" с шины 19 управления через коммутатор 9 поступает на вход "Запись" блока 7 памяти.

Происходит запись нулевого кода со второго выхода демультиплексора 15, который заблокирован при данном состоянии счетного триггера 18 (фиг.5) .

Таким образом, после считывания всей информации из запоминающего устройства оно ока.зывается обнуленным. Это обстоятельство и структура записываемых массивов D позволяет процессору вычислительной системы легко различать записанную в запоминающем уст7 2987 ройстве информацию. Процессор начинает считывать информацию с нулевой ячейки.

Если содержимое первой ячейки не равно нулю, то это продольная координата, следующая ячейка содержит поперечную координату. Следующие N ячеек содержат информацию о кодах амплитуд эхо-сигналов, поступивших с каждого из каналов. Порядковый номер 10 ячейки, отсчитываемый от ячейки, содержащей поперечную координату, указывает на номер канала. Если содержимое каких-либо из этих ячеек равно нулю, то это означает, что данные каналы не получили эхо-импульсов."

Следующие N+2 ячейки запоминающего устройства содержат новый массив Р и так далее. Считывание производится или до конечного адреса блока памяти,20 или до тех пор, пока первая ячейка очередного массива не окажется равной нулю. Это означает, что процессор сосчитал и обработал всю дефектоскопическую информацию в данном блоке памяти.

Переключение блоков 6 и 7 памяти от шин вычислительной систещл к измерительному блоку 1 и счетчикам 2 и 3 осуществляется счетным триггером

18 по сигналам переполнения счетчика

16 (этот случай описан выше), сигналу "Начало контроля" и сигналу "Конец контроля". При включении счетный триггер 18 может оказаться в произ- 3 вольном состоянии и подключить к шинам вычислительной системы блок 6 памяти или блок 7 памяти. Допустим, что произошло подключение блока 6 памяти к шинам вычислительной системы. 40

Процессор вычислительной системы при включении обнуляет этот блок памяти.

Сигнал иНачало контроля" через второй элемент ИЛИ 17 перебрасывает счетный триггер 18 в другое состоя- 45 ние, в результате чего к шинам вычислительной системы оказывается подключенным блок 7 памяти в то время, как обнуленный блок 6 памяти подсоединен к измерительному блоку 1 и счетчикам 50

2 и 3 и готов принимать дефектоскопическую информацию.

Процессор вычислительной системы по сигналу "Начало контроля" обнуляет 55 другой блок памяти (в данном случае блок 7 памяти) и начинает опрашивать его первую ячейку . Так как блок 7 па- мяти только что был обнулен, процес-

19 8 сор будет считывать из первой ячейки нулевой код, сигнализирующий ему, что информация для обработки пока не поступила. Как только заполнится блок 6 памяти, т.е. произойдет переполнение счетчика 16 адреса, этот блок памяти окажется подключенным к шинам вычислительной системы, а обнуленный блок

7 памяти — к измерительному блоку 1 и счетчикам 2 и 3. Процессор вычислительной системы в очередной раз обратится к первой ячейке запоминающего устройства, на этот раз это будет . первая ячейка блока 6 памяти, содержащая ненулевую продольную координату.

Считанный ненулевой код сигнализирует процессору о том, что поступила для обработки дефектоскопическая информация. Процессор начинает обработку поступивших данных, образующих как уже описано, массивы D. Программа обработки может включать определение типов, координат и размеров дефектов.

Пока происходит обработка данных из блока 6 памяти, в обнуленный блок 7 памяти поступает информация из измерительного блока 1 и счетчиков 2 и 3.

При этом для процессора вычислительной системы по адресам блоки 6 и 7 памяти не отличимы друг от друга.

Окончив обработку дефектоскопических данных и обнулив по ходу этой обработки блок памяти (в данном случае блок 6 памяти), процессор переходит на опрос первой его ячейки и будет считывать оттуда нули пока не произойдет переключение блоков памяти, т.е. в данном случае, пока не будет подключен к шинам системы блок 7 памяти. Описанный процесс будет продолжаться до поступления сигнала нКонец контроля". По этому сигналу происходит очередное переключение блоков 6 и 7 памяти. В результате частично заполненный дефектоскопической информацией блок памяти подключается к шинам вычислительной системы, процессор обрабатывает эти данные и останавливается.

Объемы блоков 6 и 7 памяти должны быть определены, исходя из условия практически полного исключения потерь дефектоскопических данных (т.е. вероятность потери дефектоскопических сигналов должна быть довольно низ-5 -.-7 кой — 10 — 10 ) . Реально это означает, что время обработки дефекто9

12987 скопических данных, хранящихся в блоке 7 памяти объемом M байт, практически всегда должно быть меньше времени накопления дефектоскопических данных в блоке памяти того же объема. В общем случае объем блока памяти зависит от числа каналов, статистических характеристик интервалов

-поступления дефектоскопических сигналов по каждому каналу и времени 10 обработки этих сигналов.

Предлагаемое устройство не требует от процессора вычислительной системы затрат времени на ввод кодов амплитуд эхо-импульсов и их координат, процессор при использовании данного устройства занят только обработкой дефектоскопических данных.

Повышение достоверности контроля за счет увеличения числа каналов, при- 20 менения вычислительных систем, ведущих всесторонний учет и обработку всей дефектоскопической информации, существенно снижают производительность контроля. Устройство позволяет осуществлять быструю загрузку дефектоскопических данных, не отвлекая на эту процедуру вычислительные средства системы, что позволяет достичь высокой производительности контроля при -З0 заданном уровне достоверности контроля. формула изобретения

Устройство сбора дефектоскопичес- 35 кой информации, содержащее первый блок памяти, измерительный блок, подключенный информационными входами к информационным входам устройства, а синхровходом — к первому синхровхо- 40 ду устройства, а также первый и вто- рой счетчики импульсов, связанные счетными входами соответственно с вторым и третьим синхронизирующими входами устройства, о т л и ч а ю — 45 щ е е с я тем, что, с целью повышения точности контроля, введены два регистра, второй блок памяти, мультиплексор, два демультиплексора, счетный триггер, два элемента ИЛИ, 50 третий и четвертый счетчики импульсов, два коммутатора и распределитель импульсов, соединенный входом

"Пуск с выходом первого элемента

ИЛИ, входом "Останов" — с первым вы- 55

19 ходом третьего счетчика импульсов, первым выходом — с счетным входом третьего счетчика импульсов, вторым выходом — с первым управляющим входом второго коммутатора, а третьим выходом — с счетным входом четвертого счетчика импульсов, подключенного первым информационным выходом к первому информационному вход первого коммутатора, а вторым информационным выходом — к первому выходу второго элемента ИЛИ, связанного вторым и третьим входами соответственно с входами "Начало контроля" и "Конец контроля устройства, а выходом — с входом счетного триггера, соединенного инверсным выходом с управляющим входом второго регистра, а прямым выходом — с управляющими входами первого и второго демультиплексора, с вторым управляющим входом второго коммутатора, с управляющим входом первого регистра и с вторым управляющим входом первого коммутатора, связанного вторым информационным входом с шиной адреса устройства, а первым и вторым выходами — соответственно с адресными входами первого и второго блоков памяти, подключенных выходами соответственно к информационным входам первого и второго регистров, соединенных выходами с информационной шиной устройства, связанного управляющей шиной с информационным входом второго коммутатора и с информационным входом первого демультиплексора, поцключенного первым и вторым выходами к входам Чтение" соответственно первого и второго блоков памяти, связанных входами "Запись" соответственно с первым и вторым выходами второго коммутатора, а информационными входами — соответственно с первым и вторым выходами второго демультиплексора, подключенного информационным входом к выходу мультиплексора, связанного управляющим входом с выходом третьего счетчика, а соответствующими информационными входами— с выходом первого счетчика импульсов, с выходом второго счетчика импульсов и с информационными выходами блока измерения, связанного выходами "Конец измерения" с соответствующими входами первого элемента ИЛИ.

Выход!

" Конец измеое.-, Ин рормационнь!й сия" 6ь од!

ВыходN

"Конец амере — Ьтод И

ИтРо ьш.циоииый диод !

Синхра5яод

ФиаЗ

ЮЮРиациоиный длод И

129871 9 и.а

Составитель Н.Горбунова

Техред М.Ходанич Корректор Е,Рошко

Редактор Н.Егорова

Заказ 888/50

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Тираж 8б4 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

i13035, Москва, Ж-35, Раушская наб., д. 4/5

Ь Фи