Устройство для обнаружения состязаний в синхронизируемых дискретных блоках

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков. Цель изобретения - повышение достоверности обнаружения состязаний. Устройство содержит два формирователя импульсов , которые формируют импульсы по каждому перепаду , Входного напряжения. На вход первого формирователя импульсов поступают импульсы синхронизации контролируемого блока. Сигналы с выхода первого формирователя импульсов поступают через элемент задержки на установочный вход счетчика, на счетный вход которого поступают сигналы с выхода второго формирователя импульсов , вход которого соединен с выходом контролируемого блока. Если в контролируемом блоке отсутствует состязания, то в интервале между началом и концом сигнала синхронизации на счетный вход счетчика поступает один импульс (если выходная информация изменится) или не поступит ни одного импульса (если выходная информация не изменилась). В этом случае все разряды .счетчика, кроме нулевого (младшего), находятся в нулевом состоянии. Поэтому на выходе элемента ИЛИ, входы которого соединены с выходами этих разрядов, будет нулевой сигнал. Этот сигнал поступает на информационный вход коммутатора, на двух выходах которого будут нулевые сигналы, независимо от состояния младшего разряда счетчика, выход которого соединен с управляющим кодом коммутатора. Таким образом, сигнал с выхода первого формирователя импульсов, переписывая на первьш и второй триггеры состояние вьгходов коммутатора, оставит их в нулевом состоянии. При наличии состязаний в контролируемом блоке на его выходе в интервале между началом и концом синхроимпульса появится несколько перепадов напряжения, в результате чего на счетный вход счетчика поступит несколько перепадов напряжения, в результате чего на счетный вход счетчика поступит несколько импуль- .сов. При статических состязаниях количество импульсов будет четным, при динамических - нечетным. В этом случае сигнал с выхода элемента ИЛИ пройдет на первый или второй выходы коммутатора в зависимости от состояния нулевого разряда счетчика (четности импульсов). Сигнал с выхода первого формирователя импульсов установит в единичное состояние соответствующий триггер, указывая, какой вид состязаний обнаружен в контролируемом блоке. 3 ил. Q

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

О А1 (19) (И) (51) 4 G 06 F 11/00

3Щ;Щ,» (у ,,)3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2.1) 3986888/24-24 (22) 08. 10.85 (46) 23.03.87. Бюл. ¹ 11 (72) В.Н. Куценко, А,М. Кузьменко, Е.В. Ананский, С.В. Корнеев и С.И. Богородченко (53) .681.3 (088.8) (56) Авторское свидетельство СССР № 601696, кл. G 06 Р 11/00, 1976.

Авторское свице тельство СССР № 1125628, кл. G 06 F 11/16, 1983. (54) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СОСТЯЗАНИЙ В СИНХРОНИЗИРУЕМЫХ ДИСКРЕТНЫХ БЛОКАХ (57) Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков. Цель изобретения — повышение достоверности обнаружения состязаний. Устройство содержит два формирователя импульсов, которые формируют импульсы по каждому перепаду Ъходного напряжения.

На вход первого формирователя импульсов поступают импульсы синхронизации контролируемого блока. Сигналы с выхода первого формирователя импульсов поступают через элемент задержки на установочный вход счетчика, на счетный вход которого поступают сигналы с выхода второго формирователя импульсов, вход которого соединен с выходом контролируемого блока. Если в контролируемом блоке отсутствует состязания, то в интервале между началом и концом сигнала синхронизации на счетный вход счетчика поступает один импульс (если выходная информация изменится) или не поступит ни одного импульса (если выходная информация не изменилась). В этом слу— чае все разряды .счетчика, кроме ну— левого (младшего), находятся в нулевом состоянии. Поэтому на выходе элемента HJIH, входы которого соединены с выходами этих разрядов, будет нулевой сигнал. Этот сигнал поступает на информационный вход коммутатора, на двух выходах которого будут нулевые сигналы, независимо от состояния младшего разряда счетчика, выход которого соединен с управляющим кодом коммутатора. Таким образом, сигнал с выхода первого формирователя импульсов, переписывая на первый и второй триггеры состояние выходов коммутатора, оставит их в нулевом состоянии. При наличии состязаний в контролируемом блоке на его выходе в интервале между началом и концом синхроимпульса появится несколько перепадов напряжения, в результате чего на счетный вход счетчика поступит несколько перепадов напряжения, в результате чего на счетный вход счетчика поступит несколько импуль.сов. При статических состязаниях количество импульсов будет четным, при с динамических — нечетным. В этом случае сигнал с выхода элемента ИЛИ пройдет на первый или второй выходы коммутатора в зависимости от состояния нулевого разряда счетчика (четности импульсов). Сигнал с выхода первого формирователя импульсов установит в единичное состояние соответствующий триггер, указывая, какой вид состязаний обнаружен в контролируемом блоке. 3 ил.

1298750 2

Изобретение относится к вычислительной и контрольно-измерительной технике и может быть использовано в автоматизированных комплексах проверки логических блоков.

Цель изобретения — повышение достоверности обнаружения состязаний.

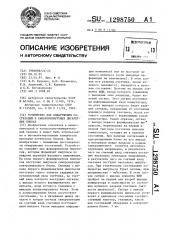

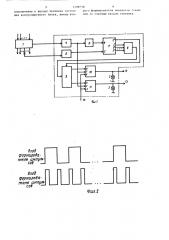

На фиг. 1 приведена функциональная схема устройства; на фиг.2 — временная диаграмма работы формирователей импульсов; на фиг.3 — временная диаграмма динамического и статического состязаний.

Схема содержит контролируемый блок

1 и устройство для обнаружения состязаний в синхронизируемых дискретных блоках, содержащее элементы 2 и 3 инпикации, формирователи 4 и 5 импульсов, элемент 6 задержки, счетчик

7, элемент ИЛИ 8, коммутатор 9, триггер 10 и 11, выходы 12 и 13 статических и динамических состязаний устройства, установочный вход 14 устройства.

Устройство обнаруживает два вида состязаний — статическое и динами— ческое.

Устройство работает следующим образом.

В начале работы по установочному входу 14 устройства устанавливаются в исходное .состояние триггеры 10 и

11. На их единичных выходах устанавливаются нулевые сигналы, тем самым снимаются сигналы наличия состязания с элементом 12 и 13 индикации.

Если в контролируемом блоке отсутствуют состязания, то устройство работает следующим образом.

Синхроимпульсы поступают на контролируемый блок 1 и íà axîä первого формирователя 4 импульсов. В зависимости от логической комбинации, присутствующей на входах контролируемого блока 1, после действия фронта (заднего или переднего) синхроимпульсов на его выходе, соединенном с входом второго формирователя 5 импульсов уста»»авливается сигнал или " 1", или

fl 0tt

Первый формирователь 4 импульсов формирует импульсы при переключении входа с "0" в "1" и наоборот. Временная дна грамма синхр оимпуль сов и импульсов, формируемых формирователем

4 импульсов, приведена на фиг.2.

Импульсы с выхода формирователя

4 импульсов поступают через элемент

6 задержки на установочный вход счетчика 7, сбрасывая его в нулевое состояние.

Сигналы с выхода контролируемого блока 1 поступают на вход второго формирователя 5 импульсов, который работает аналогично формирователю 4.

Таким образом, на счетнья» вход счетчика 7 с выхода эдновибратора формирователя 5 импульсов поступают импульсы, соответствующие переходам из

"0" в "1" и наоборот на выходе контролируемого блока 1. Счетчик 7 осуществляет подсчет импульсов, поступающих на его счетный вход в пределах интервала времени между импульсами, формируемыми формирователем 4 импульсов.

В соответствии с изложенным, при отсутствии состязаний в контролируемом блоке 1, в интервале между двумя импульсами с выхЪда формирователя 4 импульсов на счетный вход счетчика

7 с выхода формирователя 5 импульсов поступает не более одного импульса и на входы элемента ИЛИ 8 с выходов

2, 2, ..., 2" счетчика 7 поступают сигналы низкого логического уровня, при этом на выходе элемента ИЛИ

8 также присутствует сигнал ниэкогo логического уровня, который поступает на информационный вход коммутатора 9. При наличии на информационном входе коммутатора 9 сигнала низкого логического уровня, независимо от сигнала на его управляющем входе с выхода 2 (младшего разряда) счетчик

7, на выходах коммутатора 9 также присутствуют сигналы низкого логического уровня.

Сигналы низкого логического уровня с выходов коммутатора поступают на информационные входы триггера 10

40 и 11. B этом случае при поступлении пульсов, триггеры 10 и 11 сохранят нулевое состояним

При возникновении в контролируемом блоке 1 состязаний в соответствии с приведенными определениями формирователь 5 импульсов формирует последовательности импульсов (n > 1), количество которых в интервале вре-: мени между импульсами, сформированными формирователем 4 импульсов (зтот интервал времени равен длительности импульса синхронизации или паузе

45 на тактовые входы триггеров 10 и 11 импульса с выхода формирователя 4 им1298

3 между ними), будет либо четным, что соответствует статическим состязаниям, либо нечетным — в случае динамических состязаний, но в обоих случа( ях на выходах счетчика 7 от 2 до

2" присутствует логическая комбинация, содержащая хотя бы одну логическую единицу, которая через элемент ИЛИ 8 поступает на информационный вход коммутатора 9. 10

При возникновении статических состязаний на управляющий вход коммуо татора 9 с выхода 2 (младшего разряда) счетчика 7 поступает сигнал низкого логического уровня вслед-,, 15 ствие того, что на счетный вход счетчика 7 с выхода поступило четное количество импульсов, а начальное со— стояние счетчика быпо нулевое.

В случае, когда на управляющем 20 входе коммутатора 9 присутствует сигнал низкого логического уровня, логическая единица с его информационного входа через первый информационный выход поступает на информационный вход триггера 10. При этом импульс с выхода формирователя 4 им— пульсов, поступая на информационный вход триггера 10, приводит к переключению триггера 10 в единичное состо- 30 яние и через время задержки, определяемое элементом 6 задержки, сбрасывает счетчик 7 в нулевое состояние.

Требуемая величина элемента 6 задержки определяется максимальной за- 35 держкой в счетчик 7, элементе ИЛИ 8 и максимальным временем переключения триггеров 10 и 11.

При поступлении с выхода триггера

10 сигнала высокого логического уров- 40 ня срабатывает элемент 2 индикации, сигнализируя о статическом состязании в контролируемом блоке.

При возникновении динамических состязаний на управляющий вход комму- 45 татора 9 с выхода 2 счетчика 7 поступает сигнал высокого логического уровня. При этом логическая единица с информационного входа коммутатора 9 через второй его информационный выход50 поступает на информационный вход триггера 11. Импульс с выхода формирователя 4 импульсов поступает на тактовый вход триггера 11, приводит к его переключению в единичное состояние. 55

При поступлении с выхода триггера

11 сигнала высокого логического уров-, ня срабатывает элемент 3 индикации, 750 сигнализируя о динамическом состязании в контролируемом блоке.

С выхода 12 и 13 устройства сигналы обнаружения статических и динамических состязаний могут. передаваться в блок управления цифровой системы контроля для останова контролируемого блока и фиксации. такта, на котором произошло состязание.

Формула и э о б р е т е н и я

Устройство для обнаружения состязаний в синхронизируемых дискретных блоках, содержащее первый формирователь импульсов, элемент задержки, элемент ИЛИ, первый триггер и первый элемент индикации,. причем выход первого формирователя импульсов соединен с входом элемента задержки, прямой выход первого триггера соединен с входом первого элемента индикации и является выходом статических состязаний устройства, нулевой вход первого триггера является установочным входом устройства, о т л и ч а ю— щ е е с я тем, что, с целью повышения достоверности обнаружения состязаний, в него введены второй формирователь импульсов, второй триггер, второй элемент индикации, счетчик и коммутатор, причем, выход элемента задержки соединен с установочным входом счетчика, информационный выход младшего разряда которого соединен с управляющим входом коммутатора, первый и второй информационные выходы которого соединены с информационными входами соответственно первого и второго триггеров, тактовые входы которых соединены с выходом первого формирователя импульсов, нулевой вход второго триггера подключен к установочному входу устройства, прямой выход второго триггера соединен с входом второго элемента индикации и является выходом динамических состязаний устройства, информационные выходы всех разрядов счетчика, кроме младшего, соединены с соответствующими входами элемента

ИЛИ, выход которого соединен с информационным входом коммутатора, вход первого формирователя импульсов является тактовым входом устройства для подключения к входу синхронизации контролируемого блока, вход второго формирователя импульсов является информационным входом устройства для подключения к выходу признака состояния контролируемого блока, выход вто8хОУ уорюрадателя uhngn сИ дход уормирИа руере ииау

СОР

i ля;. о рого формирователя импульсов соединен со счетным входам счетчика.

12 8750

Составитель В. Гречнев

Техред М.Ходаиич Корректор А. Ильин

Редактор Е. Напп

Заказ 890/51 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. ужгород, ул. Проектная, 4

&no фариирсбавел и юую сп

8Еио рсрииродатеюя 5 иуду сИ без f crnps

8и3 рормцро8аеели5 при нации сосвяЗаний

Стата естю

coervesaeae

Динаиицесние соаттания