Многовходовой сигнатурный анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к контрольно-измерительной технике и может быть использовано-для контроля цифровых узлов радиоэлектронной аппаратуры, имеющих большое число контактов. Цель изобретения - упрощение анализатора при большом количестве информационных входов. Анализатор содержит формиро . ватели 1-1 - 1-Р сигнатур, многовходовые сумматоры 2-1 - 2-.f формирователей сигнатур, параллельные регистры 3-1 - 3-1 формирователей сигнатур, блок 4 свертки по модулю два, многовходовые сумматоры 5-1 - 5-К по модулю два первого яруса блока свертки по модулю два, многовходовые сумматоры 6-1 - 6-С по модулю два, многовходовьй сумматор 7 последнего яруса схемы, блок 8 индикации. 1 ил. с S CWfffKlixoff (Л

1 А1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (11) (51) 4 G 06 F 11/16

ВС7) »)) ) "»р, р р

1 д,,t3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

»

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3739942/24-24 (22) 05.03.84 (46) 23.03.87. Бюл. Ф 11 (72) Ю.И.Галкин, М.Ç.Бененсон, Г.P.Ìåðìåëüøòåéí и,О.Б.Харламова (53) 681.3 (088.8) (56) Авторское свидетельство СССР Р 875390, кл. G 06 F 15/46, 1979.

Патент США В 3976864, кл. G 06 F 11/00, 1976. (54) МНОГОВХОДОВОЙ СИГНАТУРНЫИ АНАЛИЗАТОР (57) Изобретение относится к контрольно-измерительной технике и может быть использовано-для контроля цифровых узлов радиоэлектронной аппаратуры, имеющих большое число контактов. Пель изобретения — упрощение анализатора при большом количестве информационных входов. Анализатор содержит формиро-. ватели 1-1 — l-f сигнатур, многовходовые сумматоры 2-1 — 2-.f формирователей сигнатур, параллельные регистры

3-1 — 3-1 формирователей сигнатур, блок 4 свертки по модулю два, многовходовые сумматоры 5-1 — 5-К по модулю два первого яруса блока свертки по модулю два, многовходовые сумматоры 6-1 — 6-С по модулю два, многовходовый сумматор 7 последнего яруса схемы, блок 8 индикации. 1 ил.

1298751

Изобретение относится к контрольно-измеритепьной технике и может быть использовано для контроля цифровых узлов радиоэлектронной аппаратуры, имеющих большое число контактов.

Цель изобретения — упрощение сигнатурного анализатора при большом количестве информационных входов.

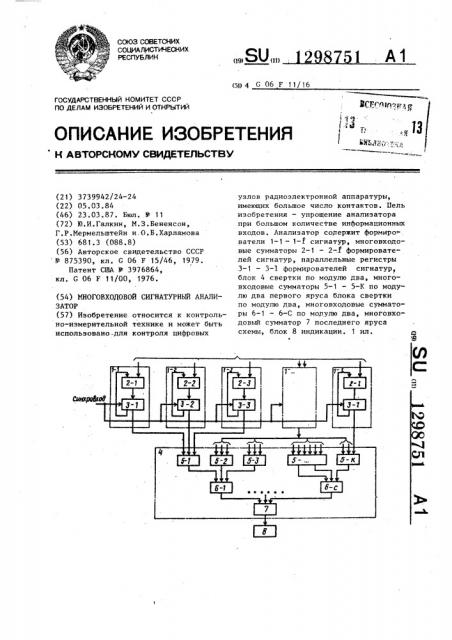

На чертеже приведена структурная схема многовходового сигнатурного свертки по модулю два, многовходовые сумматоры 5-1 — 5-К по модулю два первого яруса блока свертки по модулю два, многовхоловые сумматоры 6-1

6-С по модулю два второго яруса блока свертки по модулю два, многовходовой сумматор 7 последнего яруса схемы, блок 8 индикации.

Уравнения для каждого из разрядов регистра каждого яруса при подаче на вход этого регистра последовательности из 32-х сигналов имеет вид (32 сигнала является оптимальной величиной для существующей элементной базы): анализатора.

Лнализатор содержит формирователи

1-1 — 1-1 сигнатур, многовходовые сумMBTopbl 2-1 — 2-1 формирователей сигнатур, параллельные регистры 3-1

3-1 формирователей сигнатур, блок 4

R, (Т+1) =X

В (т+1) =Х + Х, + Х,< + Х + К (Т) + В<э(т) + В<4(т) + В< (), В (T 1) X + Х, + Х + Х + Х + Х, + В,(Т) + Вб(Т) + В (Т) + Ки(Т) + К< (В (T+1) Хд + X< + X + X + Х + В (Т) + В (Т) + B (Т) Rg(T) + <а()

В (T+1)=X + Х, + Х<> + Хт + Хб + В (Т) + Рз (Т) + Вз(т) + В (Т) + Р< ()

К, (T+1)=-Х + Х„+ Х + Х6 + Х + В (Т) + в,<(Т) + Р (Т) + в,о(Т) + К<6(т) >

7 () Ы « < я 4 4 (6 <О ) и

R (т+ 1 ) =Х„ + X, + Х „, + X + X + В, (т) + В, (т) + B Ä (T ) + B, (т) ;

К (Т+1)=Х + X(T);

R„0(Ò+1) — Х2 + Х< + Х + Х + В (Т) + В.< (Т) + в (Т) + B

P«(T+1) =X«+ Х + X> + Х + К (Т) + В (Т) + В«(Т) + В< (Т) р

R„z(T+1)=Xz< + Х<4 + Хб + К< (Т) + R@(T) + В (Т) + B«<(T);

К (Т+1) — Х,«+ Х + X + Rz (Т) + В«(1,< + Вш(Т) + R <(Т), В„(т+1) =х„+ х„, + х„+ в,(т) + В,(т) + к„(т) + в„(т);

R<5(T+1 Xia «3 4 и < О

RÄ(T+1)=х„, + х„+ х + в,(т) + в„(т) + B»(T) + к„(т), I

В2 (т+") ° ° °,К",6(т+1) — 35 блока свертки по модулю два, содержасостояния соответствующих разрядов щей m многовходовых сумматоров. При сдвигового регистра после поступления этом соединение группы выходов формина его вход последовательности из рователей сигнатур с входами одной

R=m K=32 сигналов, R<(Т), В (Т),..., группы сумматоров первого яруса проR (Ò) — до поступления; . щ изводится в соответствии с приведенХ<„Х,...,Х< — значения двоичных ными уравнениями формирования сигнасигналов на выходах первого, второго туры, в которых значения R<(T+1),..., и т.д, контактов контролируемого циф- К< (Т+1) соответствуют выходам перворового узла. го формирователя группы, значения

Полученные уравнения реализуются в 5 Х,...,X« соответствуют выходам втов виде схемы многовходового суммато- рого формирователя группы, значения ра и регистра. Число входов сумматора Х„,...,Х соответствуют выходам тредля каждого из разрядов регистра рав- тьего формирователя группы. но числу слагаемых в уравнении для Рри количестве многовходовых сумэтого разряда. 5О маторов первого яруса схем больше 16

Если число контактов контролируе- образуется второй ярус. Выходы суммамого цифрового узла больше 32, то торов первого яруса схемы разбиваются число формируемых в соответствии с на группы аналогично разбиению выхопривеценными уравнениями сигнатур Х > дов формирователей сигнатур и соеди> 1. В этом случае выходы Х формирова- 55 няются с входами одной группы из m телей сигнатур разбиваются на группы, многовходовых сумматоров следующего состоящие из выходов трех формирова- яруса в соответствии с. уравнениями телей, соединенных с входами одной формирования сигнатуры, при этом энагруппы сумматоров первого яруса схемы чения R<(T+1),...,B,< (T+1), значения

Составитель И.Сафронова

Техред N.Xoäàíè÷ Корректор С.Шекмар

Редактор Е.Папп

Заказ 890/51 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-.полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12987

Х<,...,Х „ и Р,(Т),...,К< (Т) заменяются на значения выходов сумматоров предыдущего яруса аналогично тому, как это было сделано для выходов формирователей сигнатур. Образование каж- 5 дого последующего яруса производится при числе многовходовых сумматоров предыдущего яруса, большем 16.

На последнем ярусе будет формироваться одна сигнатура, образующаяся 10 на выходах 16-и сумматоров последнего яруса. Выходы этих сумматоров соединяются с входом блока индикации.

Формула изобретенря 15

Многовходовой сигнатурный анализа- тор, содержащий блок индикации и фор-. мирователь сигнатур, информационные входы которого образуют первую группу 20 информационных входов анализатора, а синхровход соединен с синхровходом анализатора, причем формирователь сигнатур содержит группу сумматоров по модулю два и m-разрядный регистр, 25 где m — число сумматоров по модулю два в группе, первые входы сумматоров о по модулю два группы образуют группу информационных входов формирователя сигнатур, а выходы соединены с соответствующими информационными входами регистра, управляющий вход записи которого является синхровходом формиро51 4 вателя сигнатур, разряпные выходы регистра соединены с входами сумматоров по модулю два в соответствии с видом образующего полинома, о т л и ч а ю— шийся тем, что, с целью упроще— ния анализатора при большом количестве информационных входов, он содержит группу формирователей сигнатур и блок свертки по модулю два, причем информационные входы формирователей сигнатур образуют соответствующие группы информационных входов анализатора, синхровходы формирователей сигнатур соединены с синхровходом анализатора, группы выходов формирователей сигнатур в соответствии с видом образующего полинома соединены с соответствующими группами входов блока свертки по модулю два, группа выходов

:которого соединена с группой входов блока индикации, причем блок свертки по модулю два содержит группу сумматоров по модулю два, соединенных по многоярусной схеме, входы сумматоров по модулю два первого яруса образуют группы входов блока, группы выходов сумматоров по модулю два i-ro.ÿðóñà (i=1,L-1, где L — число ярусов) соединены в соответствии с видом образующего полинома с группами входов сумматоров по модулю два (i+ 1)-го яруса, группа выходов L-го яруса является группой выходов блока.