Устройство сопряжения процессора с арифметическим расширителем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки информации для одновременного подключения к процессору через общую.шину ЭВМ внешних устройств, в качестве t Л § (Л to 00 СП 00 IV) Фиг./

СВОЗ СОВЕТСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 129875 (51)4 С 06 F 3 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (54) УСТРОЙСТВО СОПРЯЖЕНИЯ ПРОЦЕССОРА С АРИФМЕТИЧЕСКИМ РАСШИРИТЕЛЕМ (57) Изобретенио относится к вычислительной технике и может быть использовано в устройствах обработки информации для одновременного подключения к процессору через общую, шину

ЭВМ внешних устройств, в качестве

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ (61) 1182529 (21) 3971955/24-?4 * (22) 29.10.85 (46) 23.03.87. Бюл, Ф 11 (72) А.И. Каменков, Л.И, Коняхина и С.д. Бороненко (53) 681.327.11 (088.8) (56) Авторское свидетельство СССР

В 1182529, кл. G 06 F 13/00, 1984.

ВС (Оцщц ,13

1 иа::.:.;.;;, 1298758

35 которых могут использоваться расширители арифметики, функциональные расширители, периферийные процессоры за счет сопряжения процессора одновременно с несколькими функциональными расшнрителями такого типа, которым для работы требуется органиэация записи.и считывания более двух операндов. Целью изобретения является расширение класса решаемых задач. Это достигается тем; что в устройство, позволяющее осуществить загрузку операндов с общей шины в функциональные расширители

Изобретение относится к вычислительной технике, может быть использовано в устройствах обработки информации для подключения функциональ- ных расширителей (ФР), например арифметических, к электронно-вычислительной машине (ЭВМ), и является

"усовершенствованием устройства по основному авт.св. N 1182529.

Цель изобретения — расширение класса решаемых задач за счет обеспечения возможности подключения группы расширителей.

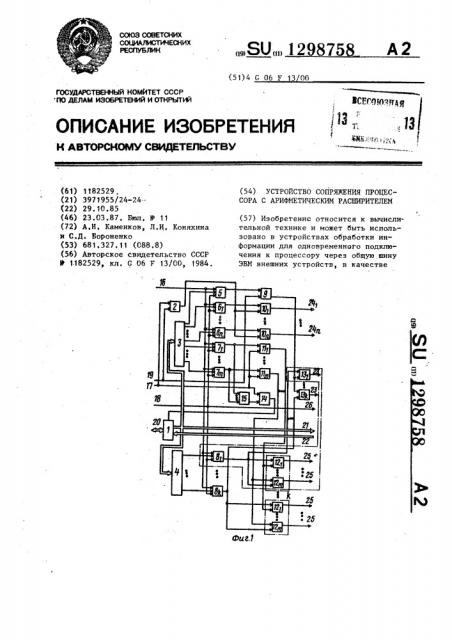

На фиг. 1 представлена блок-схема устройства; на фиг. 2 и 3 — временные диаграммы работы устройства в циклах "Ввод" и "Вывод".

Устройство (фиг. 1) содержит магистральный приемопередатчик (МПП)

1, первый элемент ИЛИ 2, блоки 3 и 4 памяти, триггер 5 признака записи микрокоманды, триггеры 6 и 7 первой и второй групп, триггеры 8, одновибратор 9 записи микрокоманды, одновибраторы 10 и 11, элементы И 12 группы, составляющие вместе с триггером 8 и элементом И 13. узел формирования сигналов записи микрокоманды и считывания операндов результата (обозначен штрихпунктирной линией на фиг, 1), элемент И 14, элемент ИЛИ 15, входы 16 признака адреса данных, 17 признака ввода, 18 начальной установки и 19 признака вывода данных устройства, информационный вход-выход 20 устройства, информационный выход 21 устройства, параллельно с выполнением команд процессора, связанных с обращением к памяти ЭВМ, и содержащее магистральный приемопередатчик 1, первый блок 3 памяти, два элемента ИЛИ

2, 15, элемент И 14, группы одновибраторов, группы триггеров, второй блок 4 памяти, группы триггеров 8 и элементов И 12, 13, что позволяет подключить через одно устройство k функциональный расширителей, в каждый из которых можно записать п операндов и считать m результатов. 3 ил, 2 информационный вход 22 устройства, выходы 23 записи микрокоманды, выходы 24 записи операндов (n — число выходов записи операндов в ФР), считывания операндов результата 25, выход 26 начальной установки устройства. о

Устройство работает следующим образом.

При обмене информацией с информационного входа-выхода 20 устройства через МПП 1 на адресные входы блоков 3 и 4 поступает адрес ячейки памяти, По адресам в блоках 3 и 4 записаны двоичные коды, которые являются признаками для формирования сигналов записи-считывания, поступающих на выходы 23 — 25 устройства,.

По управляющему сигналу с входа 16 двоичный код иэ блока 3 поступает в триггеры 5-7,.а иэ блока 4 — в триггеры 8. Сигнал " 1", поступающий на вход триггера 5, является признаком записи микрокоманды, на входы триггеров 6 — признаком записи операндов в ФР, на входы триггеров 7 признаком считывания m-операндов, на входы триггеров 8 — кодом, определяющим, в какой из ФР,записывается микрокоманда или из какого ФР будет считана информация в цикле ввода результатов в 3ВМ. Запись сигнала

"1" в триггеры 5 - 7 является разрешением срабатывания одновибраторов

9-11 при приходе с входов 17 и 19 устройства управляющих сигналов признаков ввода-вывода данных. Одновиб3 12, раторы 10 формируют импульсы, поступающие одновременно на входы записи операнда всех Е функциональных расширителей, подключенных К устройству. Одновибраторы 11. формируют импульсы, поступающие на вторые входы элементов И 12 на первые входы которых поступает код с триггеров 8.

Сигнал с выхода элемента И 12 является сигналом считывания ш-го опе ранда (определяется срабатьгванием тп-ro одновибратора 11)-из k-ro ФР (определяется записью "1" в один из k триггеров 8). Одновибратор 9 формирует импульс, поступающий на первые входы элементов И 13, на вторые входы которьгх поступает код с триггеров 8, сигналы с выходов И 13 поступают на входы записи микрокоманцы функциональных расширителей и являются вьгходами 23 записи устройства. ИПП 1 работает на выдачу информации на вход-выход 20 при считывании результата, а в остальных случаях - на прием из нее, Сброс устройства, происходит по сигналу, поступающему на вход 18 устройства.

Такая органиэация позволяет подключить через одно устройство k функциональных расширителей, в каждый иэ которых можно записать й-операндов и считывать ш-результатов.

Формула изобретения

Устройство сопряжения процессора с арифметическим расширителем по авт. св. Я -1182529, о т л и ч а ю — . щ е е с я тем, что, с целью расширения класса решаемьгх задач за счет

98758 обеспечения воэможности подключения группы расширителей,. в устройство введены второй блок памяти, К узлов формирования сигналов записи микрокоманды и считывания операндов результата, каждый иэ которых состоит из триггера, элемента И н группы элементов И, причем.в каждом узле формирования сигналов записи микро10 команды и считывания операндов результата выход триггера соединен с первыми входами элементов И и элементов И группы, выходы которых являются соответственно выходом устройг5 ства для подключения к входу сигнала записи микрокоманды и группой выходов устройства для подключения к группе входов сигналов считывания операндов соответствующего расши20 рителя, адресный вход блока памяти соединен с информационным выходом магистрального приемопередатчика, а

i-й выход (i = 1,k) — с информационным входом триггера i-ro узла формирования сигналов записи микрокоманды и считывания операндов результата, входы сброса и синхронизации которого соединены соответственно с входами начальной установки и приз" нака адреса данных устройства, вторые входы элементов И группы х-го узла формирования сигналов записи микрокоманды и считывания операндов результата соединены с выходами со35 ответствующих одновибраторов, выход одновибратора записи микрокоманды соединен с вторьгми входами элементов

И узлов формирования сигналов записи микрокоманды и считывания операн40 дов результата.

1 2987 58

СИА

88од

Адр

8ях -И

1298758

2Ююс

/Л4П

8ый

Np b

Вых 5П

8ых -И1Ю

Фиа 3

Составитель В. Вертлиб

Техред Л.Сердюкова Корректор С. Шекмар

Редактор Е. Папп

Заказ 891/52 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открьггий

" 113035, Иосква, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул, Проектная, 4