Устройство для контроля параметров

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и информационно-измерительной техники и может быть использовано в информационно-измерительных системах и информационно-вычислительных комплексах АСУТП. Цель изобретения - повышение помехоустойчивости-, устройства. Цель достигается тем, что в устройство для контроля пара .метров, содержащее индикатор 3, вход которого соединен с выходом первого блока 7 памяти, блок 2 управления , вход которого соединен с выходом генератора 1 импульсов, коммутатор 4, информационные входы которого являются соответствующими входами устройства , управляющий вход соединен с первым выходом блока 2 управления, а выход коммутатора 4 - с входом элемента 6 задержки, дополнительно введены элемент И:, второй блок 9 памяти , селектор 8 вида параметра с их связями. Это обеспечивает работу устройства в непрерывном циклическом режиме и контроль параметров любого вида датчиков. Контролируемые события регистрируются по результатам анализа за два цикла опроса датчиков, что исключает ложную регистрацию при появлении внешних помех длительностью менее одного цикла опроса всех датчиков. 2 з.п. ф-лы, 4 ил. i (Л ю со 00.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1298770 А1 (5D 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3971349/24-24 (22) 29. 10.85 (46) 23. 03.87. Бюл. № 11 (72) С.А.Артамонов, В.А.Лернер, А.П.Савельев и В.И.Семенов (53) 681 325(088.8) (56) Авторское свидетельство СССР № 562823, кл. G 06 F 11/ОО, 1975.

Авторское свидетельство .СССР № 978157, кл. С 06 F 15/46, 1982. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ (57) Изобретение относится к области автоматики и информационно-измерительной техники и может быть использовано в информационно-измерительных системах и информационно-вычислительных комплексах АСУТП. Цель изобретения — повышение помехоустойчивости: устройства. Цель достигается тем, что в устройство для контроля параметров, содержащее индикатор 3, вход которого соединен с выходом первого блока 7 памяти, блок 2 управления, вход которого соединен с выходом генератора 1 импульсов, коммутатор

4, информационные входы которого являются соответствующими входами устройства, управляющий вход соединен с первым выходом блока 2 управления, а выход коммутатора 4 — с входом элемента 6 задержки, дополнительно введены элемент И:, второй блок 9 па- мяти, селектор 8 вида параметра с их связями. Это обеспечивает работу устройства в непрерывном циклическом режиме и контроль параметров любого вида датчиков. Контролируемые события регистрируются по результатам анализа эа два цикла опроса датчиков, что исключает ложную регистрацию при появлении внешних помех длительностью менее одного цикла опроса всех датчиков. 2 з.п, ф-лы, 4 ил.

12987

Изобретение относится к автоматике и информационно-измерительной технике и может быть использовано н информационно-измерительных системах (ИИС) и информационно-вычислительных комплексах (ИВК) автоматизированных систем управления технологическими процессами (АСУТП) .

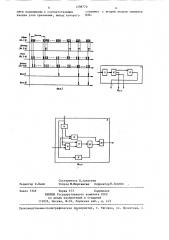

Цель изобретения — расширение области применения за счет работы с разными датчиками к повышение помехоустойчивости устройства, На фиг. 1 изображена схема устройства, на фиг. 2 — временная диаграмм ма, ка фиг. 3 и 4 — схемы блока управления и селектора вида параметра соответственно.

Устройство (фкг. 1) содержит генератор 1 импульсов, блок 2 управления, индикатор 3, коммутатор 4, дат- 20 чики 5, элемент б задержки, первый блок 7 памяти, селектор 8 вида параметра, второй блок 9 памяти, элемент И 10.

bJIок управления (фиг. 3) содержит первый счетчик 11, дешифратор 12, второй счетчик 13.

Селектор вида параметра (фиг. 4) содержит дешифратор 14, элемент И 15, ключ 16, АЦП 17, узел 18 сравнения, 30 узел 19 памяти, элемент ИЛИ 20. . Устройство работает следующим образом.

Импульсные сигналы с выхода генератора 1 импульсов поступают на вход счетчика 11 блока 2 управления.

Счетчик 11 производит пересчет импульсов на три и совместно с дешифратором 12 представляет собой распределитель импульсов. С первого вы- 40 хода дешифратора 12 каждый первый иэ трех импульсов поступает на вход счетчика 13, с второго выхода каждый второй импульс поступает на второй выход блока 2 управления и явля- 45 ется тактом считывания, поступающим на вход блока 9 памяти. С третьего выхода дешифратора 12 каждый третий импульс поступает на третий выход блока 2 управления и является тактом 50 записи, поступающим на вход блока 9.

Выход счетчика 13 является первым выходом блока 2 управления и представляет собой код адреса опрашиваемого датчика, поступающий на управляющий вход коммутатора 4, который в постоянном циклическом режиме производит поочередное подключение датчиков 5 через элемент 6 задержки

70 2 к селектору 8. Код адреса опрашиваемого датчика поступает на вход дешифратора 14, входящего н состав селектора 8. Прк опросе аналогового датчика появляется сигнал на первом выходе дешифратора 14, поступающий на управляющий вход ключа 16 и управляющий вход АЦП 17. При этом аналогоный сигнал через ключ 16 поступает на вход АЦП 17, где производится аналого-цифровое преобразонаННе и вывод на первый вход узла 18 сравнения, на второй вход которого с выхода узла 19 памяти поступает код устанки, соответствующий поступающему на вход узла 19 адресу опрашиваемого датчика. В случае, если величина аналогового сигнала, подключенного к АЦП 17, больше величины уставки (т.е. величина контролируемого с помощью аналогового датчика параметра превышает допустимую норму). то íà выходе узла 18 сравнения появляется сигнал, который через элемент ИЛИ 20 поступает на выход селектора 8 вида параметра.

При опросе дискретного датчика появляется сигнал на втором выходе дешкфратора 14,, поступающий на первый вход элемента И 15, на второй вход которого поступает сигнал от дискретного датчика. В случае, если дискретный датчик сработал (например, сигнал аварийной защиты), то на второй вход элемента И 15 поступает сигнал "1" и ка выходе элемента

И 15 также формируется сигнал "1", который через элемент ИЛИ 20 поступает на выход селектора 8.

Элемент 6 задержки обеспечивает ликвидацию сбоев от влияния процессов переключения внутри коммутатора 4.

Частота импульсов генератора 1 импульсов выбирается такой, чтобы время опроса всех датчиков 5 было бы меньше времени до момента возникновения второго события, вызванного первым.

Адресные сигналы, формируемые на первом выходе блока 2 управления, поступают на адресный вход блока 9 памяти, на информационный .вход которого с выхода селектора 8 поступает информационный сигнал, который одновременно поступает на второй вход элемента И 10. Затем формируется на втором выходе блока 2 управления сиг.нал считывания информации по выставленному адресу, поступающий на

12987

3 третий вход блока 9, с выхода которого считанный сигнал подается на первый вход элемента И 1 . Из временной диаграммы (фиг. 2) и функциональной схемы устройства (фиг. 1) видно, что при первичном возникновении на выходе селектора 8 вида параметра по какому-либо адресу логического сигнала

" 1" последний записывается в блок 9, но на выход элемента И 10 и на второй10 выход устройства он не проходит.

Если и во втором цикле опроса по тому же адресу формируется на выходе селектора 8 логический сигнал " 1", то на такте считывания на выходе эле-15 мента И 10 и на втором выходе устройства формируется логический сигнал

" 1", который поступает на вход блока

7 памяти в качестве сигнала, разрешающего запись данного адреса и вы- 2О вода на индикацию.

В случае занятости блока 7 памяти последний запирается для записи любой новой информации (например, с помощью маркерного разряда). Если при втором 25 цикле опроса датчиков по тому же адресу не сформируется логический сигнал " 1" на выходе селектора 8 вида параметра, то на выход элемента

И 10 и на выход устройства он не 30 проходит.

Таким образом, любая внешняя помеха, которая может вызвать ложный логический сигнал на выходе селектора 8, на выходе устройства и на ин35 дикации не отражается. Лишь достоверная информация, возникающая на выходе селектора 8 два цикла подряд, зафиксируется устройством. Этим дос- „ тигается по сравнению с известным устройством высокая помехоустойчивость устройства, что очень существенно при применении устройства в

АСУТП, уровень внешних (промышленных) помех для которых в большинстве случаев значителен.

Формула изобретения

1. Устройство для контроля параметров, содержащее индикатор, вход которого соединен с выходом первого блока памяти, блок управления, вход которого соединен с выходом генератора импульсов, коммутатор, информационные входы которого являются соответствующими входами устройства, управляющий вход соединен с первым

70 4 выходом блока управления, а выход коммутатора соединен с входом элементазадержки,отличающееся тем, что, с целью расширения области применения за счет работы с разными датчиками и повышения помехоустойчивости устройства, в него введены элемент И, второй блок памяти и селектор вида параметра, информационный вход которого соединен с выходом элемента задержки, адресный вход соединен с первым выходом блока управления, адресными входами первого и второго блоков памяти и первым выходом устройства, выход селектора вида параметра соединен с информационным входом второго блока памяти и первым входом элемента И, второй вход которого соединен с выходом второго блока памяти, выход элемента И соединен с управляющим входом первого блока памяти и вторым выходом устройства, второй и третий выходы блока управления соединены с входами чтения и записи второго блока памяти соответственно.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок управления содержит первый и второй счетчики и дешифратор, первый выход которого через второй счетчик подключен к первому выходу блрка, а второй и третий выходы дешифратора являются вторым и третьим выходами блока соответственно, вход первого счетчика является входом блока, выход соединен с входом дешифратора, 3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что селектор вида параметра содержит дешифратор, ключ, аналого-цифровой преобразователь, элемент И, узел сравнения, узел памяти и элемент ИЛИ, выход которого является выходом селектора, входы дешифратора и узла памяти являются адресным входом селектора, первый вход элемента И и информационный вход ключа являются информационным входом селектора, первый выход дешифратора соединен с управляющими входами ключа и аналого-цифрового преобразователя, информационный вход которого подключен к вьжоду ключа, второй выход дешифратора соединен с вторым входом элемента И, выход которого подключен к первому входу элемента ИЛИ, выходы аналогоцифрового преобразователя и узла па! 298770 мяти подключены к соответствующим входам узла сравнения, выход которого соединен с вторым входом элемента

ИЛИ.

Составитель И.Алексеев

Техред М.Иоргеитал Корректор И.Зрдейи

Редактор Е.Папп

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35„ Раушская наб., д. 4/5

Заказ 1349

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4