Устройство управления блоками памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления блоками памяти, используемых в составе процессора цифровой вычислительной мап1ины. Целью изобретения является повышение быстродействия устройства. Устройство содержит буферный регистр, входной и выходной регистры, первый и второй регистры адреса, блок сравнения, дешифратор, счетчик первый и второй элементы И, элемент И - НЕ, блок синхронизации. Повышение быстродействия устройства достигается за счет обеспечения в режиме отражения к разным блокам памяти возможности выдачи последовательных сигналов обращения через интервалы времени, меньшие, чем длительность циклоЕ обращения к блокам памяти. 3 ил. IND 00 ;о со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

5И 4 а 11 с 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

1 ,1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3879204/24-24 (22) 28.03.85 (46) 23.03.87. Бюл. № 11 (72) Л. И. Дрель и И. С. Мугинштейн (53) 681.327.67 (088.8) (56) Авторское свидетельство СССР № 947866, кл. G 06 F 13/06, 1982.

Авторское свидетельство СССР № 1037236, кл. G 06 F 13/00, 1983. (54) УСТРОЙСТВО УПРАВЛЕНИЯ БЛОКАМИ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления бло.Я0,„1298799 А 1 ками памяти, используемых в составе процессора цифровой вычислительной машины.

Целью изобретения является повышение быстродействия устройства. Устройство содержит буферный регистр, входной и выходной регистры, первый и второй регистры адреса, блок сравнения, дешифратор, счетчик, первый и второй элементы И, элемент И вЂ” НЕ, блок синхронизации, Повышение быстродействия устройства достигается за счет обеспечения в режиме отражения к разным блокам памяти возможности выдачи последовательных сигналов обрагцения через интервалы времени, меньшие, чем длительность циклов обрашения к блокам памяти. 3 ил.

1298799

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления блоками памяти, используемых в составе процессора цифровой вычислительной машины.

Целью изобретения является повышение быстродействия устройства.

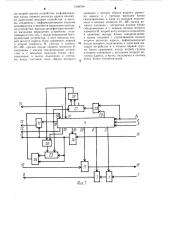

На фиг. 1 представлена схема устройства управления группой блоков памяти; на фиг. 2 — схема блока синхронизации; на фиг. 3 --- временная диаграмма работы устройств».

Устройство управления группой блоков памяти (фиг. ) содержит буферный регистр 1, информационные и управляющий входы которого соединены соответственно с первыми информационными входами 2 устройства и первым выходом 3 блока 4 синхронизации, первый, второй и третий входы которого являются соответственно входами 5, 6 и 6< сигналов «Чтение», «Запись» и «Синхронизация» устройства, выходной регистр 7, выходы которого соединены с информационными выходами 8 устройства, а управляющий вход— с вторым выходом 9 блока 4 синхронизации, третьим выходом 10 подключенного к управляюгцему входу дешифратора 11 выбора блока памяти, выходы которого являются выходами 12 обращения устройства, а информационные входы соединены с адресными выходами 13 устройства и выходами первого регистра 14 адреса, информационные входы которого являются адресными входами 15 устройства, а управляющий вход подключен к четвертому выходу 16 блока 4 синхронизации, входной регистр 17, выходы которого являются вторыми информационными выходами 18 устройства, а информационные и управляющий входы соединены соответственно с вторыми информационвходами 19 cTpoHcTBB ходом 20 блока 4 синхронизации, шестой и седьмой выходы которого являются соответственно выходами 2! и 22 сигналов

«Чтение» и «Запись» устройства, второй регистр 23 адреса, блок 24 сравнения, первый 25 и второй 26 элементы И, счетчик

27 и первый элемент И вЂ” -HE 28. Причем

Bxoffbl первого элемента И 25 связаны с восьмым выходом 29 блока 4 синхронизации, девятым выходом 30 подключенного к первому входу второго элемента И 26, выход элемента И вЂ” HF 28 связан с четвертым входом 31 блока 4 синхронизации.

Ьлок 4 синхронизации (фиг. 2) содержит кольцевой регистр 32 сдвига, элементы ИЛИ 33 — 37, элемент И вЂ” -НЕ 38, элементы HF 39 и 40, элементы И 41 — 49, вход

50.

Работа устройства управления группой блоков IIB ìÿ Tè осуществляется следующим образом.

В исходном состоянии в кольцевом регистре 32 сдвиг,> (например, двенадцатиразрядном) записана «1» (логическая единица) в

5 !

О !

55 одном из разрядов. При поступлении синхросигналов через элемент И 44 с входа 4 синхронизации устройства на управляющий вход регистра 32 «1» будет последовательно переписываться из одного разряда в другой, осугцествляя движение по «кольцу». При движении «1» по разрядам регистра 32 вырабатываются единичные потенциалы на соответствующих выходах элементов ИЛИ 34 — 37.

Так, «1» на выходе элемента ИЛИ 35 появляется при наличии «!» в первом или седьмом разрядах регистра 32, на выходе элемента ИЛИ 36 — при «1» в третьем или девятом разрядах, на выходе элемента ИЛИ 37 — при «1» в пятом или одиннадцатом разрядах, на выходе элемента

ИЛИ 34 -- при «l» в шестом или двенадцатом разрядах. Интервал времени, в течение которого «1» в кольцевом регистре 32 сдви.-а проходит все разряды, равен длительности цикла обращения к блокам памяти.

Работа начинается с поступления из процессора на вход 15 устройства адреса ячейки блока памяти, к которой должно быть произведено обращение, и выдачи на вход 5 сигнала «Чтение» или выдачи на вход 6 сигнала «Запись». Выработка сигнала «Чтение» («Запись») и адреса осуществляется в определенные моменты времени, просинхронизованные к работе устройства, что может быгь достигнуто, например, за счет использования регистра 32 в качестве программного датчика процессора.

Сигнал «Чтение», характеризующий начало отработки устройством режима чтения информации из блока памяти, непосредственно и через элемент ИЛИ 33 поступает на входы элементов И 46, 47, 49 и 41. При его совпадении на входах элементов И 46, 47, 49 и 41 с сигналами с выходов элементов

ИЛИ 37, 35 и 36 вырабатываются соответственно сигналы на выходах 16, 22, 10 и ?О блока 4 синхронизации. По заднему фронту сигнала на выходе 16 блока 4 осугцествляется прием. адреса ячейки блока памяти на регистр 14. Сигнал с выхода 21 поступает в блоки памяти, определяя их работу в режиме чтения.

Сигнал «а выходе 10 блока 4 синхронизации осуществляет сброс счетчика 27 и стробирование деши<рратора 11, обеспечивая формирование на одном из его выходов обращения к блоку памяти. Выход, на котором появляется сигнал обращения, определяется в зависимости от значения адреса, присутствующего на информационном выходе дешифратора 11. Кроме того, задним фронтом сигнала на выходе 10 блока 4 производится перепись значения адреса с регистра 14 на регистр 23. Появлению сигнала на выходе 10 блока 4 всегда предшествует сигнал, вырабатываемый вторым элементом И вЂ” HF

38 на выходе 30 блока 4 и поступаю. щий через элемент И 26 на вход сброса регистра 23. После приема адреса на ре1298799 гистр 23 на входах блока 24 сравнения оказываются одинаковые сигналы, что приводит к появлению на его выходе единичного потенциала, поступаюгцего на вход

10 блока 4 синхронизации.

Разрядность регистра 23 и соответственно количество разрядов, поступающих с регистров 23 и 14 на входы блока 24 сравнения. определяются числом разрядов в адресе, необходимых для задания различных номеров блоков памяти, к которым осущест- 10 вляется обращение. Например, при наличии в группе выходов 8 блоков памяти емкостью по 8К слов каждый для задания номера, при шестнадцатиразрядном адресе, достаточно трех старших разрядов адреса.

По сигналу на выходе 20 блока 4 синхронизации, которым заканчивается режим однократного чтения, осуществляется прием информации, считанной из блока памяти, на регистр 17 и выдача ее в процессор по выходу 18.

Сигнал «Запись», характеризующий начало отработки устройством режима записи информации в блок памяти, непосредственно и через элемент ИЛИ 33 поступает на входы элементов И 48, 42, 43, 46 и 47. При его совпадении на элементах И 49, 42, 43, 46 и 47 с сигналами с выходов элементов ИЛИ 37, 35 и 36 вырабатываются соответствующие сигналы на выходах 16, 10, 22, 3 и 9 блока 4 синхронизации. Сигнал с выхода 22 поступает в блоки памяти, определяя их работу в режиме записи. Сигналами на выходах 3 и 9 блока 4 синхронизации осуществляется прием информации, запись которой необходимо произвести для промежуточного хранения на регистр 1 и затем на регистр 7 для выдачи в блоки памяти по информационному выходу 8. Действия сигналов на выходах 16 и 10 аналогичны рассмотренным в режиме чтения.

Интервал времени от выдачи сигнала обращения до приема считанной информации на регистр 17 в режиме чтения или соот- 40 ветствующий интервал времени в режиме записи, являющийся временем чтения (записи) информации в блок памяти, определяет фактическую занятость адресной и числовых магистралей 13, 19 и 8. Указанный интервал времени значительно меньше цикла 45 обращения к блокам памяти. По истечению этого времени процессор обеспечивает поступление нового значения адреса ячейки блока памяти на вход 15 устройства и выдачу сигнала «Чтение» или «Запись» на соответствующие входы 5 или 6 устройства. По сигналу на выходе 16 блока 4 осуществляется прием нового значения адреса на регистр 14.

В случае, если вновь принятый адрес принадлежит другому блоку памяти группы, а не тому, к которому производилось предыдущее обращение, на выходе блока 24 сравнения оказывается низкий уровень (логический ноль), он поступает на вход 32 блока 4 и блокирует прохождение сигналов через элемент И 45, подтверждая нулевой уровень на выходе 29 блока 4. Дальнейшая работа устройства не отличается от рассмотренной.

В случае, если принятый на регистр 14 адрес принадлежит блоку памяти, к KQTopoìó производилось предыдущее обращение, и интервал времени от момента его выдачи меньше, чем цикл обращения блока памяти, то и после приема адреса на регистр 14 на выходе блока 24 сравнения присутствует высокий потенциал (логическая единица). При совпадении высоких уровней сигналов на всех входах элемента И 45 появляется единичный уровень на его выходе. Поступая через элемент HE 40 на вход элемента Й 44, он блокирует поступление синхросигнаlOB на вход регистра 32 и разрешает их прохождение через элемент И 25 на счетный вход счетчика 27.

На счетчике 27 обеспечивается формирование выдержки времени до момента, когда будет возможна выдача повторного обращения к блоку памяти без нарушения временной диаграммы его функционирования.

После поступления шести импульсов на выходах счетчика 27, связанных с элементом

И вЂ” НЕ 28, появляется потенциал логической единицы. На выходе элемента ИНЕ 28 вырабатывается сигнал низкого уровня, осуществляющий через элемент И 26 сброс регистра 23 и поступающий на вход 31 блока 4, обеспечивая появление нулевого уровня сигнала на выходе элемента И 45.

При этом разрешается прохождение синхросигналов на управляющий вход регистра

32 и запрещается их поступление на счетный вход счетчика 27.

Формула изобрегенп»

Устройство управления блоками памяти, содержащее блок синхронизации, первый, второй, третий, четвертый и пятый выходы которого соединены соответственно с управляющими входами буферного регистра, выходного регистра, дешифратора, первого регистра адреса и входного регистра, первый, второй и третий входы блока синхронизации являются соответственно входами чтения, записи и синхронизации устройства, а шестой и седьмой выходы — выходами чтения и записи устройства, информационные входы буферного регистра являются информационными входами первой группы устройства, а выходы подключены к информационным входам выходного регистра, выходы которого являются информационными выходами первой группы устройства, информационные входы и выходы входного регистра являются информационными входами и выхода!

298799 ми второй группы устройства, информационные входы первого регистра адреса являются адресными входами устройства, а выходы соединены с информационными входами дешифратора и являются адресными выходами устройства, выходы дешифратора являются выходами обращения устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй регистр адреса, блок сравнения, первый и второй элементы И, счетчик и элемент

И вЂ” НЕ, причем входы первого элемента И соединены с входом синхронизации устройства и с восьмым выходом блока синхронизации, а выход подключен к счетному входу счетчика, вход сброса которого соединен с входом сброса второго регистра адреса и с третьим выходом блока синхронизации, а одни из выходов подключены к входам элемента И вЂ” НЕ, выход которого соединен с четвертым входом блока синхронизации и с первым входом второго элемента И, второй вход которого подключен к девятому выходу блока синхронизации, а выход соединен с управляющим входом второго регистра адреса, информационные

IO входы которого подключены к адресным выходам устройства и к входам первой группы блока сравнения, входы второй группы которого соединены с выходами второго регистра адреса, 3 выход подключен к пятому

15 входу блока синхронизации.

1298799

Синхрогигнаягн

Bwxouoi 32 региггпра

Чтение !запигь)

ФИ ймкроо,гоо гчетчйна 27

1b

Обращение n йпорои бяон поии обращение и пербону бяок памят

12

12

У

Л7

Юхоо crerrai c ,72

20 ра ны бяот6 памяти

Составитель О. Исаев

Редактор В. Данко Техред И. Верес Корректор О. Луговая

Заказ 751/54 Тираж 59о Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4!5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4