Умножитель частоты

Иллюстрации

Показать всеРеферат

Изобретение м.б. использовано в системах передачи ЧМ-сигналов. Цель изобретения - повышение точности умножения частоты. Устр-во содержит формирователь импульсов 1, блок 3 интегрирования , блок 12 компараторов, многовходовый сумматор 13, полосовой фильтр 14. Вновь введены эл-т задержки 2, эл-ты памяти 4-6, источникопорного напряжения 7, блок вычитания 8, перемножитель 9, делитель 10 напряжений, сумматор 11. 2 ил. / 1 ю со оо с 00 ГС

С(МОЗ COBETCHHX

СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК (59 4 Н 03 В 19/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3978170/24-09 (22) 11.11.85 (46) 23.03.87. Бюл. № 11 (71) Куйбьппевский электротехнический институт связи .(72) Л.Б.Аснин (53) 621.374.4(088.8) (56) Авторское свидетельство СССР № 1190458, кл. Н 03 В 19/00, 13.07.83.

Авторское свидетельство СССР № 559358, кл. Н 03 В 19/00, 16.!2.74.

„„Я0„„1298832 (54) УМНОЖИТЕЛЬ ЧАСТОТЫ - (57) Изобретение м.б. использовано в системах передачи ЧМ-сигналов. Цель изобретения — повьппение точности умножения частоты. Устр-во содержит формирователь импульсов 1, блок 3 интегрирования, блок 12 компараторов, многовходовый сумматор )3, полосовой фильтр 14. Вновь введены эл-т задержки 2, эл-ты памяти 4-6, источник . опорного напряжения 7, блок вычитания 8, перемножитель 9, делитель !О напряжений, сумматор 11. 2 ил.

- 2988 и о интй

Изобретение относится к радиотехнике и может быть использовано в системах передачи частотно-модулированных сигналов.

Цель изобретения — повышение точности умножения частоты.

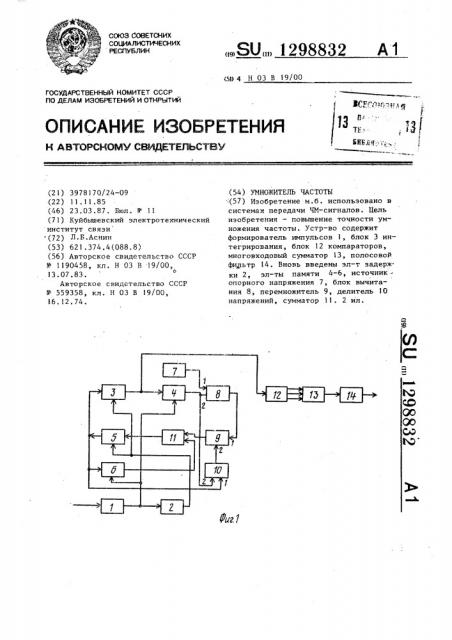

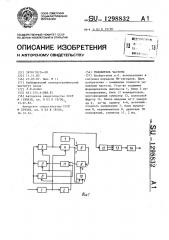

На фиг ° 1 представлена функциональная схема умножителя частоты, на фиг.2 — временные диаграммы, поясняющие работу умножителя. 1О

Умножитель частоты содержит формирователь 1 импульсов, элемент 2 задержки, блок 3 интегрирования, первый 4, второй 5 и третий 6 элементы памяти, источник 7 опорного напряжения, блок 8 вычитания, перемножитель

9, делитель 10 напряжений, сумматор

ll блок 12 компараторов, многовходовый сумматор 13 и полосовой фильтр 14.

Умножитель частоты работает следующим образом.

На вход формирователя 1 импульсов (фиг.l) поступает гармонический сигнал или периодическая последовательность импульсов, и на его выходе формируется последовательность коротких импульсов (фиг.2а)» моменты появления которых совпадают с передними фронтами входной последовательности импульсов или с момента перехода через ноль (при положительной производной) входного гармонического сигнала, а элемент 2 задержки осуществляет задержку этих импульсов. Время задержки выбирается таким, чтобы окон-35 чились переходные процессы в элемен- . тах схемы (фиг.2а,б).

Входное напряжение блока 3 интегрирования U (на N-м периоде слеыит. щ доваиия импульсов, фиг.2г) поступает 40 с выхода второго элемента 5 памяти.

Максимальное напряжение на выходе, блока 3 интегрирования (фиг.2в) в конце К-ro периода входного сигнала н 45

Ч

Плакс йнт. м с иит. где 1 — временной интервал между двумя импульсами; ми — постоянная интегрирования блока 3 интегрирования. 50

В момент времени С„ (фиг.2а) в первый элемент 4 памяти записывается U макс а в третий элемент 6 памяти U

На первый вход блока 8 вычитания поступает U. с выхода источника 7 опор" 55 о ного напряжения. Разностное напряжение

32 2 с выхода блока 8 вычитания поступает на первый вход перемножителя 9, на второй вход которого поступает напряжение с выхода делителя 10 напряжений, равное

4 Э

Таким образом, напряжение на выходе перемножителя 9 н

Это напряжение поступает на первый вход сумматора 11, на второй вход которого поступает напряжение с выхода третьего элемента 6 памяти. На вход второго элемента 5 памяти поступает напряжение

U=-U+U-=U инт инт и инт.й Чм.н о

В момент времени „. блок 3 интегрирования устанавливается в "0", нал пряжение Ч„„„ „+, " запоминается во втором элементе 5 памяти и поступает на информационный вход блока 3 интег рирования. Предполагая, что „ =7@„ получим, что по окончании (0+1)-.го периода U „, =U, . Таким образом, мсцсс Ч+7 о при условии чтот.„ 7 +,, на выходе блока 3 интегрирования будет действовать пилообразное напряжение, у ко. торого U„ = U, . Это напряжение макс сравнивается в блоке 12 компараторов

11ь с М порогами Б 0 U

М

2По . (М Ц> о

U = — ---- и на выхода

M "к М блока 12 компараторов появляются импульсы, которые на выходе многовходового сумматора 13 образуют периодическую последовательность импульсов с частотой следования f- M, где f— частота входного сигнала. Полосовой фильтр 14 необходим для получения сигнала синусоидальной формы на выходе умножителя частоты.

Формула изобретени

Умножитель частоты, содержащий последовательно соединенные блок интегрирования, блок компараторов и многовходовый сумматор, формирователь иьшульсов и полосовой фильтр, отличающийся тем,. что, с целью повышения точности умножения частоты, введены последовательно соединенные первый элемент памяти, блок вычитания, перемножитель, сумматор;

1298832

/Ч+ 7 -ф период и-й период а

И-7-и период

Составитель Ю.Максимов

Редактор В. Петраш Техред М.Моргентал Корректор А.Зимокосов

Заказ 894/55 Тираж 902 Подписно е

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.ужгород,ул.Проектная,4 второй элемент памяти и третий элемент памяти, делитель напряжений, источник опорного напряжения, элемент задержки, вход которого объеди.нен с входом записи первого и третье- 5 го элементов. памяти и соединен с выходом формирователя импульсов, а выход элемента задержки соединен с входом записи второго элемента памяти и входом сброса-блока интегрирования, 10 сигнальный вход которого объединен с первым входом делителя напряжений и соединен с выходом второго элемента памяти, выход блока интегрирования соединен с информационным входом первого элемента памяти, выход которого соединен с вторым входом делителя напряжений, выход делителя напряжений соединен с вторым входом перемножителя, выход третьего элемента памяти соединен с вторым входом сумма— тора, выход источника опорного напряжения соединен с вторым входом блока вычитания, выход многовходового сумматора соединен с входом полосового фильтра.