Синхронный делитель частоты по модулю 2 @ -1

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в трактах деления частоты. Цель изобретения - повьппение быстродействия при одновременном расширении функциональных возможностей за счет организации сигнала Перенос. Для достижения поставленной цели fe устройстве каждый из N триггеров 1.1- 1.N вьтолнен в виде 1К-триггера и образованы новые функциональные связи. В случае необходимости получения дополнительного четного коэффициента деления с симметричным выходным сигналом это осуществляется путем подключения I- и К-входов дополнительного (N+l)-ro триггера к прямому, выходу триггера 1.N и соединением их С-входов. 2 ил. (С (Л Фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

Д И Ц р

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ДВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ФигЛ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (2l) 3974588/24-21 (22) 10.11 .85 (46) 23.03.87. Бюл, Ф ll (72) И.В ° Колосов и А.В. Колосов, (53) 621.374.4(088.8) (56) Гутникав В,С. Интегральная электроника в измерительных устройствах.-JI,: Энергия, Ленинград. отд.

1980, с. 208, рис. 13-2,б.

Авторское свидетельство СССР

Р 762206, кл. Н 03 К 23/54, 20.04,77. (54) СЙНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИО

МОДУЛЮ 2N-1 (57) Изобретение относится к имнульсной технике и может быть использовано в трактах деления частоты. Цель

„.Я0„„1298903 А 1 изобретения — повышение быстродействия при одновременном расширении функциональных возможностей за счет организации сигнала Перенос". Для достижения поставленной цели в устройстве каждый иэ М триггеров 1 ° 11.N выполнен в виде IK-триггера и образованы новые функциональные связи.

В случае необходимости получения дополнительногo четного коэффициента деления с симметричным выходным сигналом это осуществляется путем подключения ?- и К-входов дополнительного (И+1)-ro триггера к прямому . выходу триггера 1.N и соединением их С-входов. 2 ил.

98903

1 12

Изобретение относится к импульсной технике и может бьггь использовано в трактах деления частоты, например, в вычислительной технике, цифровых синтезаторах частот.

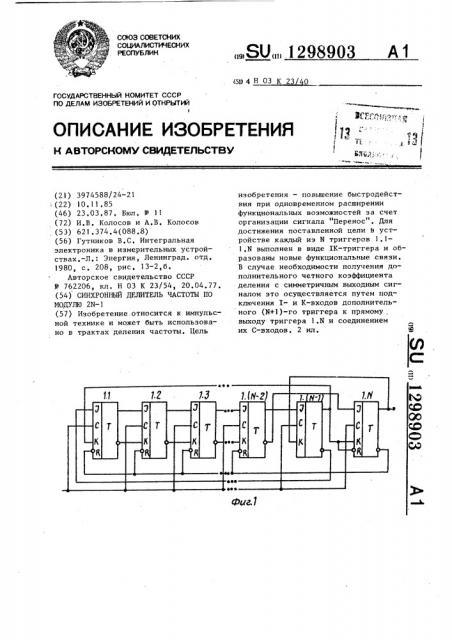

Цель изобретения — повышение быстродействия при одновременном расширении функциональных возможностей за счет организации сигнала "Перенос", На фиг. 1 приведена электрическая функциональная схема синхронного делителя частоты по модулю 2N-I-, на фиг. 2 — временная диаграмма, поясняющая работу устройства (при N=5).

Синхронный делитель частоты по модулю 2N-1 содержит N триггеров

1.1, 1,2, 1,3, ..., 1,(N-2), 1.(N-I), 1.N IK-типа, тактовые входы которых соединены с входной шиной, прямые и инверсные выходы каждого предыдущего (в группе от первого до (N-2)-ro) триггера соединены соответственно с

I- и К-входами каждого последующего триггера, образуя региСтр сдвига.

R-входы укаэанных триггеров соединены с инверсным выходом И-ro триггера

1 И,, прямой выход которого соединен с К-входом (N-1)-го триггера, 1.(N-1)-й инверсный выход которого соединен с I-входом первого триггера 1.1, К-вход которого соединен с прямым выходом (N-1)-го триггера 1,(N-1) и с К- и R-входами N-ro триггера 1.N;

I-вход N-го григгера 1.N соединен с инверсным выходом (И-2)-го триггера

1.(N-2), прямой выход которого соединен с I-входом (N-l)-ro триггера

1.(N-1).

Синхронный делитель частоты по модулю 2N-1 (при N=5) работает следующим образом.

На тактовые входы всех триггеров поступают импульсы с частотой F (фиг. 2а). Пусть в исходном состоянии на их выходах имеются уровни логического нуля. Тогда спадом первого тактового импульса в единичное состояние переключается (фиг. 2б) триггер 1.1. Далее спадом второго, третьего и четвертого тактовых импульсов в единичное состояние переключаются триггеры 1.2, 1.(N-2), 1.(И-1) соответственно (фиг. 2в, г, д) а спадом пятого, шестого и седьмого тактовых импульсов в нулевое состояние переключаются триггеры 1.1 1.2, 1.(N-2) соответственно ° При этом по спаду восьмого тактового импульса тРиггер 1,(N-l) сохраняет предыдущее единичное состояние, поскольку на

его I- и К-входах в этот момент имеются уровни логического нуля с. прямого выхода триггера l,(N-2) и с прямого выхода триггера 1.N. Триггер 1.N в этот момент переключается в единичное состояние (фиг, 2е) поскольку íà его I- и К-входах присутству1О ют уровни логических единиц с инверсного выхода триггера 1.(И-2) и с прямого выхода триггера 1.(N-1). Спадом девятого тактового импульса триггер 1.(N-1) переключается в нулевое состояние, поскольку на его

I- и К-входах в этот момент присутствуют уровни логического нуля и единицы соответственно с прямого выхода триггера 1.(N-2) и с прямого выхода триггера 1.N. Одновременно в противоположное, т ° е. нулевое, состояние переключается триггер 1.N поскольку на его I- и К-входах присутствуют уровни логических единиц с инверсного и прямого выходов триггеров 1.(N-2) и 1.(N-1) соответственно, которое удерживается уровнем логического нуля с выхода триггера

1.(N-l) по R-входу до переключения триггера 1.(N-1) в единичное состояние. На каждом периоде тактовых импульсов импульс с инверсного выхода триггера 1.И устанавливает (в случае сбоев) первые N-2 триггеры, в данном

Ç5 случае триггеры 1.1, 1.2, 1.(N-2), в нулевое состояние, либо подтверждает их нулевое состояние, В случае необходимости получения дополнительного четного коэффициента деления с симметричным выходным сигналом это осуществляется путем подключения I- и К-входов дополнительного (И+1)-ro триггера к прямому выходу триггера 1.N и соединением их

С-входов.

Формула изобретения

Синхронный делитель частоты по модулю 2N-1, содержащий N триггеров, тактовые входы которых соединены с входной шиной, инверсный выход N- ro триггера соединен с R-входом первого триггера, который совместно с триггерами с второго по (N-2)-й, R-входы которых соединены между собой, образуют регистр сдвига, о т л и ч а юшийся тем, что,. с целью повыше1298903

Составитель А. Соколов

Редактор A. Козориз Техред М.Ходанич Корректор Л. Патай

Заказ 898/59 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раутская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 ния быстродействия при одновременном расширении функциональных возможностей, каждый из N триггеров выполнен в виде IK-триггера, причем прямой выход (N-2)-го триггера соединен с

1-входом (N-1)-го триггера, инверсный выход — с I-входом N-го,триггеб д г д

8 ра, инверсный выход которого соединен с R-входом второго триггера, прямой выход — с К-входом (N-1)-го триггера, инверсный выход которого соединен с

I-входом первого триггера, прямой выход — с К-входом первого триггера и с К- и R-входами N-го триггера,