Преобразователь двоичного кода в биполярный код

Иллюстрации

Показать всеРеферат

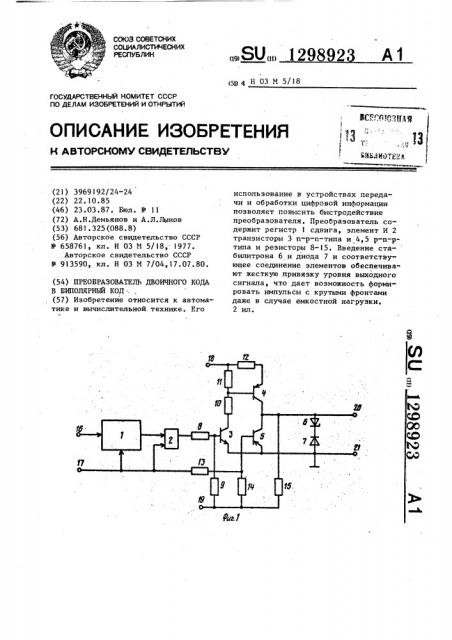

Изобретение относится к автоматике и вычислительной технике. Его использование в устройствах передачи и обработки цифровой информации позволяет повысить быстродействие преобразователя. Преобразователь содержит регистр 1 сдвига, элемент И 2 транзисторы 3 п-р-п-типа и 4,5 р-п-ртипа и резисторы 8-15. Введение стабилитрона 6 и диода 7 и соответствующее соединение элементов обеспечивают жесткую привязку уровня выходного сигнала, что дает возможность формировать импульсы с крутыми фронтами даже в случае емкостной нагрузки. 2 ил. /7 fr (Л О ISD со оо со ts5 СО П П/. ПГ5

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„SU, 129892 (д1) 4 Н 03 M 5/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ фС лРf @+11Àß

I > „,13

1 еЯЬ .1 МОТЯ",2А

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н А ВТОРСМОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3969192/24-24 (22) 22.10.85 (46) 23.03.87. Бюл. Ф 11 (72) А.Н.Демьянов и А.Л.Лыков (53) 681.325(088.8) (56) Авторское свидетельство СССР

И 658761, кл. Н 03 И 5/ 18,. 1977.

Авторское свидетельство СССР

9 913590 кл. Н 03 М 7/04,17,07.80. (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА

В БИПОЛЯРНЫЙ КОД,, (57) Изобретение относится к автоматике и вычислительной технике. Его использование в устройствах передачи и обработки цифровой информации позволяет повысить быстродействие преобразователя. Преобразователь содержит регистр 1 сдвига, элемент И 2 транзисторы 3 и-р-п-типа и 4,5 р-п-ртипа и резисторы 8-15. Введение стабилитрона 6 и диода 7 и соответствующее соединение элементов обеспечивают жесткую .привязку уровня выходного сигнала, что дает возможность формировать импульсы с крутыми фронтами даже в случае емкостной нагрузки.

2 ил.

15

1 12989

Изобретение относится к автоматике и вычислительной технике и может быть использовано в „.стройствах передачи и обработки цифровой информа, ции. 5

Цель изобретения — повышение быстродействия преобразователя, На фиг. 1 изображена принципиальная схема преобразователя, на фиг.2 диаграммы, поясняющие его работу. 10

Преобразователь двоичного кода в биполярный код содержит регистр 1 сдвига, элемент И 2, транзистор 3 п-р-п-типа, первый и второй транзисторы 4 и 5 р-п-р-типа, стабилитрон б, диод 7, первый-восьмой резисторы 8-15, а такх<е информационный и тактовый входы 16 и 17„ пины

18 и 19 положительного и отрицательного напряжений источника питания, 20 первый и второй выходы 20 и 21.

Двоичный код с входа 16 при наличии тактовых импульсов (фиг. 2<<) на входе 17 заносится в регистр 1 сдвига. При наличии на выходе реги- 25 стра 1 единичного сигнала (фиг. ?6) с элемент И 2 открывается по тактово- му импульсу (фиг. 2<1). При этом отпираются транзисторы 3 и 4 (на фиг. 2 г)показан сигнал на базе тран- 30 эистора 3) и плюсовая шина 18 подключается к выходу 20. В отсутствие единичного сигнала с. выхода регистра 1 на время действия тактового импульса все транзисторы 3-5 закрыты и на выходе 20 присутствует отрицательный потенциал, определяемый цепью параметрической стабилизации напряжения на элементах 6, 7 и 15.

При отсутствии тактовых импульсов открывается транзистор 5 (на фиг.2g паказрн сигнал на ега базе) и выход

20 закорачивается с выходом 21. Б результате на выходе 20 формируется биполярный сигнал (фиг. 2е).

Таким образом, жесткая привязка сигнала в паузе межцу тактовыми импульсами обеспечивает формирование импульсов с крутыми фронтами, что особенно важно при емкостном характере нагрузки (например, длинные линии), о р м у л а и з обретения

Преобразователь двоичного кода в биполярный код, содерх<ащий регистр сдвига, выход которого соединен с первым входом элемента И, выхад каторога через первый резистор подключен к базе транзистора и-р-и-типа и первому выводу второго резистора, первый транзистор р-п-р-типа, база которого соединена с первыми выводами третьего и четвертого резисторов, эмиттер подключен к первому выводу пятого резистора, второй транзистор р-п-р-типа, шестой резистор, первый вывод каторага объединен с первым выводом седьмого резистора, и восьмой резистор, вторые выводы четвертого и пятого резисторов подключены к шине полах<ительнаго потенциала источника питания, вторые выводы второго и седьмого резисторов подключены к пине отрицательнога потенциала и" òî÷íèêà питания, информационный вход регистра сдвига является информационным входом преобразователя, тактовый вход регистра сдвига и второй вход .элемента И объединены и являются тактовым входом преобразователя, коллектор первого транзистора р-и-р-типа объединен с первым выводом восьмого резистора и является первым выходом преобразователя, второй выход преобразователя соединен с шиной нулевого потенциала, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия преобразователя, в него введены диод и стабилитрон, катоды которых объединены, коллектор транзистора и-р-и-типа подключен к второму выводу третьего резистора, база второго транзистора р-пр-типа подключена к объединенным первым выводам шестого и седьмого резисторов, второй вывод шестого резистора подключен к тактовому входу преобразователя, второй вывод восьмого резистора соединен с пинай отрицательного потенциала источника питания, коллектор второго транзистора р-и-р-типа и анод стабилитрона объединены и подключены к первому выходу преобразователя, эмиттера транзистора > â р-< †ти и второго транзистора р-< — р-типа объединены с анодом диода и подключены к второму выходу преобразователя.

12ц8923

Фиг. Z

Составитель О. Ревинский

Редактор Л.Гратилло Техред М.Ходанич

Корректор С.Черни

Заказ 899/60 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делан изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4