Устройство для передачи и приема дискретной информации

Иллюстрации

Показать всеРеферат

Изобретение относится К радиотехнике . Цель изобретения - повышение достоверности приема дискретной информации. Устр-во содержит на передающей стороне вычитающий счетчик 1, дешифратор 2, элемент ИЛИ 3, регистр сдвига 4 с цепью обратной связи , блок задержки 5, блок совпадения 6, инвертор 7 и триггер 8, а на приемной стороне - регистр сдвига 9 с цепью обратной связи, сумматор 10 по модулю два, блок сравнения 11, триггер управления 12, блок 13 сумматоров по модулю два, элементы И 14, ИЛИ 15, суммирующий счетчик 16, промежуточный накопитель 17, инверторы 18, 19, счетчики 20, 21, блоки задержки 22, 23, элементы ИЛИ 24-26. Блок сравнения 11 состоит из сумматоров 27, 28, элемента ИЛИ 29 и инвертора 30. Введением блоков 13, 19, 2,1, 23-26 устраняется явление обратной работы, в результате чего повышается достоверность приема. 1 нл. i СЛ г кэ

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

O9) <И>

А2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 642867 (21) 3925705/24-09 (22) 08.07.85 (46) 23.03.87. Бюл. К - 11 (71) Гродненский государственный университет (72) В.Н.Сюрин (53) 621.394 ° 14 (088.8) (56) Авторское свидетельство СССР

У 642867, кл. Н 04 L 17/00, 1976..(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА

ДИСКРЕТНОЙ ИНФОРИАЦИИ (57) Изобретение относится к радиотехнике. Цель изобретения — повышение достоверности приема дискретной информации. Устр-во содержит на передающей стороне вычитающий счетчик

Sg 4 Н 04 1. 17/00 Н 03 М 5 00

1, дешифратор 2, элемент ИЛИ 3, регистр сдвига 4 с цепью обратной связи, блок задержки 5, блок совпадения

6, инвертор 7 и триггер 8, а на приемной стороне — регистр сдвига 9 с цепью обратной связи, сумматор 10 по модулю два, блок сравнения 11, триггер управления 12, блок 13 сумматоров по модулю два, элементы И 14, ИЛИ

15, суммирующий счетчик 16, промежуточный накопитель 17, инверторы 18, 19, счетчики 20, 21, блоки задержки

22, 23, элементы ИЛИ 24-26. Блок сравнения 11 состоит из сумматоров 27, 28, элемента ИЛИ 29 и инвертора 30.

Введением блоков 13, 19, 2,1, 23-26 устраняется явление обратной работы, в результате чего повышается достоверность приема. 1 ил.

1 1298942 2

Изобретение относится к радиотехнике, может быть использовано для передачи дискретных сообщений с высокой скоростью и достоверностью и является усовершенствованием изобретения по авт, св. 9 642867.

Целью изобретения является повышение достоверности приема дискретной информации.

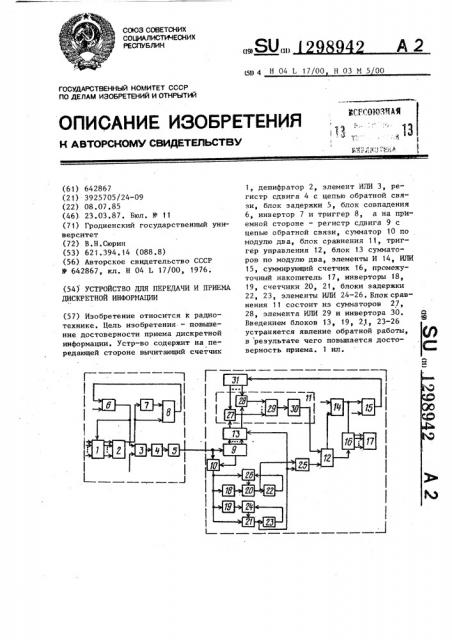

На чертеже приведена структурная >0 электрическая схема устройства для передачи и приема дискретной информации..

Устройство для передачи и приема дискретной информации содержит на передающей стороне вычитающий счет— чик 1, дешифратор 2, элемент ИЛИ 3, регистр 4 сдвига с цепью обратной связи, блок 5 задержки, блок 6 совпадения, инвертор 7 и триггер 8, на 20 приемной стороне — первый регистр 9 сдвига с цепью обратной связи, сумматор 10 по модулю два, блок 11 сравнения, триггер 12 управления, блок

13 сумматоров по модулю два, элемент

И 14, элемент ИЛИ 15, суммирующий счетчик 16, промежуточный накопитель

17, инвертор 18, дополнительный инвертор 19, счетчик 20 и дополнительный счетчик 21, блок 22 задержки и дополнительный блок 23 задержки,первый, второй и третий дополнительные элементы ИЛИ 24-26, причем блок 11 сравнения состоит из сумматоров 27 и 28, элемента ИЛИ 29 и инвертора 30, 35 второй регистр 31 сдвига с цепью обоатной связи.

Устройство для передачи и приема дискретной информации работает сле- 0 дующим образом.

Рассмотрим случай отсутствия "обратной работы". По команде в вычитающий счетчик 1 параллельным кодом происходит запись комбинации перв-»чного кода. Если записанная комбинация отличается от нулевой, то на выходе дешифратора 2 появится нуль, который инвертируется инвертором 7 и устанавливает триггер 8 в состояние "1". Сигнал с выхода триггера Я поступает на вход блока 6 совпадения, который открывается и пропускает быстрые тактовые импульсы, частота следования которых не менее чем в »1раз превьппает номинальную частоту, где

N — выраженная в числе элементов длина комбинации вторичного кода, передаваемого в канал связи. Значение

И должно удовлетворят». неравенству и

N 2 -1, » n — длина комбинации первичного кода. Быстрые тактовые импульсы с выхода блока 6 совпадения поступают на счетный вход вычитающего счетчика 1 и параллельно через элемент ИЛИ 3 на. тактовыи вход регистра 4 сдвига. Быстрые тактовые импульсы подаются до тех пор, пока вычитающий счетчик 1 не установится в нулевое состояние. При этом сработает дешифратор 2 нулевого состояния, сигнал с выхода которого поступает на вход триггера 8 и устанавливает его в нулевое состояние, что приводит к закрытию блока 6 совпадения и прекращению поступления быстрых тактовых импульсов на счетный вход вычитающего счетчика 1 и на тактовый вход регистра 4 сдвига.

Таким образом, количество поступивших на регистр 4 сдвига быстрых тактовых импульсов зависит от того, какая комбинация первичного кода была записана в вычитающий счетчик 1.

Под действием этих быстрых тактов за время„ не превышающее периода номинальной тактовой частоты (длитель ности одной элементарной посылки), производится сдвиг фазы, формируемой в регистре 4 сдвига псевдослучайной последовательности (ПСП), на число шагов, равное десятичной цифре, соответствующей двоичной комбинации первичного кода. Под действием тактовых импульсов номинальной частоты, поступающих на вход элемента ИЛИ 3 и далее на тактовый вход регистра 4 сдвига, производится вь»дача в канал связи через блок 5 задержки ПСП с новой фазой.

Принимаемая из канала последовательность поступает на вход первого регистра 9 сдвига и на первый вход сумматора 10 по модулю два, на второй вход которого подается последовательность, формируемая первым регистром

9 сдвига. Если из канала поступает

ПСП, не содержащая ошибок, то с выхода сумматора 10 по модулю два через инвертор 18 на счетный вход счетчика 20 поступает последовательность нулей. При наличии в принимаемой последовательности зачетного участка длиной In+k (где k — емкость счетчика 20, n — количество разрядов первого регистра 9 сдвига), не содержа1298942 щего ошибок, происходит заполнение счетчика 20. В противном случае каждая единица с выхода сумматора 10 по модулю два поступает через элемент

ИЛИ 26 на вход "Сброс" счетчика 20 и, устанавливает его в исходное состояние, При заполнении счетчика 20 сигнал с его выхода через второй дополнительный элемент ИЛИ 25 поступает на установочный вход триггера 12 управления 10 в единичное состояние и через блок

22 задержки и элемент ИЛИ 26 на вход

"Сброс" счетчика 20 в исходное нулевое состояние.

Триггер 12 управления, установлен-15 ный в состояние "1", выдает сигнал с прямого выхода на вход элемента И 14, открывает его и через него начинают поступать быстрые тактовые импульсы на счетный вход суммирующего счетчи- 20 ка 16 и через элемент ИЛИ 15 на вход второго регистра 31 сдвига, где производится сдвиг ранее принятой ПСП относительно принимаемой. Сдвиг осуществляется до совпадения фаз указанных последовательностей, при этом на входах сумматоров 27 и 28 блока 11 сравнения имеют место одинаковые комбинации, поэтому на их выходах будут нули, на выходе элемента ИЛИ будет также нуль, который через инвертор

30 поступает на другой вход триггера

12 управления и устанавливает его в нулевое состояние. Сигнал с инверсного выхода триггера 12 управления 35 производит считывание показаний .суммирующего счетчика 16, Информационная комбинация с его выхода передается в промежуточный накопитель 17, обеспечивающий синхронную выдачу ин- 40 формации потребителю.

Показания суммирующего счетчика

16 представляют собой комбинацию первичного кода, введенную на передаче, которая выявляется на приеме путем подсчета числа шагов, на которое различаются фазы соседних последовательно передаваемых ПСП. После выдачи информации потребителю устройство на приемной стороне возвращается в исходное состояние.

При наличии "обратной работы" с выхода канала связи на первый регистр 9 сдвига поступает инвертированная последовательность, при этом если она не содержит ошибок, то с выхода сумматора 10 по модулю два на вход дополнительного счетчика 21 поступает серия единиц. При яаличии зачетного участка инвертированных, но безошибочных символов, происходит заполнение дополнительного счетчика

21, с выхода которого сигнал через второй дополнительный элемент ИЛИ 25 устанавливает триггер 12 управления в единичное состояние. Далее декодирование информационной комбинации производится так же, как и в предыдущем случае, с той разницей, что с выхода дополнительного счетчика 21 единичный сигнал подается на управляющий вход блока 13 сумматоров по модулю два, на выходах которого формируется инвертированная комбинация, т.е. устраняется явление "обратной работы". Любая ошибка в принимаемой последовательности вызывает появление нулевого сигнала на выходе сумматора 10 по модулю два, который через дополнительный инвертор 19 и первый дополнительный элемент ИЛИ 24 производит сброс дополнительного счетчика 21. При заполнении дополнительного счетчика 21 его сброс производится через дополнительный блок 23 задержки и дополнительный элемент ИЛИ 24.

Формула изобретения

Устройство для передачи и приема дискретной информации по авт. св.

Ф 642867, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности приема дискретной информации, на приемной стороне введены последовательно соединенные дополнительные инвертор, первый элемент ИЛИ, счетчик и блок задержки, а также второй и третий дополнительные элеменЪ ты ИЛИ и блок сумматоров по модулю два, при этом выход сумматора по мо- дулю два подключен к объединенным входам дополнительного инвертора и дополнительного счетчика, выход которого и выход счетчика подключены к единичному входу триггера управления через второй дополнительный элемент ИЛИ, выходы соответствующих разрядов первого регистра сдвига с цепью обратной связи подключены к соответствующим входам блока сравнения через блок сумматоров по модулю два, к управляющему входу которого подключен выход дополнительного счетчика, а выход сумматора по модулю два и выход блока задержки подключены к входу "Сброс" счетчика через третий дополнительный элемент ИЛИ.