Приемник сигналов модулированных одновременно по частоте и фазе

Иллюстрации

Показать всеРеферат

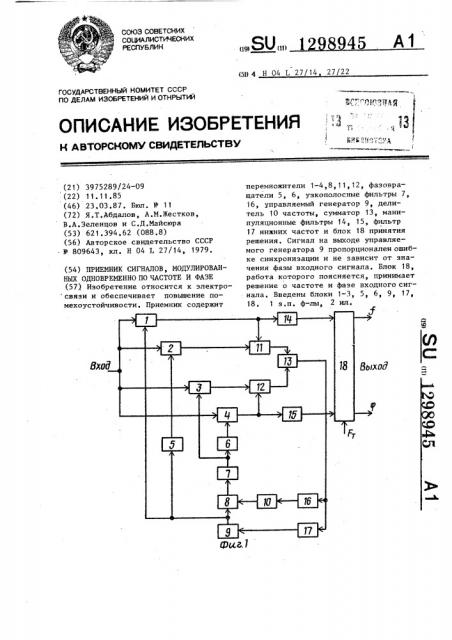

Изобретение относится к электросвязи и обеспечивает повьшение помехоустойчивости . Приемник содержит перемножители 1-4,8,11,12, фазовращатели 5, 6, узкополосные фильтры 7, 16, управляемый генератор 9, делитель 10 частоты, сумматор 13, манипуляционные фильтры 14, 15, фильтр 17 нижних частот и блок 18 принятия решения. Сигнал на выходе управляемого генератора 9 пропорционален ошибке синхронизации и не зависит от значения фазы входного сигнала. Блок 18, работа которого поясняется, принимает решение о частоте и фазе входного сигнала . Введены блоки 1-3, 5, 6, 9, 17, 18. 1 з.п. ф-лы, 2 ил. / Вход Выу-од ю со оо со NU сд Фаг./

СОЮЗ СОВЕТСКИХ

СОЯИАЛИСТИНЕСНИХ

РЕСПУБЛИК

5 А1 (д) 4 Н 04 L 27/14 27/22 ф,"гОръ х

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСИОМУ СВИДЕТЕЛЬСТВУ сриг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3975289/24-09 (22) 11. 11.85 (46) 23.03.87. Бюл, W - 11 (72) Я,Т,Абдалов, A.È.Æåñòêîâ, В.А.Зеленцов и С,Д.Майсюра (53) 621.394.62 (088.8) (56) Авторское свидетельство СССР

У 809643, кл. Н 04 1. 27/14, 1979, (54) ПРИЕМНИК СИГНАЛОВ, МОДУЛИРОВАННЫХ ОДНОВРЕМЕННО ПО ЧАСТОТЕ И ФАЗЕ (57) Изобретение относится к электро связи к обеспечивает повышение помехоустойчивости. Приемник содержит перемножители 1-4,8, 11, 12, фазовращатели 5, 6, узкополосные фильтры 7, 16, управляемый генератор 9, делитель 10 частоты, сумматор 13, манипуляционные фильтры 14, 15, фильтр

17 нижних частот и блок 18 принятия решения. Сигнал на выходе управляемого генератора 9 пропорционален ошибке синхронизации и не зависит от значения фазы входного сигнала. Блок 18 работа которого поясняется, принимает решение о частоте и фазе входного сигнала. Введены блоки 1-3, 5, 6, 9, 17, 18. 1 s.ë. ф-лы, 2 ил.

35

1 129894

Изобретение относится к электросвязи и может использоваться для при. ема сигналов с комбинированной частотой и фазовой модуляцией.

Цель изобретения — повьппение помехоустойчивости.

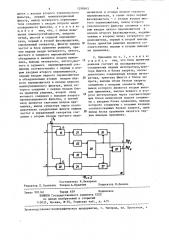

Ка фиг. 1 изображена структурная электрическая схема предложенного приемника; на фиг.2 - схема блока принятия решения.

Приемник содержит седьмой перемножитель 1, шестой перемножитель 2, пятый перемножитель 3, четвертый перемножитель 4, первый и второй фазовращатели 5 и 6, второй узкополосный !

5 фильтр 7, третий перемножитель 8, управляемый генератор 9, делитель 10 частоты, первый и второй перемножители 11 и 12, сумматор 13, первый и второй манипуляционные фильтры 14 и

15, первый узкополосный фильтр 16, фильтр 17 нижних частот, блок 18 принятия решения, состоящий из интеграторов 19 и 20, триггера Шмитта 21, блоков 22 и 23 вычисления модуля, триггера Шмитта 24, блока 2S сравнения, блоков 26 и 27 запрета и элемента ИЛИ 28.

Приемник работает следующим образом.

Пусть на вход устройства поступает входной сигнал

V — V cos(u;t + — ), где i = 1,2, Ьу =(;1 П, а управляемый генератор 9 вырабатывает опорный сигнал

V„ = Ч sin(Q,t+aq), 40

Где a(! — ошибка синхронизациИ, При поступлении на вход устройства сигнала с частотой а! на выходе перемножителя 1 получаем

V, V з1п(2ц(t+ «;+ а(у)+Ч sin(+ -a(g), а на выходе перемножителя 2 имеем

Ч Ч сов(2у, t+ y+a(g)+V cos(fy-a(1)),50

При этом ввиду отсутствия напряжения на первом входе перемножителя

8 (узкополосный фильтр 16 настроен на частоту 2a(a), а как следствие, и на опорных (вторых) входах перемножителей 3 и 4, отсутствуют сигналы и на выходах этих перемножителей.

5 2

На выходе перемножителя 1 имеем

Ч Ч -sin(4z,t+«+2ay)+V зю(+« — 2()(р)+

+2V sin(2и,t+7i)+2V sin(2и,t+2ь(1) .

На выходе фильтра 17 имеем

V4 U з п((-2a(p)=V sin 2ag т. е. сигнал на выходе управляемого генератора 9 пропорционален ошибке синхронизации и не зависит от значения фазы входного сигнала.

При помощи сигнала V< осуществляется подстройка управляемого генератора 9.

При поступлении на вход приемника сигнала с частотой (! на выходе пе2 ремножителя 1 получим

V, V sin((tt,+(t,)tt >+ttI)+

+ U sin(dQt + - -ag)

2 на выходе перемножителя 2

Vt V cos((ca, +u )t+ - +ttI) +

+ V cos(aut + — -щ)

II

2 на выходе перемножителя 11 имеем ч, -ч в1п(г(и,+и,) +г+гыр)+

+V з1п(24(Пй+ -2ь(р)+2Ч sin(2uzt+II)+

+2V sin(2u,t+2aq).

С помощью узкополосного фильтра

16 отфильтровываем напряжение с частотой 2a((1, которое после делителя 10 частоты на два поступает на первый вход перемножителя 8, на выходе ко-! торого получаем

Ч Ч cos((сд,-да)t+2a(fJ -V соя(гу .

С помощью узкополосного фильтра 7 отфильтровывается составляющая с частотой

Ч V созш,t.

На выходе перемножителя 4 имеем

Ч V злп(2(а й+ -)+Ч sin(+ -) .

На выходе перемножителя 12 имеем

V> - V sin (4ар+ () .

Принятие решения о частоте и фазе входного сигнала осуществляется в блоке 18 принятия решения.

При поступлении входного сигнала с частотой (а, на первом входе блока !

8 принятия решения имеем напряжение с выхода манипуляционного фильтра 14

1298945

3 л V sin(+ — -aq) !!

При этом напряжение на втором входе блока 18 отсутствует, т.е. V - О.

Р 5

По знаку напряжения V определяется фаза входного сигнала, а по результату сравнения V и V< принит Жг мается решение о том, что йа входе приемника присутствует сигнал с час- 10 тотой Ю, .

В случае поступления входного сигнала с частотой Q

° II

Ч,р О, а Vð V sin(+ 2) .

t5

По знаку напряжения V определяфг ется фаза входного сигнала а по ре(Р зультату сравнения. V u V приник! Рг мается решение о том, что частота 20 входного сигнала Q

Таким образом, если V V то т Фz принимается решение, что входной сигнал имеет частоту у,, а если V iU

9 Фа то принимается решение, что входной 25 сигнал имеет частоту цг.

Блок 18 принятия решения работает следующим образом. На его входы поступают напряжения с выхода манипуляционных фильтров 14 и 15. 30

Пусть входной сигнал имеет частоту (д,.

Тогда

Ч V sin(+ — -6(g)

9< 2

Ч,,-о.

С помощью интеграторов 19 и 20 производится интегрирование значений Ч, ф и V>

Период интегрирования определяет- 4О ся тактовыми импульсами частоты Р . и равен длительности единичного символа входного сигнала.

Принятие решения о частоте . вход- 45 ного сигнала производится с помощью блоков 22 и 23 вычисления модулей и блока 25. Для этого с помощью блоков

22 и 23 вычисляются модули напряжений на выходах интеграторов 19 и 20 и на блоке 25 производится их сравнение. При этом, если напряжение на первом входе блока 25 будет больше, чем на втором входе, что соответствует случаю, когда на входе имеется сигнал с частотой Ы<, то на первом выходе блока 25 появится положительный импульс, а на втором выходе— отрицательный импульс °

Положительный импульс с первого выхода блока 25 поступает на первый выход блока 18 принятия решения и выход устройства. Положительный импульс на первом выходе блока 18 принятия решения означает, что входной сигнал имеет частоту И, Если на втором входе блока напряжение окажется больше, чем на первом входе, то на ее первом выходе будет отрицательный импульс, а на. втором выходе — положительный импульс. Отрицательный импульс с первого выхо да блока 25 поступает на выход устройства и означает, что входной сигнал имеет частоту ц„ .

Принятие решения о фазе входного сигнала осуществляется с помощью триггера Шмитта 21 и блока 26 при поступлении входного сигнала с частотой с

< Ф с помощью триггера Шмитта 24 и блока

27 при поступлении входного сигнала с частотой Иг .

Это происходит следующим образом.

При поступлении входного сигнала с частотой Ы< на втором входе блока

2б будет положительный импульс, который открывает эту схему.

Знак напряжения на выходе интегратора 19 определяется с помощью триггера Шмитта 21. Если фаза входного сигнала равна "0", то на выходе триггера Шмитта 21 будет положительное о напряжение, если фаза равна 180 -— отрицательное напряжение. Это напряжение через открытый элемент ИЛИ 28 проходит на второй выход блока 18 принятия решения. На втором входе элемент ИЛИ 28 в этот момент сигнал отсутствует, так как блок 2? будет закрыт отрицательным импульсом с второго выхода блока 25.

Аналогично, при поступлении входного сигнала с частотой Я на выход блока 18 принятия решения с выхода триггера Шмитта 24 проходит напряжение, знак которого соответствует . фазе входного сигнала.

Формула изобретения

1. Приемник сигналов, модулированных одновременно по частоте и фазе, содержащий первый и второй перемножители, выходы которых соединены с входами сумматора, выход которого через последовательно соединенные первый узкополосный фильтр, делитель частоты и третий перемножитель сое1298945

Составитель Н.Лазарева

Редактор Й.Гратилло Техред А.Кравчук Корректор М, Демчик

Заказ 901/61 Тираж 639 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул, Проектная, 4 динен с входом второго узкополосного фильтра, первый манипуляционный фильтр, выход четвертого перемножителя соединен с входом второго манипуляционного фильтра, о т л и ч а юшийся тем, что, с целью повышения помехоустойчивости, введены пятый, шестой и седьмой перемножители, первый и второй фазовращатели, управляемый генератор, фильтр нижних 10 частот и блок принятия решения, причем первые входы четвертого, пятого, шестоГо и седьмого перемножителей объединены и являются входом приемника, выходы четвертого, пятого,шестого и седьмого .перемножителей соединены соответственно с первым и вторым входами второго перемножителя, первым входом первого перемножителя и объединенными вторым входом пер- 20 вого перемножителя и входом первого манипуляционного фильтра, выход которого соединен с первым входом блока принятия решения, второй вход которого соединен с выходом второго

25 манипуляционного фильтра, а третий вход является тактовым входом приемника, выход сумматора через последовательно соединенные фильтр нижних частот и управляемый генератор соединен .с вторым входом третьего перемножителя и вторым входом седьмого перемножителя, а также через первый фазовращатель — с втбрым входом шестого перемножителя, выход второго узкополосного фильтра соединен с вторым входом пятого перемножителя и входом второго фазовращателя, подключенным к второму входу четвертого перемножителя, первый и второй выходы блока принятия решения являются соответственно первым и вторым выходами приемника.

2. Приемник по п, 1, о т л и ч аю щ и и с, я тем, что блок принятия решения состоит из последовательно соединенных первых интегратора,триггера Шмитта и блока запрета, последовательно соединенных вторых интегратора, триггера Шмитта и блока запрета, выходы обоих блоков запрета соединены с входами элемента ИЛИ, выход которого является вторым выходом приемника, выходы первого и второго интеграторов через соответствующие блоки вычисления модуля соединены с входами блока сравнения, выходы которого соединены с вторыми входами соответствующих блоков запрета, один выход блока сравнения является первым выходом приемника.