Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть иснользовано при проектировании постоянных запоминающих устройств в интегральном исполнении . Целью изобретения является повышение быстродействия устройства. Для достиже)ия этой цели в устройство введены два дополнительных дифференциальных усилителя , проходные элементы и элементы предзаряда входов дифференциальных усилителей . Это позволило по сравнению с прототипом сократить цепь между выходами накопителя и входами дифференциальных усилителей за счет исключения из этой цели мультиплексора. Кроме того, для проходных элементов создан предпороговый режим работы , благодаря которому срабатывание дифференциальных усилителей происходит при меньшем, чем в нрототипе, перепаде выходного напряжения накопителя. 1 ил. ОО о о сд 05 О1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК д1) 4 G 11 C 17 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3879298/24-24 (22) 29.03.85 (46) 30.03.87. Бюл. № 12 (72) В. Б. Буй и А. Г. Солод (53) 681.327.66 (088.8) (56) Авторское свидете.чьство СССР № 841047, кл. G 11 С 17/00, 1981.

Авторское свидетельство СССР № 1!56139, кл. G 11 С 17/00, 1983. (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к области вычислительной техники и может быть использовано при проектировании постоянных запоминающих устройств в интегральном испол„„Я0„„1300565 А1 ненни. Целью изобретения является повыLIIt. Hèå быстродействия устройства. Для достижения этой цели в устройство введены два дополнительных дифференциа.чьных усилителя, проходные элементы и элементы предзаряда входов дифференциальных усилителей. Это позволило по сравнению с прототипом сократить цепь между выходами накопителя и входами дифференциальных усилителей за счет исключения из этой цели мультип.чексора. Кроме того, для проходных элементов создан предпороговый режим работы, благодаря которому срабатывание дифференциальных усилителей происходит при меныпем, чем в прототипе. перепаде выходного напряжения накопителя. 1 ил.

1300565

Изобретение относится к вычислительной технике и может быть использовано при проектировании постоянных запоминающих устройств в интегральном исполнении.

Цель изобретения — повышение быстродействия устройства.

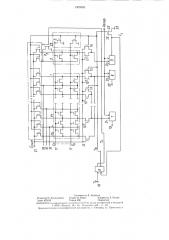

На чертеже приведена схема устройства.

Устройство содержит матричный накопитель 1, дополнительный накопитель 2, группу элементов 3 разряда, группу элементов 4 предзаряда, элемент 5 разряда дополнительного накопителя, триггер 6 обращения, первый 7, второй 8 и третий 9 дифференциальные усилители, группу проходных элементов 10, проходной элемент 11, первый 12, второй 13 и третий 14 элементы предзаряда, блокирующий элемент 15. Элементы разряда 3 и 5, предзаряда 4, 11, 12 и !3, проходные элементы 10 и блокирующий элемент 15 выполнены на МДПтранзисторах. На чертеже показаны также входы выборки первой 16 и второй 17 групп, вход 8 обращения, первый 19 и второй

20 информационные выходы, шины 21 питания, шина 22 опорного напряжения и шина 23 нулевого потенциала устройства.

Устройство работает следующим образом.

Исходное состояние триггера 6 обращения нулевое. На входах 17 и 18 нулевой уровень, на входах 16 — единичный уровень (-Е» =5В). Поскольку на инверсном выходе триггера 6 обращения единичный уровень, то элементы 4, 12, 3 и 14 предзаряда открыты и на всех вертикальных шинах матричного 1 и дополнительного 2 накопителей и на вторых входах дифференциальных усилителей 7, 8 и 9 единичный уровень. Опорное напряжение на шине 22 ниже, чем напряжение единичного уровня на вторых входах дифференциальных усилителей на значение чувствительности дифференциальных усилителей. Этому состоянию соответствуют нулевые значения на выходах 19 и 20. Чувствительность современных дифференциальных усилителей на

МДП-транзисторах составляет 0,1 В. Транзисторы элементов 12, 13 и 14 нредзаряда имеют встроенный канал, поэтому напряжение на вторых входах дифференциальных усилителей равно E -, а значение опорного напряжения на шине 22 равно Е

0,1 В. Элементы 4 предзаряда и проходные элементы 10 выполнены на МДП-транзисторах с индуцированным каналом. Поэтому значение напряжения на вертикальных линиях равно Е - 1,1 — В=3,9 В, а

МДП-транзисторы проходных элементов 0 находятся в предпороговом режиме, т. е. изменение напряжения на вертикальных шинах второй группы влечет соответствующее изменение потенциала на вторых входах дифференциальных усилителей.

При обращении к устройству на вход 18 подается короткий импульсный сигнал Т>, который формируется при переключении лю5

55 бого из адресных сигналсв (на чертеже схема выработки сигнала Т не показана).

Спад сигнала Т. .происходит не ранее, чем произойдет переключение последнего по времени адресного сигнала. По спаду сигнала Т> формируется положительный фронт сигнала на прямом выходе триггера обращения 6 Т, а затем спад сигнала на инверсном выходе триггер;. обращения Т,.

По спаду сигнала Tv формируется фронт сигнала на выбранной горизонтальной шине накопителей 5, на выбранной вертикальной шине первой группы L матричного накопителя 1 и на первой шине дополнительного накопителя 2. Разряд последней производится через элемент 5 разряда.

В накопитель 1 записывается информация заказчика, а в накопитель 2 — единичная информация. Запись информации осуществляется путем изменения в процессе изготовления значения порогового напряжения транзисторов связи накопителей 1 от нормального, равного -1 В и соответствующего коду единица, до уровня, превыц1ающего максимальное на.пряжение на горизонтальной шине и соответствующего коду ноль. Все транзисторы связи накопителя 2 имеют нормальное значение порогового напряжения, При достижении на выбранной горизонтальной шине значения порогового напряжения начинается разряд вертикальных шин второй группы Pi и Р, связанных с выбранной вертикальной шиной L первой группы матричного накопителя, если соответствующие транзисторы связи имеют нормальное значение порогового напряжения, и второй вертикальной шиной дополнительного нако п ител я.

При этом изменяется потенциал на вторых входах дифференциальных усилителей и на выходах последних устанавливается значение единицы (если соответствующие транзисторы связи имели нормальное значение порогового напряжения). Быстродействие устройства повышено благодаря исключению из цепи между выходом накопителя и входом дифференциального усилителя мульти плексора и постоян ной готовности дифференциальных усилителей к приему информации благодаря работе проходных элементов в предпороговом режиме.

Дифференциальный усилитель 9 срабатывает позже, чем дифференциальные усилители 7 и 8, благодаря тому, что дополнительный накопитель располагается в конце горизонтальной шины матричного накопителя и подъем напряжения на горизонтальной шине накопителя 2 происходит не раньше, чем на горизонтальной шине накопител я 1.

При срабатывании дифференциального усилителя 9 формируется фронт сигнала FI,.

Этот сигнал используется для разрешения

1300565 записи в триггеры сигналов с выходов дифференциальных усилителей 7 и 8 (триггеры не показаны), а также для сброса триггера 6 обращения. При сбросе триггера обращения сначала устанавливается низкий уровень на прямом выходе, а за тем высокий уровень на инверсном выходе. При этом производится заряд ранее выбранных вертикальных шин (через элементы 4 предзаряда), разряд ранее выбранной горизонтальной шины (через элемент 3 разряда), а также заряд вторых входов дифференциальных усилителей 7 — 9 (через элементы предзаряда 12, 13 и 14). Таким образом, устройство подготавливается к следующему циклу обращения.

Формула изобретения

Постоянное запоминающее устройство, содержащее матричный накопитель, вертикальные шины первой группы и горизонтальные шины которого являются соответственно входами выборки первой и второй групп устройства, дополнительный накопитель, группу элементов разряда, каждый из которых выполнен на МДП-транзисторе, сток которого подключен к соответствующей горизонтальной шине матричного и дополнительного накопителей, а исток — к шине нулевого потенциала устройства, группу элементов предзаряда, каждый из которых выполнен на МДП-транзисторе, исток которого подключен к соответствующей вертикальной шине матричного и дополнительного накопителей, а сток — к шине питания устройства, элемент разряда дополнительного накопителя, выполненный на МДП-транзисторе, сток которого подключен к первой вертикальной шине дополнительного накопителя, а исток — к шине нулевого потенциала устройства, триггер обращения, единичный вход которого является входом обращения устройства, инверсный выход подключен к затворам МДП-транзисторов группы элементов разряда и группы элементов предзаряда, а прямой выход — к затвору МДПтранзистора элемента разряда дополнительного накопителя, первый дифференциальный усилитель, первый вход которого подключен к шине опорного напряжения устройства, а выход является первым.информационным выходом устройства, отликакт«еся тем, что, с целью повышения быстро10 действия устройства, в него введень: второй и третий дифференциальные усилители. iiepвые входы которых соединены с первым входом первого дифференциального усилится», а выход второго дифференциального усилителя является вторым информационным пы15 ходом устроиства, группа Ilpoxoäíûi элi меllтов, каждый из которых выполнен на М i,(1транзисторе, исток которого подключеll к соответствующей вертикальной шине вгорой группы матричного накопителя, стоки нечетных и четных МДП-транзисторов группы проходных элементов соединены соответ TBcHно с вторыми входами первого н второго дифференциальных усилителей, проходной элемент, выполненный на МДП-транзисторе, исток которого подключен к второй верти25 кальной шине допочнитечы ого накопителя, а сток — к второму входу третьего дифференциального усилителя, затворы МД11транзисторов всех проходных элементов соединены с шиной питания, первый, второй и третий элементы rrpeдзаряда, каждый нз которых выполнен на МДП-транзисторе, исток которого подключен к второму входу соответствующего дифференциального усил и теля, сток — к шине питания устройства, а затвор — к инверсному выходу триггера опроса, блокирующий элемент, выполненный на МДП-транзисторе, сток которого подключен к выходу третьего дифференциального усилителя и к входу сброса триггера обращения, исток — к шине нулевого потенциала устройства, а затвор — к инверсному выходу триггера обращения.

1300565

Составитель А. Дерюгин

Редактор Н. Киштулинец Текред И. Верее Корректор A. Ильин

Заказ 829/52 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж вЂ” -35, Раушская наб., д. 4/5

Производственно-полиграфическое предприя гие, г. Ужгород, ул. Проектная, 4