Устройство для имитации сбоев цифровых вычислительных машин

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для отладки и испытаний nporpahiM специализированных ЦВМ. Целью изобретения является расширение функциональных возможностей за счет управления типом и интенсивностью сбоев. Устройство содержит три блока элементов И 1, 10 и 11, блок элементов ИЛИ 14, генератор 9 случайных чисел, одноразрядный блок 4 памяти, наладочный блок 2 памяти , генератор 5 управляемых сбоев, два инвертора 8 и 13 и делитель 12, содержащий счетчик и элемент ИЛИ. 2 ил. N) фиг 1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

09) (И) А2 ф(р э ф

1г

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ASTOPCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 879592 (21) 3915481!24-?4 (22) 28.06.85 (46) 30.03.87. Бюл. Н- 12 (72) Н. Б. Парамонов и А.B. Александров (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 879592, кл. Н 03 M 13/02, 1980. (54) УСТРОЙСТВО ДЛЯ ИМИТАЦИИ СБОЕВ

ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН (57) Изобретение относится к области автоматики и вычислительной техники (м 4 Н 03 И 13/02 С 06 Г 11/00 и может быть использовано для отлад-. ки и испытаний программ специализированных ЦВИ, Целью изобретения является расширение функциональных возможностей за счет управления типом и интенсивностью сбоев. Устройство содержит три блока элементов И 1, 10 и 11, блок элементов ИЛИ 14, генера" тор 9 случайных чисел, одноразрядный блок 4 памяти, наладочный блок 2 памяти, генератор 5 управляемых сбоев, два инвертора 8 и 13 и делитель 12, содержашнй счетчик и элемент ИЛИ.

2 ил, 13006

Устройство работает следующим образом.

В одноразрядном БП 4 помечаются"1", т.е. команды и данные программы, при обращении к которым допустимо формирование сбоя ЦВМ. Сигналом на- 40 чальной установки триггер 7 и делитель 12 устанавливаются в исходное состояние. При считывании содержимого помеченной ячейки наладочного БП

2 иэ одноразрядного БП 4 считывается

"1", которая поступает на генератор

5 управляемых сбоев и делитель 12.

Сбой ЦВМ имитируется тем, что из БП

2 в ЦВМ 3 поступает не содержимое опрашиваемой ячейки БП 2, а случайный код с генератора 9 случайных чисел . Причем сбойный код будет проходить на каждой k-й меченой команде (данных), считываемой из наладочного

БП 2. Делитель 12 пропускает на выход

k-й импульс меченой команды, изменение k происходит изменением коммутации начального устанава счетчика 16.

Триггер 7 предназначен для борьбы с

Устройство относится к вычислительной технике и может быть использовано для проверки устойчивости к сбоям программ управляющих ЦВМ, имеющих средства аппаратурнаго контроля и программную защиту иа участках (называемых далее защищенными блоками), и является усовершенствованием авт, авт.cs. к 879592.

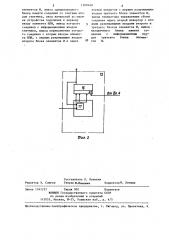

Целью изобретения является расши- 10 реиие фрикционных возможностей устройства эа счет управления интенсивностью и типом потока сбоев, На фиг. 1 приведена схема устройства для имитации сбоев ЦВМ; на фиг, фиг. 2 - схема делителя.

Устройство (фиг. 1) содержит пер; вый блок 1 элементов И, наладочный блок 2 памяти (БП), ЦВМ 3, одноразрядный блок 4 памяти (БП), генератор 20

5 управляемых сбоев, содержащий элемент И-НЕ 6 и триггер 7, второй инвертар 8, генератор 9 случайных чисел, второй 10 и третий 11 блоки эле— ментов И, делитель 12, первый инвер25 тор 13 блок 14 элементов ИЛИ, вход

15 начальной установки устройства (количества элементов И, ИЛИ в блоках и разрядность кода, снимаемого с генератара случайных чисел, определяет- 30 ся разрядностью ЦВМ); Делитель 12 (фиг. 2) содержит счетчик 16 и элемент ИЛИ 17.

48 зацикливанием короткого участка программы при защите его повторным выполнением. Он иСпользуется в случае, когда создают максимальный поток сбоев, и не позволяет сделать k = 1.Синхронная рабата (исключение влияния триггера 7 при k = 2,4...) осуществляется начальной установкой триггера

7 и счетчика 16, Г енератор 9 случайных чисел выдает случайный код при каждом обращении ЦВМ 3 к наладочному

БП 2. Эта достигается тем, что код адреса, передаваемый из ЦВМ в БП, содержит разряд определения операции (запись, считывание), сигнал считывания, поступая на вход пуска генератора 9 случайных чисел, разрешает выдать на выход генератора 9 очередной случайный двоичный код. Этот код проходит через блок 10 элементов И только в том случае, когда есть разрешение от генератора 5 управляемых сбоев (на выходе элемента И-НЕ 6 сигнал "0", на выходе инвертора 8—

"1") и делителя 12 (на его выходе

" 1 ). В противном случае в ПВМ 3 передается информация, считанная из

БП 2.

Таким образом, устройство позволяет расширить возможности устройства за счет возможности управления интенсивностью и типом потока ЦВМ, в результате чего имеются более широкие возможности для проверки устойчивости к сбоям программ управляющих ЭВМ, имеющих средства программной и аппаратной защиты.

Формула изобретения

Устройство для имитации сбоев цифровых вычислительных машин по авт.св.

В 879592, о т л и ч а ю щ.е е с я тем, что, с целью расширения функциональных возможностей за счет управления интенсйвностью и типом потока сбоев, устройство содержит генератор случайных чисел, второй и третий блоки элементов И, первый и второй инверторы, счетчик, элемент ИЛИ и блок элементов ИЛИ, причем выходы с первого по третий блоков элементов И соединены соответственно с первого по третий входами блока элементов

ИЛИ, выход которого является выходом устройства, вход устройства подключен к входу пуска генератора случайных чисел, выход которого соединен с информационным входом второго блока

1300648

ЩФ. 2

Составитель JT.. Ванюхин

РедактоР Э. Слиган ТехРед И.Попович Корректор М. Лемчик

Заказ 1161/57 Тира к 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений н открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ущгород, ул. Проектная, 4. элементов И, выход одноразрядного блока памяти соединен со счетным входом счетчика, вход начальной ус ановки устройства подключен к первому входу элемента ИЛИ, выход которого соединен с информационным входом счетчика,. выход переполнения которого соединен с вторым входом элемента ИЛИ,-с первым разрешающим входом второго блока элементов И и через первый иквертор с первым разрешающим входом третьего блока элементов И, выход генератора управляемых сбоев соединен через второй инвертор с вторыми разрешающими входами второго и третьего блоков элементов И, выход;. наладочного блока памяти соединен с информационным входом третьего блока элементов И.