Программируемый логический контроллер

Иллюстрации

Показать всеРеферат

Изобретение относится к устройствам для программно-логического управления объектами дискретного циклического действия. Целью изобретения : является повьшение быстродействия. Программируемый логический контроллер содержит генератор 11 импульсов, счетчики 6 и 13 импульсов, блоки 3,4,9 и 10 памяти, элементы И 5 и 12, блоки 2 и 8 сравнения, элемент 2И-ШШ 7 и блок 1 индикации. В качестве датчиков состояний и условий переходов могут быть использованы как датчики, устанавливаемые на механизмах, так я органы управления и защиты, сигналы управления информационных и электрических блокировок от других устройств. Сочетание в данном устройстве режима сканирования при анализе комбинаций состояний датчиков условий переходов (состояние внешней среды) и методе пошаговой отработки подпрограмм управления хщклами работы механизмов позволяет компоновать любые последователь- СО со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1302242 (50 4 G 05 В 19/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР пО делАм изОБРетений и ОтнРытий (21) 3999363/24--24 (22) 30.12.85 (46) 07.04.87, Бюл. № 13 (71) Всесоюзный научно-исследовательский и проектно-конструкторский институт технологии электромашинострое1 ния (72) Б.ДеНовожилов и И.АаФурман (53) 621. 503 ° 55 (088. 8) (56) Унифицированная логическая система .управления механизмами УПМ-2.

Техническое описание. Кировоград, 1977.

Авторское свидетельство СССР № 857933, кл. G 05 В 19/18, 1979. (54) ПРОГРАИИИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР (57) Изобретение относится к устройствам для программно-логического управления объектами дискретного циклического действия. Целью изобретения является повышение быстродействия.

Программируемый логический контроллер содержит генератор 11 импульсов, счетчики 6 и 13 импульсов, блоки 3,4,9 и

i0 памяти, элементы И 5 и 12, блоки

2 и 8 сравнения, элемент 2И-ИЛИ 7 и блок 1 индикации. В качестве датчиков состояний и условий переходов могут быть использованы как датчики, устанавливаемые на механизмах, так к органы управления и защиты, сигналы управления информационных и электрических блокировок от других устройств.

Сочетание в данном устройстве режима сканирования при анализе комбинаций а состояний датчиков условий переходов (состояние внешней среды) и методе пошаговой отработки подпрограмм управленин Пинками работы меканиамов ноево- С ляет компоновать любые последовательности подпрограмм и на этой основе обеспечить про граммное ло гиче ское управление объектами как с детермини1302242 рованной, так и со случайной последовательностью выполняемых технологических операций, 1 ил, Изобретение относится к автоматике, а конкретнее к устройствам для программно-логического управления объектами дискретного циклического действия. 5

Целью. изобретения является повышение быстродействия устройства.

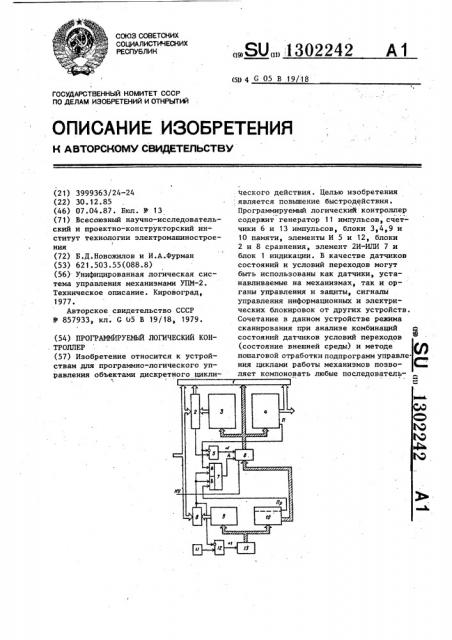

На чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит блок 1 индикации, первый блок 2 сравнения, первый

3 и второй 4 блоки памяти, первый элемент И 5, первый счетчик 6 импульсов, элемент 2И-ИЛИ 7, второй блок 8 сравнения,. четвертый 9 и третий 10 блоки памяти, генератор 11 импульсов, второй элемент И 12 и второй счетчик .

13 импульсов.

Во второй блок 4 памяти .записывается последовательность комбинаций

20 команд на включение и отключение механизмов, в первый блок 3 памяти — последовательность комбинаций состояний, В KQTopbIe должны IIpHATH датчики фик сирующие положения механизмов в результате выполнения соответствующих команд. В блок 9 памяти записывается набор комбинаций состояний датчиков условий, определяющих необходимость выполнения соответствующих этим комо бинациям переходов в программе по адресам, записываемым в блок 10 памяти.

Во всех строках второго блока 4 памяти один разряд выделен для программирования признака конца подпрограммы (П), а во всех строках блока 10 памяти один разряд выделен для программи рования признака прерывания (Пр). Адресация первого 3 и второго 4 блоков памяти осуществляется параллельно при помощи первого счетчика 6 импульсов.

Адресация третьего 10 и четвертого

9 блоков памяти осуществляется также параллельно, но посредством второго

Q4 счетчика 13 импульсов.

В качестве датчиков состояний и датчиков условий переходов могут быть использованы как собственно датчики, устанавливаемые на механизмах, так и органы управления и защиты, сигналы управления информационных и электрических блокировок от других устройств.

В качестве блоков памяти могут применяться, например, программируемые постоянные запоминающие устройства различньх типов.

Программируемыйлогический контроллер работает следующим образом.

Установка его в исходное состояние осуществляется при помощи внешнего импульсного сигнала начальной установки (НУ) и состоит в обнулении первого счетчика 6 импульсов. Процесс отработки управляющей программы состоит из анализа комбинаций состояний датчиков условий переходов (состояния внешней среды) и формирования начального адреса подпрограммы; собственно отработки выбранной подпрЬграммы, причем анализ состояния внешней среды осуществляется параллельно и независимо от отработки подпрограммы.

При отсутствии запрещения на первом (инверсном) входе второго элемента И 12 импульсы генератора 11 через элемент И 12 поступают на вход счетчика 13 импульсов, обеспечивающего циклическое сканирование четвертого 9 и третьего 10 блоков памяти, а второй блок 8 сравнения непрерывно сравнивает фактические комбинации состояний датчиков условий переходов, образующиеся на втором ее входе, с комбинациями, запрограммированными в блоке

9 памяти. При совпадении комбинаций сигналов на первом и втором входах блока 8 сравнения сигнал с его выхода запрещает прохождение импульсов генератора 11 через второй элемент И 12, второй счетчик 13 импульсов останавливается, а с первого выхода третьего блока 10 памяти на первый вход первого счетчика 6 импульсов выдается адрес перехода.

1302242

При наличии сигнала об окончании отработки подпрограммы (в общем случае при наличии сигнала П) на первом входе элемента 2И-ИЛИ 7 и сигнала с выхода второго блока 8 сравнения на 5 втором входе элемента 2И-ИЛИ 7 на выходе элемента 2И-ИЛИ 7 появляется сигнал "Адрес" (А), обеспечивающий в первый счетчик 6 импульсов запись адреса перехода, поданного на его первый вход, в результате чего первый 3 и второй 4 блоки памяти адресуются на начальный адрес соответствующей подпрограммы. При этом с первого выхода блока 4 памяти на управляемый объект выдаются записанные на данной строке подпрограммы команды управления, срабатывают соответствующие механизмы, а следовательно, и датчики, а образовавшаяся комбинация фактических .состояний датчиков цикла сравнивается при помощи первого блока 2 сравнения с комбинацией состояний, прочитанной из первого блока 3 памяти. При совпадении фактической комбинации состояний с запрограммированной и отсутствии сигнала на втором выходе второго блока 4 памяти срабатывает элемент

И 5, на выходе которого появляется сигнал, поступающий на второй (счетный) вход счетчика 6 импульсов, и увеличивает его содержимое на единицу. Происходит адресация первого 3 и второго 4 блоков памяти на следующий шаг подпрограммы. Далее процесс 35 отработки строк (шагов) подпрограммы выполняется аналогично описанному.

В случае, если на каком-либо шаге подпрограммы произойдет выход из строя или поломка механизма или датчика (но не приводящие к аварийной ситуации), переход к следующей строке подпрограммы не происходит (так как не может сработать первая схема 2 сравнения), а на блок 1 индикации выдается информация, используемая для диагностирования неисправностей: номер строки подпрограммы, на которой произошел останов (с выхода первого счетчика 6 импульсов), о состояниях входов и выходов контроллера, а с первого выхода первой схемы сравнения в блок 1 индикации выдается информация о датчике (датчиках), фактическое 55 состояние которого не соответствует запрограммированному. При устранении выявленной неисправности устройство автоматически продолжает отработку последующих строк подпрограммы. При отработке последнего шага подпрограммы на втором выходе второго блока

4 памяти появляется сигнал "Конец подпрограммы"(П), блокирующий срабатывание элемента И 5 и разрешающий чередное срабатывание элемента

2И-ИЛИ 7.

Из описанного принципа работы следует, что переходы в программе реализуются после отработки -очередной подпрограммы, т.е. в строго детерминированные моменты времени. Вместе

V с тем в реальных объектах при выходе из строя механизмов или датчиков могут образовываться комбинации состояний механизмов (a следовательно, и датчиков), которые являются запрещен,ными, т.е. такими, при которых в уп равляемых объектах могут складываться аварийные ситуации, требующие немедленного вмешательства в процесс управления. Для реакции устройства на аварийные ситуации во всех строках блока 10 памяти вьщелен разряд, наличие единицы в котором свидетельствует о принадлежности адреса, записанного в строке с признаком "Пр", к адресам переходов по аварийным ситуациям состояний датчиков условий, запи-. санным в соответствующей строке блока

9 памяти. При совпадении фактической комбинации состояний датчиков условий с одной из запрограммированных запрещенных с второго выхода третьего бло" ка 10 памяти на второй вход элемента

2И-ИЛИ 7 выдается сигнал "Прерывание" ("Пр") и так как на первом входе элемента 2И-ИЛИ 7 присутствует сигнал с выхода второго блока 8 сравнения, то срабатывает элемент 2И-ИЛИ 7 и по сигналу А в первый счетчик 6 импуль сов без ожидания конца отработки рабочей подпрограммы заносится адрес перехода к прерывающей подпрограмме, соответствующей сложившейся аварийной ситуации на управляемом объекте.

Сочетание в предлагаемом устройстве режима сканирования при анализе комбинаций состояний датчиков усло-. вий переходов (состояния внешней среды) и метода пошаговой отработки подпрограмм управления циклами работы механизмов позволяет компоновать любые последовательности подпрограмм в программе и на этой основе программируемый логический контроллер обеспечивает программное логическое

Составитель И.Швец

Редактор Л.Гротилло Техред Л.Сердюкова; Корректор М.Пожо

Заказ 1215/46

Тираж 864 Подписное

ВНИИПИ Государственного комитета СССР. по делам изобретений и открытий

113035, Москва, Ж-35, Раушская.наб,, д. 4/5

Производственно-полиграфическое предприятие, r.Óæãoðoä, ул.Проектная, 4

5 13022 управление как с детерминированной, так и со случайной последовательностью выполняемых технологических операций.

Формула изобретения

Программируемый логический контроллер, содержащий первый, второй, третий и четвертый блоки памяти, пер- 10 вый счетчик импульсов, первый и второй элементы И, информационный вход программируемого логического контроллера соединен с первым входом первого блока сравнения, второй вход кото- 15 рого подключен к выходу первого блока памяти, выход первого счетчика импульсов соединен с адресными входами первого и второго блоков памяти, а его информационный вход — с йнформа- 20 ционным выходом третьего блока памяти, отличающийся тем, что, с целью повьппения быстродействия устройства, в него введены генератор импульсов, второй блок сравнения, второй счетчик импульсов, элемент

2И-ИЛИ и блок индикации, первый вход которого соединен с информационным входом программируемого логического контроллера, второй вход — с выходом первого блока сравнения, третий вход— с информационным выходом первого счетчика импульсов, четвертый вход— с информационным выходом второго блока памяти и выходом программируемого логического контроЛлера, второй выход первого блока сравнения соединен с первым входом первого элемена И, инверсный вход которого соединен с выходом второго блока памяти и первьп

Э входом первого элемента 2И-ИЛИ, вто-, рой вход которогЬ соединен с третьим входом элемента 2И-ИЛИ, с выходом второго блока сравнения и инверсным входом второго элемента И, второй вход которого подключен к выходу генератора импульсов, а выход — к вход> второго счетчика импульсов, выход которого соединен с адресными входами третьего и четвертого блоков памяти, установочный вход первого счетчика импульсов которого соединен с входом начальной установки программируемого логического контроллера, адресный вход — с выходом элемента 2И-ИЛИ, счетный вход — .с выходом первого элемента И, информационный вход програм" мнруемого логического контроллера соединен с первым входом второго блока сравнения, второй вход которого подключен к выходу четвертого блока памяти, четвертый вход элемента 2И-ИЛИ, соединен с выходом третьего блока памяти.