Фазовый фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и предназначено для использования в системах спектрального анализа процессов с неравномерным разрешением по частоте. Цель изобретения - повышение точности . Поставленная цель достигается за счет того, что фазовый фильтр состоит из мультиплексора 1, сдвигового регистра 2, мультиплексора 3, регистра 4, арифметического блока 5, регистра 6 и синхронизатора 7. 4 шт. г kn 45 / 7 V э э tsD N5 ) Л 9иг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19} (1И

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3988499/24-24 (22) 09. 12.85 (46) 07.04.87. Б}0л. Р 13 (71) Институт технической кибернетики АН БССР (72) С.Н. Демиденко, В.Е. Куконин, В.И. Петько и П.М. Чеголин (53) 681.32 (088.8) (56) Рабинер Л.,и Гоулд Б. Теория и применение цифровой обработки сигналов. — М.: Иир, 1978.

Оппенгейм А.В. и Джонсон Д.Х. Дискретное представление сигналов.

ТИИЭР, 1972, т. 60, }} 6, с. 47, рис. 8. (51} g (: 06 F 15/353, H 03 Н 17/04 (54) ФАЗОВЫЙ ФИЛЬТР (57) Изобретение относится к цифровой вычислительной технике и предназначено для использования в системах спектрального анализа процессов с неравномерным разрешением по частоте.

Цель изобретения — повышение точности. Поставленная цель достигается за счет того, что фазовый фильтр состоит из мультиплексора 1, сдвигового регистра 2, мультиплексора 3, регистра 4, арифметического блока 5, регистра 6 и синхронизатора 7. 4 ил.

2295

) 1

А, (Е)

А = а(Ь-c)+d у; =,> х„Ь =о! 130

Изобретение относится к цифровой вычислительной технике и предназначено для использования в системах спектрального анализа процессов с неравномерным разрешением по частоте.

Целью изобретения является повыше- ние точности путем реализации коррекции частотной характеристики фильтра.

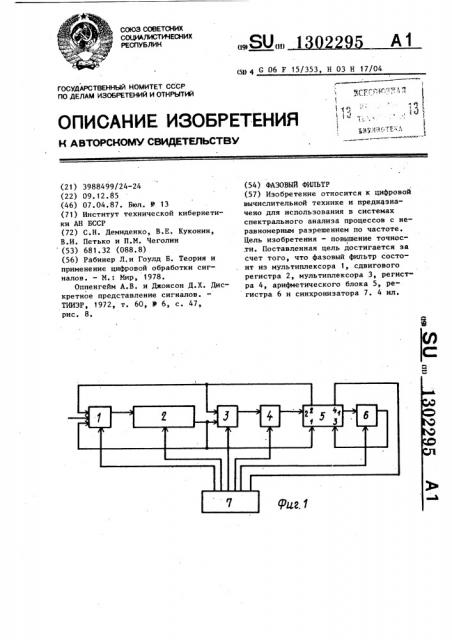

На фиг.1 представлена схемз фильтра, на фиг.2 — схема арифметического блока; на фиг.3 — временные диаграммы; на фиг.4 — схема синхронизатора.

Фильтр (фиг.1) содержит первый мультиплексор 1, сдвиговый регистр 2, второй мультиплексор 3, регистр 4, арифметический блок 5, регистр 6 и .синхронизатор 7.

Арифметический блок 5 (фиг.2) содержит сумматоры 8 и 9 и умножнтель

10 и предназначен для вычисления выражения

Синхронизатор 7 (фиг.4) содержит генератор 11 тактовых импульсов, счетчик 12, блок 13 постоянной памяти, элементы 14 задержки и элементы И 15.

Устройство работает. следующим образом.

Пусть в установившемся режиме функционирования в k первых (левых) разрядах сдвигового регистра 2 записаны некоторые (и-1)-е значения выходной функции с деформированным спектром, g „„,,,,я „< (k — порядок фазового фильтра), а в оставшихся ш следующих разрядах — отсчеты входной последовательности в порядке их поступления справа налево х х,„,...,х, (справа тот из m отсчетов, который поступил раньше других). Содержимое регистров 4 и 6 равно нулю. На первом этапе производится коррекция частотного состава входного дискретного процесса,. компенсирующая искажения, вносимые на этапе собственно фазовой фильтрации. Для этого m отсчетов входного процесса, хранимые в правых разрядах сдвигового регистра 2, обрабатываются по алгоритму нерекурсивного частотного фильтра где у; — 1-й отсчет выходной отфильтрованной последовательности;

2 х;, — (i+j)-й отсчет входной последовательности;

h - j-й коэффициент весовой функ3 ции фильтра.

5 Значение коэффициентов h выбирают1 ся такими, чтобы выполнялось соотношение где А (f) — амплитудно-частотная ха1 рактеристика корректирующей цепи;

Az(f) — амплитудно-частотная характеристика устройства для фазовой фильтрации.

Обработка происходит следующим образом.

С выхода последнего разряда регистра сдвига значение i-го отсчета х; входного процесса передается на первый вход арифметического блока 5. Одновременно на четвертый вход блока 5

25 из синхронизатора 7 поступает значение h весового коэффициента. На третий и второй входы арифметического блока 5 с выходов регистров 4 и 6 передаются нулевые значения.

Получаемое на втором выходе арифметического блока 5 значение первой частичной суммы S равное х; и поступает по командам синхронизатора 7 через второй мультиплексор 3 в регистр 4 и фиксируется в нем. Затем по сигналу из синхронизатора 7 в сдвиговом регистре 2 происходит сдвиг

I хранимой информации на один разряд вправо. С выхода последнего разряда

4р сдвигового регистра 2 значение х;« .передается через мультиплексор 1 в освободившийся первый разряд регистра

2 сдвига и по сигналу из синхронизатора 7 записывается в нем. Кроме то45 го, данное значение поступает на первый вход арифметического блока 5,. на второй вход которого с выхода регистра 4 передается зйачение х; h, на третий вход — нулевое значение с выхода регистра 6, а на четвертый вход— значение соответствующего весового коэффициента h с выхода синхронизатора 7. В результате на выходе арифметического блока 5 получается значе55 ние второй частичной суммы S2, равное

S, + x;„ h,, которое по сигналам синхронизатора 7 через второй мультиплексор 3 поступает в регистр 4 и фиксируется в нем. Далее по сигналу

g „= a(g — 0) + Е „(2) = а(Й,„, — О) + g q,> (3) 35

g<,n ю \

g;„= а(д;„, — g;,„) + g;,„, (4) где а — коэффициент, определяющий деформацию спектра процесса (при 1 ) а ) 40 О спектр имеет большее разрешение на низких частотах и меньшее на высоких, при О > а -1 наоборот — более высокое.разрешение на высоких и меньшее на низких, при комплексном а раэ-45 решение увеличено в любой наперед заданной области частотного диапазона).

С выхода последнего (правого) разряда регистра 2 сдвига значение g поступает на первый вход арифметического блока 5, на второй вход которого с выхода регистра 4 передается значение f „, на третий — нулевое значение с выхода регистра 6, а на четвертый — код коэффициента деформации спектра а, задаваемый из синхронизатора 7. На выходе арифметического блока 5 получаем значение О-ro

3 13022 из синхронизатора 7 осуществляется очередной сдвиг информации в сдвиговом регистре 2 и обрабатывается сле-. дующий отсчет х;, входного процесса аналогично описанной выше процеду5 ре и т.д. Окончательно, после обработки последнего х; -го отсчета входного процесса, хранимого в регистре 2 сдвига, в регистре 4 получаем отфильтрованное значение i-го вход- щ ного процесса у..

Этот отсчет можно обозначить f

Затем по сигналу синхронизатора 7 в регистре 2 сдвига происходит сдвиг хранимой информации вправо на один разряд, при этом в последний (правый) разряд регистра 2 сдвига вдвигается правое промежуточное значение последовательности с деформированным спектром. В освободившийся первый 2р (левый) разряд регистра 2 сдвига по сигналам синхронизатора 7 поступает и записывается очередное значение входного процесса (через первый) мультиплексор 1 с его третьего входа). 25

Затем начинается рекуррентный процесс вычисления значений последовательности с деформированным спектром на очередном этапе.

Этот процесс описывается выраже- 30 ниями

95 4 члена последовательности с деформированным спектром после очередной итерации g „,,которое по сигналам синхронизатора 7 через первый мультиплексор 1 поступает на вход первого (левого) разряда регистра 2 сдвига.

На выходе арифметического блока 5. повторяется значение gо„ ° По сигналам с выходов синхронизатора 7 в регистре 2 сдвига происходит сдвиг хранимой информации вправо на один разряд, при этом значение, выдвигаемое из последнего (правого) раэряда,записывается в регистр 4, а в первом (левом) разряде регистра 2 сдвиг фиксируется значение

Затем происходит вычисление значения g в соответ-..твии с выражением (3). С выхода последнего (правого) разряда регистра 2 сдвига на первый вход арифметического блока 5 передается значение g < „, На второй вход арифметического блока 5 с выхода регистра 4 поступает. значение я „,, на третий — нулевая величина с выхода регистра 6, а на четвертый — значение кода а коэффициента деформации спектра задаваемого из синхронизатора 7. Получаемые на выходе арифметического блока 5 устройства значения поступают на вход регистра

6 и через мультиплексор 1 на вход первого разряда сдвигового регистра

2. По сигналам синхронизатора 7 в регистре 2 сдвига производится сдвиг хранимой информации вправо на один разряд, причем выдвигаемое из последнего (правого) разряда значение g <. записывается в регистр 4, а в освободившийся первый разряд регистра 2значение д,, в регистр 6 записывается значение g„ Затем происхоI дит очередное вычисление в арифметическом блоке 5, описываемое выражением (4), при k=2, которое происходит в целом аналогично представленной выше обработке на предыдущем такте за исключением того, что на третий вход арифметического блока 5 поступает с выхода регистра 6 не нулевое значение, а величина g < . Аналогично, в соответствии с выражением (4), происходит вычисление отсчетов последовательности g „ для всех остальных значений i. Окончательно, в результате выполнения обработки для последнего k-го отсчета и получения g„ „ приходим к исходному

1302295 а залпа

Я+ 2 arcing 1 где Q= 2ift в = 21т;

f — значение частоты в исходном массиве; значение частоты в преобразовательном массиве; — интервал между поступлениями отсчетов на вход устройства.

Формула изобр ет ения

Фазовый фильтр, содержащий сдвига вый регистр, первый и второй регистры, причем выход сдвигового регистра подключен к первому входу арифметического блока, второй и третий входы которого подключены к выходам соотсостоянию, при котором в k первых (левых) разрядах регистра 2 сдвига находятся и-е значения последовательности с деформированным спектром,а в остальных ш — отсчеты входного процесса, Начинается новая вычислительная итерация и т.д. до поступления всех отсчетов входной последовательности. Окончательный результат обработки.считывается с первых (левых) разрядов регистра 2 сдвига, причем частотный состав данного дискретного процесса изменен по сравнению с исходным в соответствии с выражением ветственно первого и второго регистров, выход арифметического блока подключен к информационному входу второго регистра, причем арифметический блок содержит два сумматора и умножитель, выход которого подключен к первому входу первого сумматора, выход которого является выходом арифметического блока, первым, вторым и третьt0 им входами которого являются соответственно первый вход второго сумматора, второй вход первого сумматора и второй вход второго сумматора, выход которого подключен к первому

15 входу умножителя, второй вход которого является входом задания коэффициентов фильтра, о .т л и ч а ю щ и йс я, тем, что, с целью повышения точности,в него введены первый и вто20 рой мультиплексоры и синхронизатор, первый, Второй, третий, четвертый и пятый выходы которого подключены соответственно к управляющему входу первого мультиплексора, тактовому

25 входу сдвигового регистра, управляющему входу второго мультиплексора, тактовым входам первого и второго регистров, причем выход первого мульО типлексора подключен к информацион30 ному входу сдвигового регистра, выход которого подключен к первым информационным входам первого и второго мультиплексоров, вторые информационные входы которых подключены к выходу арифметического блока, а третий информационный вход первого мультиплексора является информационным входом фильтра.

2,Ф,6

7 1 фиг. Л

Фиг. 4

ВНИИПИ Заказ 1218/49 Тираж 673 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4