Регистр сдвига

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть иснользовано для сдвига двоичных кодов, у которых справа от каждой единицы следует не менее двух нулей. К таким кодам относятся , например, коды с иррациональными оспованиями:р-коды Фибоначчи и коды «золотой р-пропорции, причем р2 -2. Целью изобретения является упрощение устройства. В регистре сдвига используются одноступенчатые / 5-триггеры, а сдвиг выполняется за два такта. В первом такте единица переписывается из предыдущего триггера в последующий , а во втором предыдупхий триггер устанавливается в нуль. В отличие от прототипа регистр сдвига содержит инвертор и имеет другие связи между соседними разрядами . 1 ил. 1 табл. « (Л со о to со to о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„Я0„„1302320 (SD < Ci 11 С 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Сй

CO

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3973822/24-24 (22) 04.10.85 (46) 07.04.87. Бюл. № 13 (72) А. П. Стахов, В. А. Лужецкий, А. И. Черняк и А. Е. Андреев (53) 681.327.66 (088. 8) (56) Шигин A. Г. Цифровые вычислительные машины. (Элементы и узлы) — M.:

Энергия, 1971, с. 172.

Майоров С. А., Новиков Г. И. Принципы организации цифровых машин. — Л.:

Машиностроение, 1974, с. 128. (54) РЕГИСТР СДВИГА (57) Изобретение относится к области вычислительной техники н может быть использовано для сдвига двоичных кодов, у которых справа от каждой единицы следует не менее двух нулей. К таким колам относятся, например, колы с иррациональными основаниями:р-коды Фибоначчи и коды «золотой» р-пропорции, причем р о 2. Целью изобретения является упрогцение устройства.

В регистре сдвига используются одноступенчатые RS-триггеры, а сдвиг выполняется за два такта. В первом такте единица переписывается из прелылущего триггера в последующий, а во втором прелылущпй триггер устанавливается в нуль. В отличие от прототипа регистр сдвига содержит инвертор и имеет другие связи между соселними разрядами. 1 ил. табл.

1302320

Такт

Действия

Сост яги:е тоиггеоов

Вход 18

0 Начальная установка

0 0 0 0

o o o o

0 0 0 0

1 Запись единиц

2 Запись нулей

3 Запись единиц

0 0 0

4 Запись нулей

О 0 0 1

5 Запись единиц

0 0

6 Запись нулей

0 0 0

0 0

0 1 0 0

7 Запись единиц

8 Запись нулей

9 Запись единиц

О 0

10 Запись нулей

Изобретение относится к вычислительной технике и может быть использовано для сдвига двоичных кодов, у которых справа от каждой единицы следует не менее двух нулей (коды с иррациональными основаниями; р-коды Фибоначчи и коды «золотой» р-пропорции, причем р)2).

Целью изобретения является упрощение регистра сдвига.

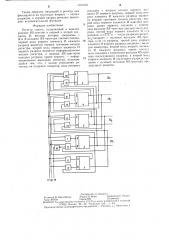

На чертеже приведена схема регистра сдвига, содержащего, например, 5 разрядов.

Каждый разряд регистра содержит

RS-триггер, первый и второй элементы И.

На схеме обозначены Ю-триггеры 1 — 5, первые 6 — 10 и вторые 11 — 15 элементы И, инвертор 16, первый 17 и второй 18 тактовые входы, информационный вход 19 и информационные выходы 20 регистра сдвига.

Регистр сдвига работает следующим образом.

Предположим, что на вход 19 поступает код 010010... Предварительно триггеры

1 — 5 устанавливаются в нуль (цепи установки в нуль не показаны). Запись и сдвиг кода производится за два такта: первый такт— такт записи единиц, второй такт — такт записи нулей. Тактовые сигналы поступают на входы 17 и 18. Пусть на входе 19 действует первый (О) разряд входного кода.

При подаче сигнала на вход 17 (в первом такте) состояние триггеров 1 — 5 не изменяется.

Во втором такте на вход 18 подается сигнал разрешения записи нулей, при этом триггеры 1 — 5 также остаются в прежних состояниях.

При подаче на вход 19 второго разряда (1) в первом такте на выходе элемента И 6 формируется единичный сигнал, под действием которого триггер 1 устанавливается в единичное состояние, вследствие чего на выходе элемента И 7 формируется единичный сигнал, под действием которого триггер 2 также устанавливается в единичное состояние. Триггеры 3 — 5 остаются в прежних состояниях. Во втором такте на вход 18 подается сигнал разрешения записи нулей, при этом на выходе элемента И 11 формируется единичный сигнал, под действием которого триггер 1 устанавливается в нулевое состояние, триггеры 2 — 5 при этом остаются в прежних состояниях.

При подаче на вход 19 третьего разряда кода (О) и на вход 17 сигнала разрешения записи единиц триггер 3 устанавливается в единичное состояние, остальные триггеры при этом остаются в прежних состояниях. Во втором такте на вход 18 подается сигнал разрешения записи нулей, под действием которого триггер 2 устанавливается в нулевое состояние, а остальные триггеры остаются в прежних состояниях.

При подаче на вход 19 четвертого раззп ряда кода (О) и на вход 17 сигнала разрешения записи единиц триггер 4 устанавливается в единичное состояние. Остальные триггеры остаются в прежних состояниях. Во втором такте на вход 18 подается сигнал разрешения записи нулей, под действием которого триггер 3 устанавливается в нулевое состояние. Остальные триггеры остаются в прежних состояниях.

При подаче на вход 19 пятого разряда кода (1) и на вход 17 сигнала разрешения записи единиц триггер 5, а также триггеры 1 и 2 устанавливаются в единичное состояние. Триггеры 3 — 4 остаются в прежних состояниях. Во втором такте на вход 18 подается сигнал разрешения записи нулей, под действием которого триггеры 4 и 1 устанавливаются в нулевое состояние. Остальные триггеры остаются в прежних состояниях и т. д.

В таблице проиллюстрирована работа регистра. з 1302320 4

17 18 19

Составитель A. Дерюгин

Редактор И. Николайчук Техред И. Верес Корректор Е. 1зошко

Заказ 949/50 Тираж 590 Г1одписнос

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 415

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Таким образом, вводимый в регистр код фиксируется на триггерах второго — пятого разрядов, а первый разряд регистра выполняет вспомогательные функции.

Формула изобретения

Регистр сдвига, содержащий в каждом разряде RS-триггер и первый и второй элементы И, выходы которых соединены с

5 -и R-входами RS-триггера соответственно, первый вход первого элемента И каждого разряда является первым тактовым входом регистра, второй вход первого элемента И первого разряда является информационным входом регистра, а выходы RS-триггеров каждого разряда, кроме первого, — информационными выходами регистра, отличаюи4ийся тем, что, с целью упрощения регистра, он содержит инвертор, вход которого соединен с вторым входом первого элемента И первого разряда, первый вход второго элемента И каждого разряда является вторым тактовым входом регистра, второй вход первого элемента И каждого разряда, кроме первого, соединен с единичным выходом RS-триггера предыдущего разряда, третий вход первого элемента И i-го разряда,i =3, и, n — число разрядов регистра, соединен с нулевым выходом RS-трпг10 гера (-2) -го разряда, третий вход второго элемента И второго разряда соединен с выходом инвертора, второй вход второго элемента И каждого разряда, кроме последнего, соединен с единичным выходом RS-тригI5 гера последующего разряда, а второй вход второго элемента И последнего разряда соединен с нулевым выходом RS-триггера-предыдущего разряда.