Устройство для контроля оперативной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной .технике, в частности к устройствам для контроля оперативных запоминающих устройств (ОЗУ) с произвольной выборкой. Целью изобретения является повышение достоверности контроля. Устройство содержит блок управления, мультиплексор, первый, второй и третий блоки сравнения, регистр задержки данных, формирователь выходных сигналов, блок эталонной памяти, блок фиксации ошибки, формирователь информационных сигналов, первый и второй счетчики адреса, блок индикации. Повышение достоверности контроля достигается за счет введения в устройство блока эталонной памяти, третьей схемы сравненияи блока фиксации ошибки, позволяющих контролировать процесс генерации тестовых воздействий. 4 ил. 00 о to со to ел

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (я) 4 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3952267/24-24 (22) 06.09.85 (46) 07.04.87. Бюл. № 13 (71) Всесоюзный научно-исследовательский институт телевидения и радиовещания (72) В. 3. Хаимов, Н. Н. Иванова и Ю. В. Скобелев (53) 681.327.6 (088.8) (56) Electronic Design, 1978, ч. 26, № 19, р.р. 118 — 122.

Авторское свидетельство СССР № 1003150, кл. С 11 С 29/00, 1983. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ОПЕРАТИВНОЙ ПАМЯТИ (57) Изобретение относится к вычислительной,технике, в частности к устройствам

80» 1302325 А1 для контроля оперативных запоминающих устройств (ОЗУ) с произвольной выборкой.

Целью изобретения является повышение достоверности контроля. Устройство содержит блок управления, мультиплексор, первый, второй и третий блоки сравнения, регистр задержки данных, формирователь выходных сигналов, блок эталонной памяти, блок фиксации ошибки, формирователь информационных сигналов, первый и второй счетчики адреса, блок индикации. Повышение достоверности контроля достигается за счет введения в устройство блока эталонной памяти, третьей схемы сравнения. и блока фиксации ошибки, позволяющих контролировать процесс генерации тестовых воздействий.

4 ил.

1302325

Изобретение относится к вычислительной технике, в частности к устройствам для контроля оперативных запоминающих устройств (ОЗУ) с произвольной выборкой.

Цель изобретения — повышение достовер н ости ко нтрол я.

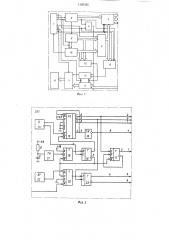

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 — функциональная схема блока управления; на фиг. 3— функциональная схема формирования информационного сигнала; на фиг. 4 — эпюры, поясняющие работу блока управления.

Устройство для контроля оперативной памяти содержит блок 1 управЛения, мультиплексор 2, первый блок 3 сравнения, регистр 4 задержки данных, формирователь

5 выходных сигналов, блок 6 эталонной памяти, блок 7 фиксации ошибки, формирователь 8 информационных сигналов, первый 9 и второй 10 счетчики адреса, третий 11 и второй 12 блоки сравнения, блок индикации 13.

Блок 1 управления (фиг. 2) содержит задающий генератор 14, формирователь 15 сдвинутых последовательностей, второй триггер 16, формирователь 17 управляющего сигнала, инвертор 18, первый 19 и третий 20 триггеры, триггер 21 Шмитта, кнопку 22 и четвертый триггер 23.

Формирователь 8 информационных сигналов (фиг. 3) содержит счетчик 24 длительности такта и дешифратор 25.

Устройство работает следующим образом.

Работа устройства начинается с установки и микросхем памяти в держатели накопителя. При включении питания в блоке 1 управления вырабатывается положительный фронт на RC-цепочке и триггере 21 Шмитта, который поступает на тактовый вход первого триггера 19 и далее с его прямого выхода на информационный вход второго триггера 16. После тактирования (фиг. 4 а) на инверсном выходе триггера 16 образуется отрицательный фронт (фиг. 4б), который поступает на сбросовый вход первого триггера 19. В результате этого на прямом выходе этого триггера образуется импульс положительной полярности, а на выходах второго триггера 16 образуются импульсы соответственно положительной и отрицатель:«oH полярностей, длительностью в такт частоты задающе о генератора 14. По приходе импульса положительной полярности с прямого выхода второго триггера 16 на вход управления формирователя 15 сдвинутых последовательностей код, заданный на его входах предустановки, переписывается на выходы. По окончании установочного импульса под воздействием тактовой частоты, поступающей на тактовый вход формирователя 15 сдвинутых последовательностей задающего генератора 14, в формирователе осуществляется сдвиг единицы в сторону

1

55 старшего разряда и далее по обратной связи на его информационный вход.

Таким образом, на выходах появляются последовательно сдвинутые относительно друг друга тактовые последовательности.

Тактовая последовательность с первого выхода формирователя 15 поступает на находящийся в счетном режиме триггер формирователя 17, образуя сигнал меандровой формы, поступающий далее на вход управления мультиплексора 2 (фиг. 4в). Одновременно с инверсного выхода триггера 16 установочный импульс поступает на тактовый вход третьего триггера 20 и переписывает нулевой потенциал с его входа на выход, а также на сбросовый вход формирователя 17 управляющего сигнала. Нулевой потенциал с выхода третьего триггера 20 поступает на информационный вход четвертого триггера 23, где переписывается с приходом тактовой последовательности на выход (фиг. 4и). В результате этого устройство находится в режиме «Стоп».

При нажатии кнопки 22 «Пуск» происходит переустановка третьего триггера 20 в единичное состояние и перезапись логической единицы с входа на выход четвертого триггера 23 (фиг. 4з). Разрешающий потенциал с инверсного выхода четвертого триггера 23 поступает на установочные входы счетчиков 9 и 10 адресов и счетчика 24 длительности, разрешая их работу. Выходы счетчика 24 дл ител ьности подключены к дешифратору-формирователю 25, где и происходит формирование информационного сигнала, который поступает на формирователь 5 выходных сигналов и далее на проверяемые микросхемы памяти.

Для одного цикла работы при формировании теста «Попарная запись — считывание с полным перебором» необходимо шестнадцать периодов тактовой последовательности, так как при обращении к каждой паре ячеек из всевозможных в режимах записи и считывания необходимо проверить четыре возможные комбинации состояния ячеек: 00, 01, 10, 11. Поэтому смена пар адресов происходит раз в шестнадцать периодов тактовой последовательности по импульсу переноса, поступающему со счетчика 24 длительности. Адресные сиггналы с выходов счетчиков 9 и 10 адресов поступают на информационные входы мультиплексора 2, где коммутируются на выход в соответствии с сигналом управления, тем самым обеспечивая однозначность обращения к паре ячеек. С выхода мультиплексора 2 адрес поступает на соответствующие входы формирователя 5 выходных сигналов и далее на плату накопителя. Туда же через формирователь 5 поступают сигналы разрешения записи и считывания соответственно с третьего и четвертого выходов блока 1 управления.

1302325

Формула изобретения

Для обеспечения режима самоконтроля на блок 6 подают те же, что и в накопитель, сигналы. Работу блока эталонной памяти 6 ведут непрерывно и параллельно с проверкой микросхем памяти на плате накопителя.

Считанная из накопителя и блока 6 информация поступает соответственно на первый 3 и третий 11 блоки сравнения, куда одновременно поступает опорная информация, задержанная в регистре 4 на необходимое число тактов. Для правильной работы указанных блоков сравнения необходимо исключить ситуацию, вытекающую из способа построения функционального теста, а именно, момент времени, когда адресные коды обоих счетчиков 9 и 10 адресов совпадают. В этом случае во время шестнадцати периодов тактовой последовательности производится обращение к одной и той же ячейке микросхем памяти. Поэтому, вместо записанных в последовательные моменты времени кодовых комбинаций 01, 10 считываются кодовые комбинации соответственно 11 и 00, что следует из логики построения теста «Попарная запись — считывание с полным перебором».

Включение второго блока 12 сравнения позволяет определить эти моменты времени и выработать строб, запирающий первый 3 и третий 11 блоки сравнения. Результат сравнения фиксируется блоком 7 и выводится в блок 13 индикации. В последнем индицируются номера тех микросхем памяти, в которых обнаружены одна или несколько неисправностей.

При неправильном функционировании самого устройства третий блок 11 сравнения вырабатывает сигнал ошибки, который фиксируется в блоке 7 и индицируется в блоке 13 индикации.

В момент появления импульса переноса на выходе счетчика 10 адреса, сигнализирующего об окончании перебора всех возможных адресных комбинаций, в блоке 1 управления вырабатывается потенциал, запрещающий дальнейшую работу счетчиков

9 и 10 адресов и счетчика 24 длительности, и устройство возвращается в режим ожидания (состояние «Стоп»).

Устройство для контроля оперативной памяти, содержащее первый счетчик адреса, информационные выходы которого подключены к информационным входам первой группы мультиплексора, а выход переполнения

50 соединен со счетным входом второго счетчика адреса, информационные выходы которого подключены к входам первой группы второго блока сравнения и к информационным входам второй группы мультиплексора, управляющий вход которого соединен с первым выходом блока управления, второй и третий выходы которого подключены соответственно к входу синхронизации первого блока сравнения и к синхровходу регистра задержки данных, информационный вход которого соединен с информационным выходом формирователя информационных сигналов, а выход подключен к информационному входу первого блока сравнения, информационные входы группы которого являются информационными входами устройства, отличающееся тем, что, с целью повышения достоверности контроля, в усТройство введены блок эталонной памяти, третий блок сравнения, блок фиксации ошибки, причем третий выход блока управления соединен с входом разрешения считывания б.пока эталонной памяти, а четвертый выход подключен к входу разрешения записи блока эталонной памяти, адресные входы которого соединены с выходами мультиплексора и явпяются адресными выходами устройства, информационные выходы группы формирователя информационных сигналов являются информационными выходами устройства, а шестой выход блока управления соединен с входами начальной установки первого и второго счетчиков адреса и формирователя информационных сигналов, вход синхронизации которого подключен к седьмому выходу блока управления, пятый выход которого соединен с входом сброса блока фиксации ошибки, выходы которого являются информационными выходами устройства, а установочные входы подключены к выходам второго и третьего блоков сравнения, выход переполнения формирователя информационных сигналов соединен со счетным входом первого счетчика адреса, а информационный выход подключен к информационному входу блока эталонной памяти, выход которого соединен с вторым информационным входом третьего блока сравнения, первый информационный вход и вход синхронизации которого подключены к соответствующим входам первого блока сравнения, а вход запрета сравнения соединен с соответствующим входом первого блока сравнения и с выходом второго блока сравнения, входы второй группы которого подключены к информационным выходам первого счетчика адреса, выход переполнения второго счетчика адреса соединен с входом блокировки блока управления.

1302325

Фиг. 2! 302325

Фиг. s

„Canon

Составитель"(Э. Исаев

Редактор И. Дербак Техред И. Верес Корректор И.Муски

3aказ 949/50 Тираж 590 Поди ясное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытнй ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4