Устройство для сопряжения в резервированной многопроцессорной системе

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в высоконадежных многомашинных комплексах и сетях ЭВМ, при этом сокращается время восстановления работоспособности системы в случаях jj 1Jсбоя двух из трех резервированных процессоров , подключаемых посредством устройства к магистрали системы. Три процессора 1, 2, 3 подключаются к устройству 4, которое содержит блок 5 мажоритарных элементов, четыре шинных формирователя 6, 7, 8, 11, блок 9 контроля, первый блок 10 синхронизации , второй блок 12 синхронизации. В процессе синхронной работы процессоров 1, 2, 3 возможны случайные искажения информации, что приведет к останову устройства. Для его предотвращения служит блок 12, который формирует местные сигналы управления и организует повторные циклы передачи информации в адрес соответствующего устройства магистрали. 1 з.п, ф-лы, 2 ил. S (Л оо 4

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 С 06 Е 15 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ фие1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 39! 9158/24-24 (22) 01.07,85 (46) 15.04,87, Бюл. У 14 (72) В.И.Головин, Е.M.Eðçàêoâ и И.Я.Денищенко (53) 681.325(088.8) (56) Патент США Р 3921149, кл. G 06 F 15/16, опублик ° 1975 °

Авторское свидетельство СССР

N - 1156087, кл. G 06 F 15/16, 1982. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ В РЕЗЕРВИРОВАННОЙ МНОГОПРОЦЕССОРНОЙ СИСТЕМЕ (57) Изобретение относится к области вычислительной техники и может быть использовано в высоконадежных многомашинных комплексах и сетях ЗВМ, при этом сокращается время восстановления работоспособности системы в случаях

„„Я0„„1304031 А 1 сбоя двух из трех резервированных процессоров, подключаемых посредством устройства к магистрали системы. Три процессора 1, 2, 3 подключаются к устройству 4, которое содержит блок 5 мажоритарных элементов, четыре шинных формирователя 6, 7, 8, 11, блок 9 контроля, первый блок 10 синхронизации, второй блок 12 синхронизации. В процессе синхронной работы процессоров 1, 2, 3 возможны случайные искажения информации, что приведет к останову устройства. Для его предотвращения служит блок 12, который формирует местные сигналы управления и организует повторные циклы передачи информации в адрес соответствующего устройства магистрали. 1 з.п. ф-лы, 2 ил.

4031 2

tO

f5

ЗО

t 130 !

Изобретение относится к вычислительной технике и может быть использовано для объединения процессоров в высоконадежных и распределенных вычислительных сетях ЭВМ.

Целью изобретения является уменьшение времени восстановления работоспособности за счет организации повторных циклов вывода информации в мегистраль.

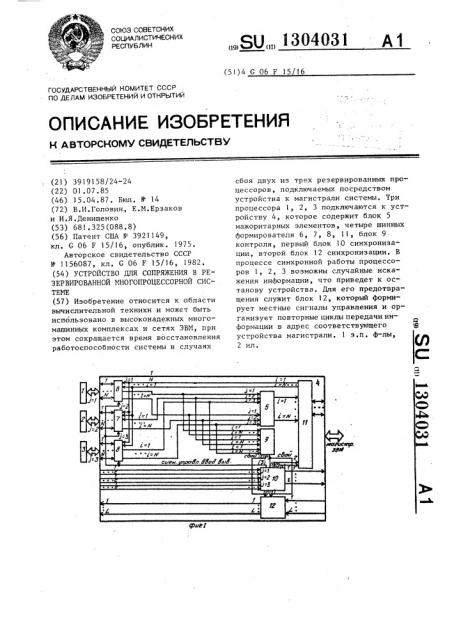

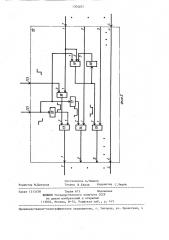

На фиг,1 приведена функциональная схема устройства; на фиг.2 — функциональная схема второго блока синхронизации.

Процессоры 1-3 подключаются через устройство 4 для сопряжения в резервированной .многопроцессорной системе, содержащее (фиг.1 ) блок 5 мажоритарных элементов, шинные формирователи

6-8, блок 9 контроля, первый блок 10 синхронизации, шинный формирователь

11 и второй блок 12 синхронизации, к магистрали системы.

Второй блок 12 синхронизации (фиг.2) содержит три элемента ИЛИ 1315, два формирователя импульса 16, 17, элемент И 18, счетчик 19, элемент 20 задержки.

Устройство работает следующим образом.

В исходном состоянии шинные формирователи 6-8 находятся в режиме "Ввод шинный формирователь 11 закрыт, Далее устройство функционирует известным образом, В случае искажения информации в двух и более процессорах 1, 2, 3 блок

9 формирует прямой и инверсные сигналы признака сбоя, При этом в блоке

10 вырабатывается сигнал, запрещающий передачу информации в магистраль шинным формирователем 11.

Одновременно при этом в блок 12 пр первому и второму входам с блока 9 поступают, соответственно сигналы

"1" и "0". Сигнал "0" при сбое информации, сформированный формирователем 16, пройдя через элемент ИЛИ 13, предотвращает формирование процессорами сигнала "Сбой канала" и выход на связь с пультовым терминалом и одновременно, пройдя через формирователь и элемент ИЛИ, выставляет в процессоры сигнал низкого уровня "Прерывание по таймеру" (К ПРТ Н), который инициирует программный цикл повторного вывода информации из процессоров во внешнее устройство. В это же время сигнал "1" по второму входу блока 12 запрещает двойное прохождение сигнала синхронизации, подтверждающего прием данных пассивным устройством (К СИП Н) к процессорам от пассивного внешнего устройства, котарый в соответствии с дисциплиной обмена должен поступить в процессоры спустя 10 мкс после обращения к внешнему устройству. Каждый случай искажения информации сопровождается появлением по второму входу блока 12 сигнала "0", число которых подсчитывается счетчиком 19. При переполнении счетчика 19 на его выходе появляется сигнал "Переполнение" ("0").

Стандартная длительность сигнала останове (К 0СТ Н) формируется элементом 20 задержки, с выхода которого по переднему фронту сигнала счетчик

19 устанавливается в исходное состояние, Сигнал "0" с выхода счетчика 19 через элемент ИЛИ 15 поступает в процессоры 1 » 3, как сигнал К ОСТ Н и переводит процессоры 1, 2, 3 в режим связи с пультовым терминалом.

В случае, если в процессе программного цикла повторного вывода информации из процессоров 1, 2, 3, во внешнее устройство искажения информации в двух и более процессорах не переполнила счетчик 19, то после получения данных внешнее устройство вырабатывает стандартный сигнал синхронизации К СИП Н, который по первому входу блока 12 сбрасывает счетчик 19 в исходное состояние и завершает цикл обмена с процессорами 1, 2, 3.

В прототипе, когда количество случайных сбоев каждого из процессоров (но не двух одновременно) при сохранении их общей работоспособности возрастает, происходит быстрое переполнение счетчиков спучайных сбоев, что ведет к останову всего устройства и снижает его надежность (наработку на отказ). В предлагаемом устройстве счетчики случайных сбоев ликвидированы и количество случайных сбоев каждого процессора на работу устройства не влияет.

В прототипе при случайном искажении информации в двух процессорах происходит останов устройства и перевод процессоров в режим связи с пультовым терминалом, что при работе устройства в режиме реального времени недопчстимо. Ъ предлагаемом устройст3 13040 ве при случайном искажении информации в двух процессорах организуются повторные циклы вывода информации в адрес внешнего устройства.

Формула изобретения

1. Устройство для сопряжения в резервированной многопроцессорной системе, содержащее четыре шинных Я формирователя, блок мажоритарных элементов, блок. контроля и первый блок синхронизации, информационные входывыходы с первого по третий шинных формирователей являются информацион- f5 ными входами-выходамн с первого по третий процессоров устройства соответственно, информационные входы с первого по третий шинных формирователей поразрядно объединены и подключе-д) ны к информационному выходу четвертого шинного формирователя, информационный вход-выход которого является одноименным входом-выходом устройства, подключаемым к магистрали системы, 25 информационные выходы с первого по третий шинных формирователей подключены к входам с первого по третий блока контроля и блока мажоритарных элементов соответственно, выход кото- 30 рого соединен с информационным входом четвертого шинного формирователя, группы входов и выходов первого блока синхронизации являются группой входов сигналов синхронизации от про- 35 цессоров и группой выходов сигналов синхронизации магистрали устройства соответственно, инверсный выход признака сбоя блока контроля подключен к входу первого блока синхронизации с <0 первого по третий, выходы которого подключены к входу выборки кристалла, к входу управления выдачей информации четвертого шинного формирователя и входам управления выдачей информации 45

Ч1 ф с первого по третий шинных формирователей, входы выборки кристалла которых подключены к входу логического нуля устройства, о т л и ч а ю щ е ес я тем, что, с целью уменьшения времени восстановления работоспособности эа счет организации повторных циклов вывода информации в магистраль, в него введен второй блок синхронизации, группы входов и выходов которого являются группой входов сигналов синхронизации от магистрали и группой выходов сигналов синхронизации к процессорам устройства соответственно, прямой и инверсный выходы признака сбоя блока контроля подключены к первому и второму входам второго блока синхронизации.

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что второй блок синхронизации содержит три элемента

ИЛИ, элемент И, два формирователя импульса, элемент задержки и счетчик, счетный вход которого является вторым входом блока и соединен через первый формирователь импульса с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу элемента

И, первый и второй входы которого соединены с первым входом группы и первым входом блока соответственно, первый вход элемента И соединен с первым входом сброса счетчика, первые входы второго и третьего элементов ИЛИ являются вторым и третьим входами группы блока, выход переполнения счетчика соединен с вторым входом третьего элемента ИЛИ и через элемент задержки — с вторым входом сброса счетчика, второй вход блока соединен через второй формирователь импульсов с вторым входом второго элемента ИЛИ, выходы с первого по третий элементов ИЛИ являются выходами группы блока.

1304031

Составитель А.Ушаков

Техред В.Кадар Корректор С,Черни

Редактор М.Циткина

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035) Москва, Ж-35, Раушская наб., д. 4/5

Заказ 1313/50

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4