Способ аналого-цифрового преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Цель изобретения повышение быстродействия. Для достижения поставленной цели в способ поразрядного аналого-цифрового преобразования (АЦП) вводятся дополнительные операции формирования дополнительного аналогового сигнала и суммирование его с компенсирующим сигналом перед сравнением с входным сигналом. Устройство, реализующее заявленный способ, содержит аналоговый вход 1, блок 2 сравненияS счетчик 3 адреса, генератор 4 иьшульсов, управляющий вход 5 запуска, цифроаналоговый преобразователь 6, блок 7 элементов ИЛИ, регистр 9 последовательного приближения, первый цифровой выход 10, второй цифровой выход 11. Формирование дополнительного аналогового сигнала и использование избыточных измерительных кодов позволяет сократить длительность такта уравновешивания, что повышает быстродействие АЦП. 1 ил. о (О сл с со о 4

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ6ЛИН (51)4 Н 03 Г! 1/26 у

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ABT0PCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (2!) 394198!/24-24 (22) 08.07.85 (46) 15.04.87. Бюл. Ь - 14 (72) А.П.Стахов, А.Д.Азаров, В.Я.Стейскал, В.И.Моисеев и В.П.Марценюк (53) 681,325 (088.8) (56) Лаврентьев В.Н., Клочан П.С., Аналого-цифровые преобразователи двустороннего уравновешивания, Киев. Знание, 1982, с,22, Балакай В.Г. и др. Интегральные схемы аналого-цифровых и цифроаналоговых преобразователей ° — Yi. . Энергия, 1978, с. 45, рис. 1-13. (54) СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ (57) Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Цель изобретения

„„SU„„1304172 А1 повышение быстродействия. Для достижения поставленной цели в способ поразрядного аналого-цифрового преобразования (АЦП) вводятся дополнительные операции формирования дополнительного аналогового сигнала и суммирование его с компенсирующим сигналом перед сравнением с входным сигналом, Устройство, реализующее заявленный способ, содержит аналоговый вход l блок 2 сравнения, счетчик 3 адреса, генератор 4 импульсов, управляющий вход 5 запуска, цифроаналоговый преобразователь 6, блок

7 элементов ИЛИ, регистр 9 последовательного приближения, первый цифровой выход 10, второй цифровой выход ll. Формирование дополнительного аналогового сигнала и использование избыточных измерительных кодов позволяет сократить длительность такта уравновешивания, что повышает быстродействие АЦП. 1 ил.

1304172

В предлагаемом способе аналогоцифрового преобразования формирование сигнала Ак на основе избыточного измерительного кода (ИИК) исключает недоуравновешивание входного сигнала йри появлении ошибок типа "неправильное выключение разряда" вслед55

Изобретение относится к автоматике и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. 5

Цель изобретения — повышение быстродействия аналого-цифрового преобразования.

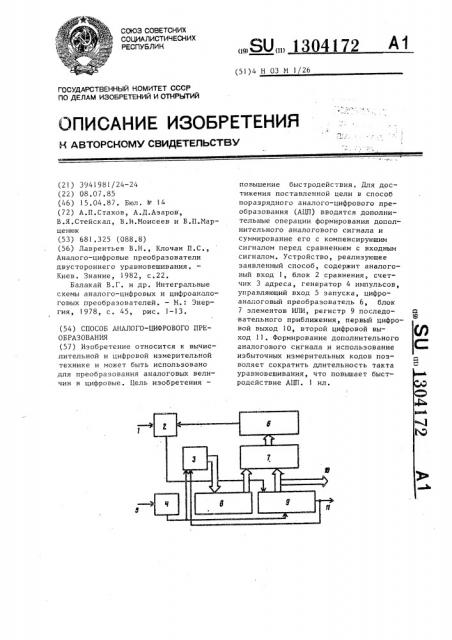

На чертеже приведено устройство, реализующее предлагаемый способ .аналого-цифрового преобразования.

Устройство содержит аналоговый вход 1, блок 2 сравнения, счетчик 3 адреса, генератор 4 импульсов, управляющий вход 5 запуска, цифроаналоговый преобразователь (ЦАП) 6, блок 7 элементов ИЛИ, блок 8 посто— янной памяти, регистр 9 последов-тельного приближения, выходные шины

10, выход 11 окончания преобразования, Сущность способа аналого-цифрового преобразования заключается в следующем.

При выполнении аналого-цифрового

25 преобразования путем поразрядного уравновешивания осуществляют компенсацию входного аналогового сигнала

А „ компенсирующим аналоговым сигналом А . При этом преобразование происходит правильно, если на последнем такте осуществляется уравновешивание А .сигналом А„ с точностью

Ьх до единицы младшего разряда ПАП.

Для этого необходимо, чтобы t > t„, 35 где t — - длительность одного такта преобразования; t — номинальное значение длительности такта, Если длительность такта t будет меньше значения t„, то уравновешивание мо- 40 жет произойти неверно, вследствие неточного установления значения A и появление ошибок типа "неправиль.ное включение разряда или "неправильное выключение разряда". При 45 формировании компенсирующего сигнала

А„ на основе двоичного кода появление и первого и второго типов указанных ошибок кодирования приводит к неправильному уравновешиванию вход- 50 ного сигнала А,„ сигналом Ак. ствие возможности компенсации этого типа ошибки в ИИК обладающем избыР тОчностью, Для того, чтобы при аналого-цифровом преобразовании исключить ошибку типа "неправильное включение разряда введена несимметрия в процессе уравновешивания входного сигнала, заключающаяся в том. что на каждом

i-ом такте поразрядного уравновешивания одновременно с формированием компенсирующего сигнала формируется дополнительный аналоговый сигнал величиной где и — число разрядов кода; Q; — вес

i-го разряда ИИК, при этом 0; = 0;-,/, где 1 g,< 2 — основание ИИК, который суммируется с компенсирующим сигналом поразрядного уравновешивания, а сравнение входного сигнала производится с результатом суммирования.

Это приводит к тому, что действующий на i-ом такте вес i-ro pagp pa увеличивается. При этом, если разность входного и компенсирующего сигналов в конце предыдущего такта уравновешивания превышала незначительно вес i-го разряда, то в текущем такте произойдет выключение -го разряда и дальнейшее уравновешивание будет производиться последующими младшими разрядами. Таким образом исключается ошибка типа "неправильное включение разряда".

Данные обстоятельства позволяют значительно уменьшить длительность такта поразрядного кодирования, вследствие отсутствия производить точное, до половины веса младшего разряда сравнение входного и компенсирующего сигналов. Это сравнение достаточно производить с некоторой относительной погрешностью о . Значение о зависит от избыточности кода и определяется по формуле

3= 2 — 1

Для чисел Фибоначчи, например, значение о равно 23,бЕ, Устройство, реализующее данный способ, работает следующим образом.

Цикл аналого-цифрового поразрядного кодирования начинается после прихода сигнала "Запуск на управляющий вход 5. При этом на выходе ре13041

72 4 тается в единичном состоянии /у =1/.

На последующих тактах работа устройства происходит аналогично. После окончания и тактов поразрядного уравновешивания на выходных шинах !

О находится код Квых являющийся цифровым эквивалентом входного аналогового сигнала А „,, а на выходе 11 сигнал окончания преобразования.

Формула из о я

Способ аналого-ци разования,основанный м уравновешивании входи го сигнала, заключающийс на каждом i-ом такте мпенсирующий аналогов У ществляют сравнение в гового сигнала с компен оговым сигналом и запо тат сравнения, о т л с я тем, что, с цель ыстродействия, одновреме ованием компенсирующег сигнала формируют доп налоговый сигнал величи

И

Q ° — Q + 1

=j

2 разрядов кода; Q; — вес i-го разряда, и перед сравнением с входным аналоговым сигналом суммируют компенсирующий и дополнительный аналоговые сигналы, а сравнение входного аналогового сигнала осуществляют с сигналом результата суммирования, при этом формирование компенсирующего аналогового сигнала осуществляют на основе избыточного измерительного кода с весами Q< = Q,,/ot ., где 1 о 2— основание избыточного измерительного следующему условию. у; E (0,1) О, А„аА„, 20 кода.

Составитель В.Першиков

Техред И.Попович Корректор Е.Рошко

Редактор M.Òîâòèí

Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д,4/5

Заказ 1324/57

Производственно-полиграфическое предприятие, г.ужгород, ул,Проектная,4

3 гистра 9 последовательного приближе- . ния устанавливается в единичное состояние старший 1-й разряд (остальные разряды имеют нулевое значение).

На выходе блока 8 устанавливается код 5

К,/bQ,/, полученный на основании выражения (1) и записанный в блок 8 на этапе изготовления. Через блок 7 коды с выходов регистра 9 последовательного приближения и блока 8 поступают 10 на вход ЦАП 6, в котором происходит формирование и суммирование основного компенсирующего и дополнительного сигналов. На выходе ЦАП 6 появится компенсирующий аналоговый сигнал А = 15

К(= Q<+ йЦ, . Сравнение сигналов А „и

A к„ производится в блоке 2, выходной сигнал у, которого подчиняется

При этом, если на первом такте уравновешивания у, = О, то 1-ый разряд устанавливается в нулевое состо-: яние, если же у = 1, то 1-ый разряд ! остается в единичном состоянии на последующих тактах уравновешивания.

На втором такте аналого-цифрового 30 преобразования по сигналу генератора 4 импульсов изменяется на единицу содержимое счетчика 3 адреса и на выходе. блока 8 устанавливается код

К /bQz(, причем К /bQ,I= = К(/AQ, /:2. 35

Одновременно на выходе регистра 9 последовательного приближения устанавливается в единичное состояние

2-ой разряд. После очередного сравнения входного и компенсирующих сигна- 40 лов 2-ой разряд либо устанавливается в нулевое состояние /y =0/, либо осб р е т е н и фрового преоб на поразрядно ого аналогово я в том, что формируют ко

ый сигнал, ос ходного анало сирующим акал минают резуль и ч а ю щ и и ю повышения б нно с формир о аналогового олнительный а ной А(};

Р ,где и — число