Устройство для вычисления полинома @ -ой степени

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных системах, работающих в реальном масштабе времени. С целью повьшения быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов в устройство, содержащее элементы 5, счетчик 8, блоки 9, 10 памяти , сумматоры 11, 12, коммутаторы 13, 14, регистр-мультиплексор 15, умножители . 19, 20, введены регистры 16- 18, триггеры 1-4 и злементы И 6, 7. 4 ил., СО о СП а

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ()9)SU(i() 57 А1 (51)4 G 06 F 7/544

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ !

Фиг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3955344/24-24 (22) 23. 09.85 (46) 23.04.87. Бюл. Ф 15 (71) Одесский политехнический институт (72) В.А.Парасочкин, Е.Л.Полин, В.Г.Ткаченко и А.В.Дрозд (53) 681,325(088.8) (56) Авторское свидетельство СССР

Ф 962973, кл, Г 06 F 15/31, 1982.

Авторское свидетельство СССР

И- 1140115, кл, G 06 F 7/544, 1983. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИH0N0B и-Й СТЕПЕНИ (57) Изобретение относится к вычислительной технике и может быть исполь зована в измерительно-вычислительных системах, работаюших в реальном масштабе времени. С целью повышения быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов в устройство, содержащее элемент И 5, счетчик 8, блоки 9, 10 памяти, сумматоры 11, 12, коммутаторы

13, 14, регистр-мультиплексор 15, умножителн 19, 20, введены регистры 1618, триггеры 1-4 и элементы И 6, 7.

4 ил.

1305670

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных системах, работающих в реальном масштабе времени. 5

Цель изобретения — повышение быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов .

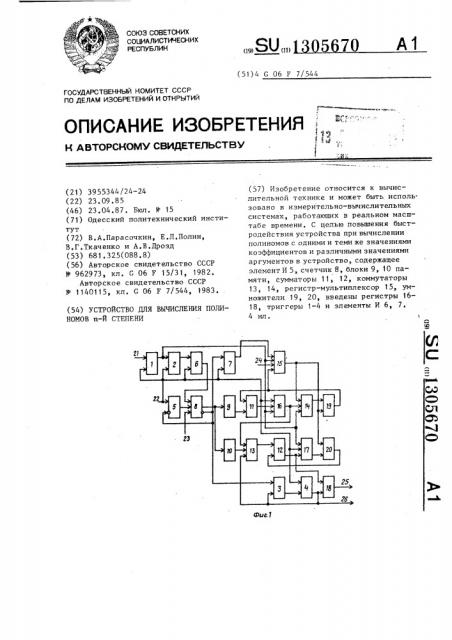

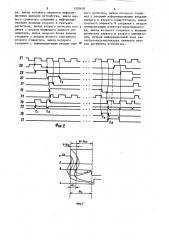

На фиг.1 представлена функциональная схема устройства; на фиг.2 — циалограмма его работы; на фиг.3 — временная диаграмма работы триггеров; на фиг.4 — триггеры.

Устройство содержит триггеры 1-4, элементы И 5-7, счетчик 8, блоки 9 и 10 памяти, сумматоры 11 и 12, коммутаторы 13 и 14, регистр-мультиплексор 15, регистры 16-18, умножители 19 и 20, входы запуска 21, синхронизации

22, значений степени 23 и аргумента

24, выходы информационный 25 и сигнала окончания цикла работы 26.

На циалограмме (фиг.2) показаны импульсы синхронизации 27 и запуска

28 состояния на выходах: 29 — первого триггера 1, 30 - второго триггера 2, 31 — второго элемента И 6, 32 « заема счетчика, 33 — первого элемента И 5, 34 - третьего элемента И 7, 35 - регистра-мультипликатора 15, 36 - третьего триггера 3, 3? — четвертого триггера 4.

Устройство реализует алгоритм вьг- чиспения полиномов по формуле

Y=X((...(a„X +а„2)Х +...+а )Х +a„j+

+ I(... (а х а„) х +...+в )х +а,).

° ° ° 1 3 ° ° 2 о ° 40

Устройство работает следующим образом.

В исходном состоянии в первом блоке 9 памяти размещены значения коэффициентов а„ „, а„,..., а, во вто 45 ром блоке 10 памяти — значения коэффициентов а„, а,..., а„. Счетчик 8 находится в нулевом состоянии.

На вход 21 поступает сигнал "Пуск", по которому первый триггер 1 выраба- 0 тывает импульс Т1 с длительностью, равной периоду синхросигналов (СИ), под действием которого триггер 2 вырабатывает импульс Т2, поступающий

„.э через элемент И 6 на счетный вход счетчика 7. При этом разряд заема на выходе счетчика переходит из нулево- го состояния в единичное. Разряд заема поступает на вход первого элемента

И 5, разрешая прохождение СИ на счетный вход счетчика 8.

Инверсное значение разряда заема подается на вход третьего элемента И

7, запрещая прохождение СИ на синхровход регистра 15 в процессе счета счетчика 8. При этом в момент t„ s регистр 15 через его второй информационный вход записывается значение аргумента Х1. С выхода регистра 15 значение аргумента поступает на входы первого умножителя 19 (непосредственно на первый вход) и через первый коммутатор 14 " на второй вход. Первый коммутатор 14 подключает выход регистра 15 к входу первого умножителя 19 на время действия импульса Т1, поступающего на. управляющий вход первого коммутатора 14. С выхода первого умножителя 19 снимается величина (Х1)2 записываемая в регистр 15 через его первый информационный вход в момент времени t и сохраняемая в нем до окончания счета счетчика 8. Запись в регистр 15 через первый информационный вход разрешается на время действия импульса Т1, поступающего íà его управляющий вход. С приходом импульса

Т1 на входы сброса первого 16 и второго 17 регистров эти регистры обнуляются (в момент времени t„„) и сохра-, няют нулевое состояние до момента t>, Это обеспечивает обнуление выходов первого 19 и второго 20 умножителей от момента времени е, до момента времени t . .На этом интервале времени из первого 9 и второго 10 блоков памяти считываются записанные по адресу п/2 коэффициенты а„ „ и а„ соответственно.

Эти коэффициенты складываются на первом 11 и втором 12 сумматорах с нулевыми значениями, поступившими с выходов умножителей, и записываются с приходом СИ в первый 16 и второй 17 регистры соответственно. В следующем такте работы устройства коэффициенты а„. 1 и а„ поступают на входы первого

19 и второго 20 умножителей, где домножаются на величину (Х1)2, а затем складываются на первом 11 и втором 12 сумматорах со считанными по адресу (и - 1)/2 — 1 из первого 9 и второго 10 блоков памяти коэффициентами а и а 2 . Результаты суммирования записываются соответственно в первый 16 и второй 17 регистры. В последующих тактах результаты, снимаемые с выходов

3 13056 первого 16 и второго 17 регистров, домножаются на величину (Х1) и складываются с очередными считанными коэффициентами аналогично описанному.

Порядок считывания коэффициентов из блоков памяти определяется счетчиком

8, с выхода которого код состояния поступает на управляющие входы блоков памяти. При достижении счетчиком 8 нулевого состояния и с приходом зад- 1Р него фронта СИ разряд заема на выходе счетчика 8 принимает нулевое значение и запрещает дальнейшее поступление синхросигналов на счетный вход счетчика 8. Инверсное значение разря- 15 да заема передним фронтом устанавливает третий триггер 3 в единичное состояние в момент времени с,, С приходом очередного СИ единичное значение третьего триггера 3 перепи- 20 сывается в четвертый триггер 4, сбрасывающий сигналом с инверсного выхода третий триггер 3 в нулевое состояние.

Следующий СИ переводит четвертый триггер 4 в нулевое состояние. 25

Таким образом, формируется импульс

Т4. Изменившееся значение разряда заема на выходе счетчика 8 вновь разрешает прохождение СИ на вход регистра

15, принимающего к моменту времени ЗО значение аргумента Х1. Импульс Т4 с выхода четвертого триггера 4 поступает на управляющий вход второго коммутатора 14, обеспечивая на время действия импульса Т4 подключение выхода З5 первого регистра 16 к второму входу второго сумматора 12. На первый вход второго сумматора 12 поступает результат с второго регистра 17, домноженный на втором умножителе 20 на 40 значение аргумента Х1. С выхода второго сумматора 12 снимается значение полинома и-й степени, записываемое в регистр 18 по заднему фронту импульса

Т4. С выхода регистра 18 значение по-45 линома снимается на выход 25 устройства. Кроме того, на выход 26 устройства подается импульс Т4 с выхода четвертого триггера 4. Передним фронтом импульс Т4 сообщает о возможности50 подачи на вход 24 нового значения аргумента (например, Х2) и сигнала

"Пуск" на вход 24. Задним фронтом импульса Т4 сообщается информация о завершении вычисления полинома. 55

Ф ор мула и зо бр ет ения

Устройство для вычисления полинома и-й степени, содержащее два блока

70 4 памяти, два сумматора, два коммутатора, два умножителя, регистр — мульти— плексор, счетчик и первый элемент И, первый вход которого является входом синхронизации устройства, выход первого элемента И соединен с вычитающим входом счетчика, информационный выход которого соединен с адресными входами первого и второго блоков памяти, выход первого блока памяти соединен с первым информационным входом первого коммутатора, выход которого соединен с входом первого слагаемого первого сумматора, вход второго слагаемого

l которого соединен с выходом первого умножителя, выход второго умножителя соединен с входом первого слагаемого второго сумматора и первым входом данных регистра-мультиплек сора, выход которого соединен с первым информационным входом второго коммутатора, выход которого соединен с входом мнохммого второго умножителя, о т л и— ч ающе е с я тем, что, сцельюповышения быстродействия устройства при вычислении полиномов с одними и теми же значениями коэффициентов и различными значениями аргументов, в него введены четыре триггера, второй и третий элементы И, три регистра, первые входы второго и третьего элементов И и синхровходы первого и второго регистров и с первого по третий триггеров соединены с входом синхронизации устройства, информационный вход первого триггера является входом запуска устройства, выход первого триггера соединен с управляющими входами регистра-мультиплексора и второго коммутатора, входами сброса первого и второго регистров и информационным входом второго триггера, выход которого соединен с вторым входом второго элемента И, выход которого соединен с синхровходом счетчика, параллельный вход данных которого является входом показателя степени устройства, инверсный выход разряда заема счетчика соединен с вторым инверсным входом первого элемента И, вторым входом третьего элемента И и входом установки четвертого триггера, выход которого соединен с информационным входом третьего триггера, выход которого является выходом сигнала окончания цикла работы устройства и соединен с управляющим входом первого коммутатора, входом сброса четвертого триггера и входом синхронизации третьего регист1305670

27 б ° °

2д

° ° Ф

° ° б

Ф ° °

° ° °

° ° 1

° °

° б б б ° В б ° б

° ° Ф ра, выход которого является информационным выходом устройства, выход первого сумматора соединен с информационннъии входами второго и третьего регистров, выход второго регистра соединен с входом множимого первого умножителя, выход второго блока памяти соединен с входом второго слагаемого второго сумматора, выход которого соединен с информационным входом пер29

Л

З2

ЗЗ

ЗФ

35 вого регистра, выход которого соединен с .вторыми информационными входами первого и второго коммутаторов, выход третьего элемента И соединен с входом синхронизации регистра-мультиплексора, выход которого соединен с входами множителя первого и второго умножителей, второй информационный вход регистра-мультиплексора является входом аргумента устройства.

Составитель Н.Матвеев

Редактор Н.Рогулич Texpep JI.9ëeéíèê Корректор А.Зимокосов

Заказ 1452/46 Тирах 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская иаб., д. 4/5

Производственно-полиграфическое предприятие, r.Óàrîðoä, ул.Проектная, 4