Устройство для вычисления функции двоичной экспоненты

Иллюстрации

Показать всеРеферат

Изобретение касается цифровой вычислительной техники и может быть использовано при построении специализированных вычислителей,, информационно-измерительных систем и цифровых устройств для обработки сигналов. Цель изобретения - уменьшение объема памяти. В состав устройства входят регистр 1, первый и второй блоки 3 и 4 памяти, коммутатор 2, три сумматора 6, 7, 8 и блок 5 элементов НЕ. В данном устройстве уменьшение объема памяти достигается за счет использования кусочно-линейной функции коррекции , аппроксимирующей разность @ (Л

СОЮЗ СОВЕТСНИХ

СО0ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (0 4 G 06 F 7/556

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3974836/24-24 (22) 05.11.85 (46) 23.04.87. Бюл. N - 15 (72) Ю.В.Хохлов, А.N.ËHòBèí, В.Д.Циделко и С.В.Шантырь (53) 681.325(088.8) (56) Циделко В.Д., Хохлов Ю.В. К вопросу построения вычислительных устройств логарифмирования и потенцирования. — Управляющие системы и машины, 1981, М - 5, с.24-29, рис. I °

Авторское свидетельство СССР

И- 1238066, кл. G 06 F 7/556, 1984.

„„SU„„1305675 А 1 (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ ДВОИЧНОЙ ЭКСПОНЕНТЫ (57) Изобретение касается цифровой вычислительной техники и может быть использовано при построении специализированных вычислителей,. информационно-измерительных систем и цифровых устройств для обработки сигналов.

Цель изобретения — уменьшение объема памяти. В состав устройства входят регистр 1, первый и второй блоки 3 и 4 памяти, коммутатор 2, три сумматора 6, 7, 8 и блок 5 злементов НЕ.

В данном устройстве уменьшение объема памяти достигается за счет использования кусочно-линейной функции кор- Я рекции, аппроксимирующей разность

1305675

1ау1(х)!„„с (2 между исходной функцией и ее линейным приближением, а также за счет. использования симметрии функции корИзобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных вычислителей, цифровьгх устройств для обработки сигналов, гибридных функциональных преобразователей и информационно-измерительных систем, при восстановлении и сжатии сигналов, при цифровой нелинейной обработке звуковых и видеосигналов в устройствах реального времени.

Цель изобретения — уменьшение объема памяти.

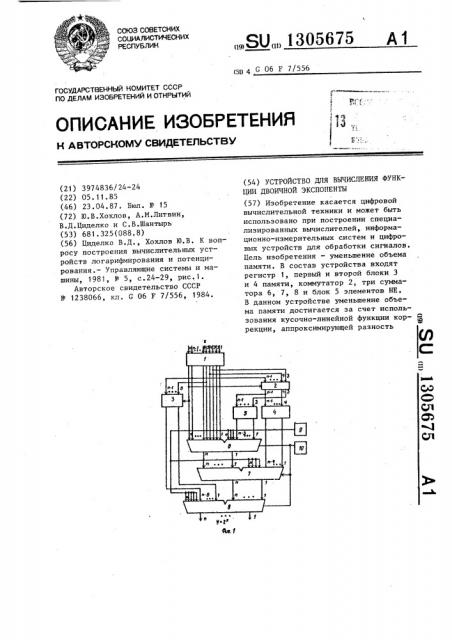

На фиг.1 приведена структурная схема устройства для вычисления функции двоичной экспоненты; на фиг.2 — эпюры, поясняющие принцип преобразования.

Устройство для вычисления функции двоичной экспоненты содержит регистр

1, коммутатор 2, первый и второй блоки 3 и 4 памяти, блок 5 элементов HE третий, первый и второй сумматоры

6-8, входы 9 и 10 логических нуля и единицы.

Работа устройства для вычисления

Х функции двоичной экспоненты у = 2 где х E. (0;i) (в дальнейшем . — исходной функции), основана на кусочнолинейной аппроксимации этой функции с последующей коррекцией разности, называемой функцией коррекции, между исходной функцией и ее линейным приближением.

На фиг.2a показана аппроксимация функции у = 2", x t j0 1) прямой линией, откуда видно, что входной код содержит часть информации о выходной величине и может использоваться как грубое приближение исходной функции, Разность между исходной функцией и ее линейным приближением ду (х)=

Х

2 . — (x+ 1) показана на фиг.2$. Анализ функции ду (х) показывает, что рекции, устранения двузначности функции коррекции и введения второго канала коррекции, 2 ил.

Построим функцию,(х), которая является кусочно-линейной аппроксимацией функции разности д у„(х) на интервалах х E ГО, 1/2) и х E-(1/2, 1), 5 таким образом, чтобы

-2 (x), х Е (О, 1/2);

4 1 (х) = (2)

-2 (1-х), х E (1/2, 1), т.е. функция „(х) — симметрична от носительно оси, проведенной через точку х = 1/2. Вычисления g,(x) на интервале г О, 1/2), т.е. умножение

-3 кода аргумента х на коэффициент -2 соответствует операции сдвига на три разряда влево и не представляет трудностей при практической реализации, а вычисление (х) на интервале

Ei/2, 1) может выполняться аналогично, если в качестве аргумента брать дополнение х до 1, т.е. обратный ход Х, что возможно вследствие сим2$ метрии Функции ч „(х) .

Разность между функциями д ул(х) и y„(x); д у (х) = д у (х) — y (х) показана на фиг.2$. Построим фуйкцию (х), которая является симметричным отображением функции ay>(x) для значений X E. О, 1/2) относительно оси, проведенной через точку х = 1/2 (фиг.2 6 пунктир).

Значения функции (х) на интервале (О, 1/2) рассчитывается заранее и помещаются во второй блок памяти.

Очевидно, что для получения функции

j»(x) на интервале x e f1/2, 1) необходимо брать дополнение аргумента до

40 1. Вследствие построенной симметрии функция j (х) совпадает с функцией

2 ду (х) на интервале х E (0, 1/2) .

Функция разности ду (х) = йу2(х)—

V2(х) (фиг. 2 6), значения которой запоминаются в первом блоке памяти и служат для получения точного результата преобразования на интервале х Е Г1/г, 1).

2-3 х

У х E 0, 1/2);

+„(x) =

3 13056

Записывают уравнения для аппроксимирующих и корректирующих функций: ду (х) 2 -(х+1), х (О, 1); (3) (4)

-2 (1-х), х E (1/2, 1); (д у„(х) — „(x), x e (0, 1/2); (5)

2 (ду (х) — 4, (1-х), хе(1/2, 1); 10

4 (1-х) = а у (1-х), х е C1/2, 1); (б) ду (х)= д У2(х) Ó (1-х), хб(1/2, 1) .

AHBJIH3 функции +2 (X) H g y (x) зывает, что

42 с(2 и д у3мс кс с -2

-5 6

Таким образом, объемы блоков памя20 ти, необходимых для запоминания корректирующих функций V>(x) и д УЗ (х), равны

n-<

Q„= Q ду (х) = (n — б) 2 .2 (n — б) 2, бит. и-5 (8)

25 п-5

Q Qq2(х) = (и — 5) 2 .2 (п — 5) 2, бит; (9)

Дополнительное умножение на два в выражениях (8) и (9) учитывает двузначность (в математическом смысле) функций у (х) и ду З(х) .

Итоговое уравнение преобразования 35 можно записать следующим образом: интервал х E (О, 1/2): у(х) =(х+1)+ V„(x)+ М (х) (10)40 х E 1/2, 1): у(х) =(х+1)+ +< (1-х) +

+ у (1 x) + д у3 (х)

Корректирующая функция дуз(х) на интервале хЕ (О, 1/2) не использует- 4> ся. В качестве аргумента для функций

+<(x) и (х) на интервале х е (1/2, 1) берется дополнение Х до единицы, т.е. его обратный код.

Таким образом, работа коммутатора

2 заключается в том, что для значений х О, 1/2) он пропускает значения аргумента X без изменения, а для х Е 1/2, 1) значения аргумента х инвертируются. Управлени коммутатором 55

° осуществляется старшим разрядом кода аргумента x .. Практически коммутатор реализуется на схемах сложение по модулю два.

Сумма (х+1) + ч,(х) или сумма (х+1) + ч (1-х) образуется на выхо1 дах сумматора 6.

Преобразование вида у (х) = -2 х или у (х) = -2 - (1-х) выполняет1 ся путем соединения выходов коммутатора с (n-3) входами младших разрядов первого слагаемого сумматора 6, что соответствует пространственному сдвигу на три разряда влево кода аргумен- та х и (1-х), т.е. умножению х или (1-х) на 2 .

Из блоков 3 и 4 памяти выбираются соответственно значения корректирующих функций д у (х) и y> (x) или (1-х) и поступают на входы сумматоров 8 и 6 (фиг.1) и на выходе сумматора

8 получается окончательный результат.

Если функции М„(х), (х), ky< (х) д у (х), д у (х) отрицательные, для получения верного результата необходимо осуществить преобразование значений упомянутых функций в дополнительный код, Последнее преобразование сводится к тому, что на практике в блоки 3 и 4 памяти следует записывать значения и в обратном коде, а к входам переноса сумматоров 6-8 подключается вход логической единицы, обеспечивая таким путем получение дополнительного кода непосредственно на сумматорах.

Формула изобретения

Устройство для вычисления функций двоичной экспоненты, содержащее регистр, первый и второй блоки памяти, коммутатор, первый и второй сумматоры, причем вход аргумента устройства соединен с информационным входом регистра, выходы с пятого по (и-1)-й разрядов которого соединены с адресными входами первого блока памяти, где и — разрядность аргумента, выход и-го разряда регистра соединен с управляющими входами первого блока памяти и коммутатора, выходы с третьего по (п-1)-й разрядов регистра соединены с информационными входами коммутатора, выходы старших разрядов которого соединены с адресными входами второго блока памяти, выходы которого соединены с входами с первого по (n-4)-й разрядов первого слагаемого первого сумматора, выход которого подключен к входу первого слагаемого второго сумматора, выход которого яв1305675

Х р К

ay(xl, W ю (х) 4Д! (Pf) Составитель А.Шуляпов

Техред Л.Олейник Корректор A.Обручар

Редактор Н,Рогулич

Заказ 1452/46 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб...д„ 4/5

Производственно-полиграфическое предприятие, r.Yæãoðoä, ул.Проектная, 4

5 ляется выходом результата устройства, выходы первого блока памяти соединены с входами с первого по (и-5)-й разрядов второго слагаемого второго сумматора, входы переносов первого и второго сумматоров подключены к входу логической единицы устройства, вход логического нуля которого подключен к входам четырех старших разрядов первого слагаемого первого сумматора 10 и к входам пяти старших разрядов второго слагаемого второго сумматора, о т л и ч а ю ш е е с я тем, что, с целью уменьшения объема памяти, в него введены третий сумматор и блок 15

6 элементов НЕ, входы которого поразрядно подключены к выходам коммутатора, выходы блока элементов НЕ соединены с входами с первого по (п-3)-й разрядов первого слагаемого третьего сумматора, выход которого соединен с входом второго слагаемого первого сумматора, выход регистра соединен с входом второго слагаемого третьего сумматора, вход переноса которого соединен с входом логической единицы устройства, входы трех старших разрядов первого слагаемого третьего сумматора подключены к входу логического нуля устройства.