Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении ЦВМ. Цель изобретения - повышение быстродействия. Устройство содержит регистр 1 маски, группу элементов И 2, регистр 3 условий , регистр 4 адреса, дешифратор 5, блок 6 памяти микропрограмм, регистр 7 микрокоманд, входы 8 условий, вход 9 кода маски условий, элемент ИЛИ 13. За счет уменьшения времени реакции устройства на логические условия достигнута цель изобретения. 4 ил. со ел Oi сх

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) (51) 4 G 06 F 9/46

OllHCAHHE ИЗ0БРЕтанИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3993699/24-24 (22) 20.12.85 (46) 23.04.87. Бюл. Н- 15 (72) В.А. Кривего, Е.В. Глонти, В.А. Полеха и В.В. Кривего (53) 681.32(088.8) (56) Авторское свидетельство СССР

9 855665, кл. G 06 F 9/46, 1981.

Авторское свидетельство СССР

У 1126956, кл. G 06 F 9/46, 1984. (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано при построении ЦВМ. Цель изобретения — повышение быстродействия.

Устройство содержит регистр 1 маски, группу элементов И 2, регистр 3 условий, регистр 4 адреса, дешифратор 5, блок 6 памяти микропрограмм, регистр

7 микрокоманд, входы 8 условий, вход 9 кода маски условий, элемент ИЛИ 13.

3а счет уменьшения времени реакции устройства на логические условия достигнута цель изобретения. 4 ил.

1 130568

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах.

Цель изобретения — повышение быст5 родействня.

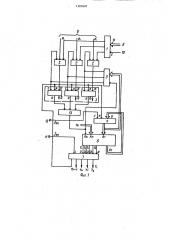

На фиг. i представлена функциональная схема микропрограммного устройства управления; на фиг. 2 — временная диаграмма его работы; на 10 фиг. 3 — временная диаграмма формирования полного адреса; на фиг, 4 — апгоритм работы микропрограммного устройства управления.

Микропрограммное устройство управ- 15 ления предназначено для регистрации и обработки сигналов запросов в зависимости от заданной дисциплины приоритета.

Микропрограммное устройство управ- 20 ления (фиг. 1) включает регистр 1 маски, группу элементов И 2, регистр

3 условий, регистр 4 адреса, дешифратор 5, блок 6 памяти микропрограммы, регистр 7 микрокоманд, входы 8 условий, вход 9 кода маски условий, первый 10, второй 11 и третий 12 тактовые входы, элемент ИЛИ 13 и входы 14 задания приоритета логических условий.

Устройство работает следующим об- 30 разом.

На регистр 1 маски по входу 9 кода маски передним фронтом тактового импульса с шины 10 заносится код маски, т.е. код, который регламентирует 35 номенклатуру обрабатываемых условий.

Нулевое содержимое какого-либо из разрядов этого кода запрещает дальнейшее прохождении соответствующего условия, поступающего по входам 8 логи- 40 ческих условий на соответствующий элемент И 2.

Прием (с шин 8) условий на регистр

3 логических условий, состоящий из р-триггеров, производится путем опро- 15 са их (на элементах И 2) сигналами с выхода дешифратора 5, формируемыми в зависимости от заданной дисциплины обработки условий.

Блок микропрограммного управления 50 работает следующим образом.

На блок 6 памяти микропрограмм задается адресный код А, состоящий из базового адресного кода АБ, склеенного с адресным .кодом подпрограммы об- 55 работки запросов А и текущим значея нием адресного кода А т"

А =- .А Ап ° Ат

1 2

Коды в выражении (1) записаны в

Ав=log k

A =Eogm (2) Блок 6 памяти микропрограмм представляет собой постоянный или полупостоянный информационный накопитель, каждому значению адресного кода в котором соответствует определенная ячейка памяти, состоящая из и разрядов. При подаче адресного кода на адресный выход блока 6 памяти микропрограмм на его выходе считывается соответствующее микропрограммное слово.

Разрядность и-микропрограммного слова, т.е. разрядность блока 6 памяти микропрограмм, определяется количеством управляющих микрокоманд V.

1 и разрядностью текущего адреса А г (3) и =Ч Ат, Исходя из выражения (3), блок 6 памяти микропрограмм можно условно разделить на две части, содержащие группу разрядов.

В первой группе разрядов кодируются микрокоманды, во второй — значения текущего адреса А соответствии с их весами, при этом старшим является А

Базовый адресный код Л (фиг. 3) представляет собой однобитовый сигнал, единичное значение которого обозначает наличие сигнала единичного условия на входе устройства, нулевое значение А6 — отсутствие единичного условия.

Адресный код подпрограммы обработки условия A определяет зону блока 6 памяти микропрограмм, в которой размещены подпрограммы обработки условий, включающие подпрограммы опроса условий с различной дисциплиной их обработки. Адресный код Ап задается от внешних (по отношению к предлагаемому) устройств. Разрядность

его определяется пользователем в зависимости от номенклатуры k реализуемых подпрограмм обработки условий.

Текущий адресный код Ат определяет порядок выборки микропрограммных слов, составляющих соответствующую подпрограмму обработки условий. Разрядность этого кода определяется количpcTBом микропрограммных слов m в самой длинной из подпрограмм где Топ п1

3 13056

Значение микрокоманд, т.е. значение первой группы разрядов, поступает на информационный вход регистра 7 микрокоманд, где фиксируется передним фронтом импульса инверсной серии формируемой на входе 11 устройства.

Значение текущего адреса поступает на информационный вход регистра 4 адреса, где фиксируется передним фрон- fp том импульса прям0й серии f „, формируемой на входе 12 устройства.

В каждой предыдущей ячейке в разрядах А блока 6 памяти микропрограмм фиксируется (программируется) адрес t5 следующего программного слова. В последнем микропрограммном слове фиксируется адрес первого микропрограммного слова, тогда при непрерывном считывании этих слов формируется цик-gp лическая программа, образуемая кодами, представленными первой группой разрядов блока 6 памяти микропрограмм.

Темп реализации такой программы, а также длительность микрокоманды оп- 25 ределяются частотой импульсов foä, формируемой на входе 12 устройства.

При этом длительность микрокоманды

Т > определяется

Т =Т„п„, (4) 30

1 — длительность периода импульсов опорной частоты; — количество подряд запрограммированных единиц в соответствующем разряде ячейки блока 6 памяти микропрограмм.

Адресный код с выхода регистра 4 адреса поступает на дешифратор 5, где 40 дешифрируется в сигналы, осуществляющие опрос элементов И 2 и регистрацию сигналов с выходов этих элементов на триггерах регистра 3 логических условий. 45

При наличии какого-либо из логических условий соответствующий триггер регистра 3 логических условий устанавливается в единичное состояние, которое с Q-выхода этого триггера че-sp рез элемент ИЛИ 13 подается на старший разряд адресного входа АБ блока 6 памяти микропрограмм, меняя ход выполняемой подпрограммы опроса на программу обработки предлагаемого ус-55 ловия. В последнем слове подпрограммы формируется микрокоманда 7(„ „, которая сбрасывает на "0" содержание

81 4 триггеров регистра 3 логических условий и содержимое адресного регистра 4. формула изобретения

Микропрограммное устройство управления, содержащее регистр маски, группу элементов И, регистр логических условий, регистр адреса, дешифратор, блок памяти микропрограмм и регистр микрокоманд, выходы поля микроопераций которого соединены с управ- . ляющими выходами устройства, а информационные входы регистра микрокоманд соединены с выходами поля операций блока памяти микропрограмм, выходы поля адреса которого соединены с группой информационных входов регистра адреса, выходы которого соединены с младшими разрядами адресного входа блока памяти микропрограмм, первые входы элементов И группы соединены с входами логических условий устройства, вторые входы элементов И группы соединены с выходами регистра маски, информационный вход которого соединен с входом кода маски условий устройства, а вход записи регистра маски подключен к первому тактовому входу устройства, о т л и ч а ю— щ е е с я тем, что, с целью повышения быстродействия, второй тактовый вход устройства соединен с входом записи регистра микрокоманд, а третий тактовый вход устройства соединен с входом записи регистра адреса, выходы регистра адреса соединены с входами дешифратора, старший разряд адресного входа блока памяти микропрограмм соединен со стробирующим входом дешифратора и с выходом элемента

ИЛИ, остальные разряды адресного входа блока памяти микропрограмм подключены к входам задания приоритета логических условий устройства, выходы дешифратора соединены с третьими входами элементов И группы и синхронизирующими входами соответствующих раз-: рядов регистра логических условий, выходы элементов И группы соединены с информационными входами регистра логических условий, выходы которого подключены к входам элемента ИЛИ, вход установки в "О" регистра логических услов.:й соединен с выходом признака окон ания подпрограммы регистра микрокомаг.ц и с входом установки в "0" регистра адреса.

1305681

1305681

ыхоУ еишрр. 5

Cocmps ue сиежюаУ пррр

Ванин ео аююах д дыхоР ,юепеююоР

Cocmowaue триеаероФ

Юыкоо умей ил У йироноюак

У(л+1) Фиа 2

ЗкоУл аю о-

У

Уых иапупасо

Ьл

Выкоо рег. оо о.

ЗьаоУ &она вял и musion дь коР регисла нинроиоиайд

1305681

Ф r л ак о юе хо ы

8ыхо8 регистр адреса дыхЫ блока 8 иапюпи пикропроер. дьиаР

aoeocmp. Ю

Зиачаиие афеса Ар

Значение

norteoe0 ОУРГса

&ока Флагогти иинропрагр.

i 3056Я1

Составитель Г. Иошкин

Редактор Н. Рогулич Техред п Олейник Корректор Е. Рошко

Заказ 1452/ 46, Тираж 673 Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4