Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении постоянного запоминающего устройства (ПЗУ). Целью изобретения является повьшение надежности ПЗУ. Для этого в устройство введен формирователь напряжения контроля с соответствующими связями. Введение формирователя позволяет производить измерение токов утечки тран-- зисторов накопителя. При превышении токов утечки допустимого уровня негодные ПЗУ отбраковываются. 1 ил. оо о СП vl СП

СОЮЗ СОВЕТСНИХ СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 С 11 С 17/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3946259/24-24 (22) 20.08.85 (46) 23.04.87. Бюл. N 15 (72) 10 ° И.Щетинин, П.С.Приходько, Ап.А.Львович и Ан.А.Львович (53) 681.327.6 (088.8) (56) Валиев К.А., Орликовский А.А.

Полупроводниковые интегральные схемы памяти на биполярных транзистор-. ных структурах. — М.! Советское радио, 1979, с. 249.

Bipolar Memory PRON Series. AMD Inc 1980 р. 5-9.

„„SU 1305775 A 1 (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение. относится к вычислительной технике и может быть использовано при построении постоянного запоминающего устройства (ПЗУ).

Целью изобретения является повышение надежности ПЗУ. Для этого в устройство введен формирователь напряжения

1 контроля с соответствующими связями.

Введение формирователя позволяет производить измерение токов утечки транзисторов накопителя. При превышении токов утечки допустимого уровня негодные ПЗУ отбраковываются. 1 ил °

130

Изобретение относится к микроэлектронике и может быть использовано при

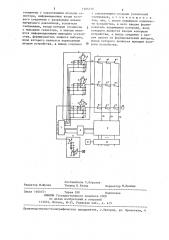

I построении электрически программируемых запоминающих устройств (ПЗУ), Целью изобретения, является повышение надежности устройства, На чертеже приведена схема предлагаемого устройства.

Устройство содержит матричный накопитель i состоящий из словарных шин (СШ) и разрядных шин (РШ), в местах пересечений которых расположены запоминающие ячейки, состоящие из и-р-п транзисторов плавких перемычек, дешифратор 2 слов, состоящий из элементов И, построенных на диодных сборках 3 и 4 и резисторах 5, и формирователей импульсов выборки строки, построенных на тиристорах 6, адресные формирователи 7, дешифратор 8 разрядов, селектор 9, выходные усилители 10, формирователь 11 напряжения контроля, состоящий из и-р-и транзисторов 12, трех диодов 13-15 р-п-р транзисторов 16 и двух резисторов 17 и 18, вход 19 и выход 20 контроля, формирователь 21 запрета выборки.

Устройство работает следующим образом.

Для измерения токов утечки матрицы на ПЗУ подают напряжение питания режима программирования, при этом все разрядные шины отключаются от остальной части ПЗУ и ток не должен протекать ни через какую-либо плавкую перемычку накопителя 1. При подаче на входы адресных формирователей 7 адресного коца, соответствую.щего словарной шине, которая соединена с выходом 20 контроля, на выбранной словарной шине установится уровень напряжения Ч, На невыбранных словарных шинах присутствует низкий потенциал, так как хотя бы один диод из диодных сборок 4 подключен своим катодом к одному из выходов адресных формирователей, находящемуся в состоянии логического "0".

При подаче на вход 19 контроля от внешнего формирователя напряжения разрешающего уровня напряжения включается транзистор 12 и на входе формирователя выборки словарной шины устанавливается низкий потенциал, определяемый цепью смещения из диодов

13-15 и р-и-р транзистора 16. При подаче на контролируемую контактную площадку от внешнего формирователя

5775 2 напряжения уровня напряжения V равного напряжению на выбранной словарной шине, в режиме программирования все переходы база — эмиттер транзисторов, подключенных к невыбранным словарным шинам, находятся под обратным смещением, а тиристор 6 дешифратора слов 2 оказывается выключенным, так как потенциал на его базе, определяемый формирователем 11 напряжения контроля ниже потенциала на катоде тиристора 6, определяемого уровнем напряжения внешнего формирователя напряжения. В результате, если есть утечка одного из переходов база — эмиттер транзисторов накопителя 1, то он легко может быть измерен подключением измерительного прибора между выходом 20 контроля и внешним формирователем напряжения У. Диоды

13-15, р-и-р транзистор 16 определяют уровень напряжения, вырабатываемый формирователем 11 напряжения контроля. Этот уровень должен быть, с одной стороны, достаточно низким, чтобы напряжение между базой и катодом тиристора 6 было меньше гранич" ного напряжения включения база — эмиттерного перехода тиристора 6, а с другой стороны, достаточно высоким, чтобы предотвратить пробой в цепи: внешний формирователь напряжения, подключенный к выходу 20 контроля, словарная шина — обратно смещенный переход база — эмиттер тиристора 6— формирователь 11 опорного напряжения.

С этой целью и включена в коллектор транзистора 12 цепь смещения,сос" тоящая из диодов 13-15 и р-п-р транзистора 16.

Формула изобретения

Постоянное запоминающее устройство, содержащее матричный накопиI тель, дешифратор слов, который состоит из элементов И и формирователей выборки, входы которых соединены с выходами соответствующих элементов И, а выходы соединены со словарными шинами матричного накопителя, дешифратор разрядов, селектор, адресные формирователи, входы которых являются адресными входами устройства, а выходы соединены с соответствующими входами соответствующих элементов И дешифратора слов и с входами дешифратора разрядов, выходы которого

1305775

Составитель С.Королев

Техред В.Кадар Корректор М.Демчик

Редактор И.Шулла

Заказ 1460/51 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4 соединены с управляющими входами селектора, информационные входы которого соединены -с разрядными шинами матричного накопителя, усилители считывания, входы которых соединены 5 с выходами селектора, а выходы являются информационными выходами устройства, формирователь запрета выборки, вход которого является управляющим входом устройства, а выход соединен с управляющими входами усилителей считывания, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введен формирователь напряжения контроля, вход которого является входом контроля устройства, а выход соединен с входом одного из формирователей выборки, выход которого является выходом контроля устройства.