Генератор многофазного квазисинусоидального напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано в схемах управления преобразователями частоты. Целью изобретения является упрощение и расширение функциональных возможностей. Под действием тактовых импульсов, поступающих на вход счетчика 2, последний вырабатывает двоичный код, являющийся адресным для постоянного запоминающего устройства и, i (Л с 00 о ел 00 4 I

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (ll) (5I) 4 H 02 M 1/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3931 955/24-07 (22) 19.07 ° 85 (46) 23,04.87, Бюл. ¹ 15 (71) Коммунарский горно-металлургический институт (72) А.В.Пузаков (53) 621.316 ° 727(088.8) (56) Гольденберг M.Н. Импульсные устройства. — М.: Радио и связь, 1981, с. 197 °

Авторское свидетельство СССР № 1001436, кл. Н 02 M 7/48, 1982. (54) ГЕНЕРАТОР ИНОГОФАЗНОГО КВАЗИСИНУСОИДАЛЬНОГО НАПРЯЖЕНИЯ (57) Изобретение относится к электротехнике и может быть использовано в схемах управления преобразователями частоты. Целью изобретения является упрощение и расширение функциональных возможностей. Под действием тактовых импульсов, поступающих на вход счетчика 2, последний вырабатывает двоичный код, являющийся адресным для постоянного запоминающего устройства

13058

3, в котором записаны коды дискретных выборок синусоидального напряжения и на выходе которого формируется кодо— вая последовательность, преобразуемая в ступенчатое квазисинусоидапьное напряжение. Двоичный код с выходов сч;=ò-. -— чика 2 поступает также на первый порт входов сумматоров 6 каналов формирования выходного напряжения каждой

14 последующей фазы, на второй порт входов которых поступает код с выходов задатчиков кода ". Б задатчиках кода .5 сформированы коды заданного фазово— го сдвига выходных напряжений других фаз. Б результате происходит формирование выхсдных напряжений других каналов с фазовым сдвигом относительно первого канала,. 3 ил.

Изобретение относится к преобразовательной технике и может быть испопьзовано в схемах управления преоб разователем частоты.

Целью изобретения является упрощение генератора и расширение функциональных возможностей.

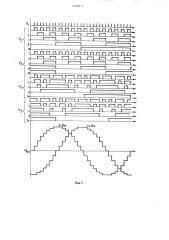

На фиг ° 1 представлена функциональная схема генератора; на фиг.2 временные диаграммы, поясняющие ра- 1О боту схемы; на фиг, 3 — таблица программирования постоянных запомина.ощих устройств °

Генератор содержит поспедо"атепьи но соединенные управляемый генератор

1 тактовых импульсов и счетчика 2, по числу каналов формирования фаз выходных напряжений постоянные запоминающие устройства 3 и цифроаналоговые преооразоватепи 4, входы которых сое- () динены с выходами постоянных запоминающих устройств 3. Канал формирования выходного напряжения каждой последующей фазы дополнительно снабжен ,7 задатчиком 5 кода и сумматором б,причем входы первого порта сумматора соединены с выходами счетчика и входами постоянного запоминающего устройства первого канала формирования выходно— го напряжения, а входы второго порта — с выходами задатчика кода, выходы — с входами постоянных запоминающих устройств формирования выходных напряжений последующих каналов.

Генератор работает следующим образом.

Под действием управляющего напряжения U генератор 1 тактовых импульсов вырабатывает импульсную последовательность с частотой, определяемой уровнем этого напряжения (кривая

2 фиг. 2) . Под действием тактовых им— пульсов, поступающих на вход счетчика 2, последний вырабатывает на своих выходах нарастающий двоичньй код (семейство кривых U>, фиг. 2), являющийся адресным дпя постоянного запоминающего устройс-.ва 3, в котором записаны коды дискретных выборок синусоидапьного напряжения (фиг. 3). Образующаяся на выходах постоянного запоминающего устройства кодовая поспедоватепьнссть (семейство кривых д фиг. 2) поступает на входы цифроаналогового преобразователя 4, в результате на выходе последнего формируется ступенчатое квазисинусоидальное напряжение (кригая П, „,,фиг. 2).

Двоичный код с выходов счетчика 2 поступает также на первый порт входов сумматоров 6 канапов формирования выходного напряжения каждой последую— щей фазы, на второи порт входов которых поступает код с выходов задатчиков 5 кода. При этом в задатчиках кода сформированы коды заданного фазоного сдвига выходнь х напряжений других фаз. Б результате суммирования на выходах сумматоров 6 образуются адресные коды с заданным фазовым сдвигом

Например, в канале формирования вьгходного напряжения второй фазы на выходе сумматора 6 образуется кодовая последовательность (семейство кривых фи-.. ), которая поступает на входы пос,о:нного запоминающего устройства 3 своего канала. На выходе постся;-:ного запоминаюшего устройства

3 данно: о ка.нала образуется кодовая п >спепонате::ьность (семейстьо кривых

3 13058 фиг. 2), которая поступает на входы цифроаналогового преобразователя 4, на выходе которого образуется ступенчатое квазисинусоидальное напряжение с заданным сдвигом по фазе (кривая Б, фиг. 2).

Аналогичным образом происходит формирование выходных напряжений других каналов с заданным фазовым сдви- 10 гом в каждом канале относительно выходного напряжения первого канала.

При необходимости фазовый сдвиг изменяется путем перестройки кода в 15 задатчиках 5 кода без изменения таблицы истинности постоянных запоминающих устройств 3.

Таким образом, изобретение позво- 20 ляет расширить функциональные возможности генератора за счет обеспечения изменения фазового сдвига путем перестройки кода в задатчиках кода, упростив при этом построение генерато25 ра в связи с использованием постоянных запоминающих устройств с идентичной таблицей истинности.

14 4

Формул а и з о б р е т е н ия

Генератор многофазного квазисинусоидального напряжения, содержащий последовательно соединенные управляемый генератор тактовых импульсов и счетчик, о числу каналов формирования фаз выходных напряжений постоянные запоминающие устройства и цифроаналоговые преобразователи, входы которых соединены с выходами постоянных запоминающих устройств с кодами дискретных выборок синусоидального напряжения, отличающийся тем, что, с целью упрощения и расширения функциональных возможностей, он снабжен в канале формирования выходного напряжения каждой последующей фазы задатчиком кода и сумматором, причем входы первого порта сумматора соединены с выходами счетчика и входами постоянного запоминающего устройства первого канала формирования выходного напряжения, а входы второго порта — с выходами задатчика кода, выходы — с входами постоянных запоминающих устройств формирования выходных напряжений последующих каналов.

13 05814.

2 д

f

3 Ч

Ю

1б

2

Ю

Зн

2

8

Зн.

1305814

Адрес lD&

/ЪF F Fi Б

8 ixo0 nap

Ав А А А, Зн

Фиг.5 Составитель С.Станкевич

Техред А.Кравчук Корректор А.Зимокосов

Редактор О.Юрковецкая

Тираж 661

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 1463/53

Подписное ул.Проектная, 4

Производственно-полиграфическое предприятие, r.Óæãoðîä, 0

1 г

Ф

5 б

7 д

О

12

73

И

1б

77

f8

79

ZI

22

23

2б

27

2о

29

000 00

000О1

000 f0

0001 1

00 1 00

00f 01

00f 1f

0f 0а0

010 01

0f0 f0

0f 017

0fl 00

0f 10f

Of f10

0f f f1

f0000

f 0001

700f 0

f0011

I 0100

1 0107

10f f0

101f 1

f 1000

10 01

1f 010

7 1011

1 1101

7 1110

1 1111

00001

00f f1

0f f01

10 011

f 0111

1101 f

f1101

jff11

111f1

111f 1

f f107

1 1

107 17

1007 7

01 107

001 11

0000 7

00f 10

011 00

7 0010

701 10

110f0

71f00

11 110

7f 170

17 070

1011 0

1 0010

001 f 0