Цифровой синтезатор частот

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обесйечивает уменьшение уровня паразитных спектральных составляющих в выходном сигнале. Цифровой синтезатор содержит регистры 1,5 кода частоты, генератор импульсов 2, накапливающий сумматор (НС) 3, блок вычитания 4 кодов, триггер 6, компараторы 7, 11, 12, 13 кодов, коммутатор 8, сумматоры 9, 14, 15, 16 кодов, дешифратор 10, ЦАП 17, фильтр 18 нижних частот. В регистр 1 записан код числа п, а в регистр 5 - код числа N, определяющий емкость НС 3. В НС 3 происходит суммирование кода числа п с кодом числа, полученным в предыдущем такте работы. Блок вычитания 4 определяет разность между текущим значением кода в НС 3 и кодом регистра 5. Компаратор 7 формирует сигнал записи кода блока вычитания 4 в НС 3 в том случае, если текущее значение кода НС 3 превысит значение кода N. Последовательность кодов на выходе НС 3 является последовательностью кодов фазы. Интервал изменения кодов НС 3, равный N, разбивается на четыре подынтервала. С помощью компараторов 11-13 определяется подынтервал, в котором находится текущее значение кода НС 3. Дешифратор 10 формирует управляющие сигналы на сумматор 9 в зависимости от того, в каком подынтервале находится текущее значение кода НС 3. В сумматоре 14 происходит сложение аппроксимирующей функции (с НС 3) и корректирующей функции (с сумматора 9). 1 ил. I (Л р1 эо SD :о

СОЮЗ СОВЕТСКИХ

СОЩМЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 ав а> (5D 4 H 03 В 19 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4010690/24-09 (22) 09.12.85 (46) 23.04.87. Бюл. Ф 15 (72) В.И. Гомозов, Н.П. Кандырин, Ю.M. Романов и С.А. Соколов (53) 621.373.42 (088.8) (56) Рабинер Л., Гоулд Б. Теория и применение цифровой обработки сигналов. — М.: Мир, 1978, с. 622. (54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ (57) Изобретение относится к радиотехнике и обеспечивает уменьшение уровня паразитных спектральных составляющих в выходном сигнале. Цифровой синтезатор содержит регистры 1,5 кода частоты, генератор импульсов 2, накапливающий сумматор (НС) 3, блок вычитания 4 кодов, триггер 6, компараторы 7, 11, 12, 13 кодов, коммутатор 8, сумматоры 9, 14, 15, 16 кодов, дешифратор 10, ЦАП 17, фильтр 18 нижних частот. В регистр 1 записан код числа и а в регистр 5 — код числа N определяющий емкость НС 3 ° В НС 3 происходит суммирование кода числа и с кодом числа, полученным в предыдущем такте работы. Блок вычитания 4 определяет разность между текущим значением кода в НС 3 и кодом регистра 5. Компаратор 7 формирует сигнал записи кода блока вычитания 4 в НС 3 в том случае, если текущее значение кода НС 3 превысит значение кода N.

Последовательность кодов на выходе

НС 3 является последовательностью кодов фазы. Интервал изменения кодов

НС 3, равный N, разбивается на четыре подынтервала. С помощью компараторов 11-13 определяется подынтервал, в котором находится текущее значение кода НС 3. Дешифратор 10 формирует управляющие сигналы на сумматор 9 в зависимости от того, в каком подынтервале находится текущее значение ( кода НС 3. В сумматоре 14 происходит сложение аппроксимирующей функции (с НС 3) и корректирующей функции (с сумматора 9). 1 ил.

1305823

Изобретение относится к радиотехнике и может быть использовано в радиопередающих и радиоприемных устройствах.

Целью изобретения является уменьшение уровня паразитных спектральных составляющих в выходном сигнале.

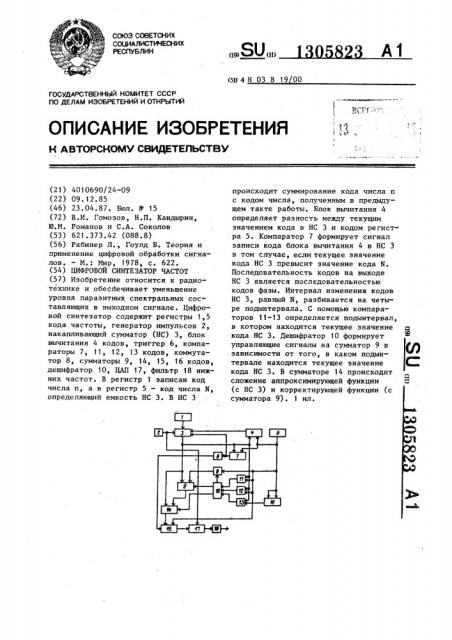

На чертеже представлена электрическая структурная схема цифрового синтезатора частот.

Цифровой синтезатор частот содержит первый регистр 1 кода частоты, генератор 2 импульсов, накапливающий сумматор (НС) 3, блок 4 вычитания кодов, второй регистр 5 кода частоты, триггер 6, первый компаратор 7 кодов, коммутатор 8, первый сумматор

9 кодов, дешифратор 10, второй компаратор 11 кодов, третий компаратор

12 кодов, четвертый компаратор 13 кодов, второй сумматор 14 кодов, третий сумматор 15 кодов, четвертый сумматор t6 кодов, цифроаналоговый преобразователь (ЦАП) 17 и фильтр 18 нижних частот.

Синтезатор работает следующим образом.

В исходном состоянии в первый регистр 1 записан код числа и а во второй регистр 5 — код числа N, определяющий емкость НС 3. В каждом такте работы в НС 3 под действием синхронизирующего импульса с выхода генератора 2 импульсов происходит суммирование кода числа и с кодом числа, полученным в предыдущем такте работы. В НС 3 происходит формирование последовательности кодов Кц 1

= и ° р (р = 1, 2, 3, .. - номер такта работы цифрового синтезатора частот), Одновременно в каждом такте работы в блоке вычитания происходит вычисление разности между текущим значением кода в HC 3 (кодом К ц, ) ) и значением кода во втором регистре. 5 K з )

K цс(р)

В первом компараторе 7 происходит сравнение текущего кода НС 3 и кода второго регистра 5, и на выходе первого компаратора 7 формируется сигнал записи в том случае, если текущее значение кода Кис р1 превысит значение кода N. Под действием этого сигнала происходит переключение триггера б и осуществляется запись выходного кода блока 4 вычитания в НС 3.

В результате этого дальнейшее формирование последовательности кодов

K „,е 1 в НС 3 осуществляется со значенйем dK = К < ), Последовательность кодов на выходе НС 3 можно рассматривать как последовательность кодов фазы на интервале q E (0.„.(е). Преобразование указанных кодов в коды амплитуды выходного колебания осуществляется в остальных элементах цифрового синтезатора частот.

Заданная функция преобразования представляется в виде суммы где FjK« )1t — аппроксимирующая функция

S — число подынтервалов разбиения аргумента;

F Кц, 1 — корректирующая к » Нс р1 функция; ((K „, — переключательная функция.

В качестве аппроксимирующей функЗО ции Р Кц (Д используется прямое или инверсное значение функции К „с(j pà корректирующие функции формируются операциями сдвига и суммирования.

Интервал изменения кодов KHc(p) р равный N, разбивается на четыре

35 подынтервала и с помощью второго, третьего и четвертого компараторов

11-13 происходит определение подынтервала, в котором находится текущее значение кода Кцс(j НС 3. Для этих целей на один из входов компараторов

11-13 подается текущее значение

Кц е 1,а на другие входы подаются коды, определяющие границы выделенных подынтервалов. При этом к второй группе входов второго компаратора 11 подключены выходы второго регистра

5 со сдвигом на один разряд в сторону младших разрядов, что эквивалентно подаче кода N/2. К второй группе

5О входов третьего компаратора 12 подключены выходы второго регистра 5 со сдвигом на два разряда в сторону мпадших разрядов, что эквивалентно подаче кода N/4. На вторую группу

55 входов четвертого компаратора 13 с выходов четвертого сумматора 16 подается код 3 N$4. Этот код формируется в четвертом сумматоре 16 путем

3 13058 сложения кодов N/2 и N/4 либо путем вычитания кода N/4 из кода N. Указанные входные коды четвертого сумматора 16 формируются путем сдвига разрядных шин. В дешифраторе 10 происходит дешифрация выходных сигналов второго, третьего и четвертого компараторов 11-13 и формируются различные управляющие сигналы в зависимости от того, в каком подынтервале 10 находится текущее значение кода, нс(р}

1,5 К чс(р) N/4

Сформированные на выходе третьего сумматора 15 коды амплитуды преобразуются в ЦАП 17, а в фильтре 18 выделяется первая гармоника выходного сигнала.

В предложенном цифровом синтезаторе частот существенно уменьшается уровень паразитных спектральных составляющих в выходном си "нале, Это обусловлено устранением ошибки преобразования кодов при инверсии выходных кодов НС 3, а также более точным формированием выходной гармонической функции.

N нс(р) 4 нс(р) = 1,5 К„,(,) — N/4.

Сложение аппроксимирующей и корректирующей функций происходит во втором сумматоре 14, а формирование корректирующих функций — в первом сумматоре 9.

Если текущее значение кода К„с(р) находится в первом подынтервале, т.е. 20

0 К„,() 6 И/4, на выходах дешифратора 10 формируются управляющие сигналы, под действием которых первый сумматор 9 включается в режим транслирования входного кода, т.е. на его выходе формируется код К„с(р>.

Выходы первого сумматора 9 подключены к входам второго сумматора 14 со сдвигом на один разряд в сторону младших разрядов, что эквивалентно ЗО уменьшению в два раза численного значения входного кода. Под действием сигнала с выхода дешифратора 10 во втором сумматоре 14 осуществляется операция вычитания из кода К„ 35

К кода

Если текущее значение кода К„с(р) находится во втором подынтервале, т.е. N/4 К„ () И/2, то на комму- 40 татор 8 подается сигнал, под воздействием которого выходы второго регистра 5 подключаются к входам первого сумматора 9 со сдвигом на один разряд в сторону младших разрядов. 45

Это эквивалентно подаче кода И/2.В первом сумматоре 9 из кода И/2 вычитается текущее значение кода К„ нс р)> т.е. К,() = N/2 — К„(), а во втором сумматоре 14 из кода К„() вы- 50 читается уменьшенное в два раза значение выходного кода первого сумматора 9, т.е.

23 4

Если текущее значение кода К нс(р) находится в третьем поцынтервале, т.е. N/2 6 K„ (p) « 3 N/4, то в первом сумматоре 9 из кода К (; вычинс (р) тается код N/2, который поступает с выхода коммутатора 8.

Выходной код К,, ) уменьшенный

У () > в два раза во втором сумматоре 14, складывается с кодом К () т.е. Форнс(р) > мируется код

1 N) К,(,) нс(р) 2 И нс(р) 2) Если текущее значение кода находится в четвертом .1одынтервале, т.е.

3 N/4 «Kxc(p) «N то на вход первого сумматора 9 через коммутатор 8 поступает без смещения код числа N из которого вычитается код К„ ().Уменьшенный в два раза выходной код первого сумматора 9 складывается во втором сумматоре 14 с кодом К c(p) т. е, K <(p) 1/2 tN + Kec(p) j ..

Сформированные во втором сумматоре 14 коды подаются на вхоц третьего сумматора 15, управление режимом работы которого осуществляется триггером 6. В первом полуперисде выходного колебания трет л сумматор 15 работает в режиме транслирования входного сигнала, а во втором полупериоде в третьем сумматоре 15 из кода И вычитается выходной код второго сумматора 14. Таким образом, при формировании второго полупериода выходного колебания осуществляется инверсия кодов по основанию N и тем самым устраняется ошибка преобразования кодов.

1305823

Составитель Ю, Ковалев

Редактор О. Юрковецкая Техред А.Кравчук Корректор A.Çèìîêoñoâ

Заказ 1463/53

Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

Формула изобретения

Цифровой синтезатор частот, содержащий первый регистр кода частоты, последовательно соединенные второй регистр кода частоты, блок вычитания кодов, накапливающий сумматор и первый компаратор кодов, последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, а также генератор импульсов, выход fQ которого соединен с входом синхронизации накапливающего сумматора,второй вход первого компаратора кодов подключен к выходу второго регистра кода частоты, второй кодовый вход, установочный вход и выход накапливающего сумматора подключены соответственно к выходу первого регистра кода частоты, выходу первого компаратора кодов и второму входу блока вычитания кодов, отличающийся тем, что, с целью уменьшения уровня паразитных спектральных составляющих в выходном сигнале, между выходом второго регистра кода частоты и вхо- 25 дом цифроаналогового преобразователя введены последовательно соединенные второй компаратор кодов, дешифратор, коммутатор, первый сумматор кодов, второй сумматор кодов и третий сум- 30 матор кодов, а также введены триггер, третий компаратор кодов и последоватепьно соединенные четвертый сумматор кодов и четвертый компаратор кодов, выход которого соединен с вторым входом дешифратора, третий вход, второй и третий выходы которого подключены соответственно к выходу третьего компаратора кодов, управляющему входу первого сумматора кодов и управляющему входу второго сумматора кодов„ второй вход которого объединен с вторым входом первого сумматора кодов, вторым входом второго компаратора кодов, первым входом третьего компаратора кодов и вторым входом четвертого компаратора кодов и подключен к выходу накапливающего сумматора, второй вход третьего компаратора кодов объединен с Кодовым входом коммутатора, вторым входом третьего сумматора кодов, первым и вторым входами четвертого сумматора кодов и подключен к выходу второго регистра кода частоты, вход и выход триггера. подключены соответственно к выходу первого компаратора кодов и управляющему входу третьего сумматора кодов, а выход генератора импульсов соединен с входом синхронизации цифроаналогового пре- . образователя.