Устройство для измерения характеристик синусоидального сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой электроизмерительной технике, а именно к измерению амплитуды, фазы и частоты синусоидальных сигналов. Цель изобретения - расширение функциональных возможностей, повышение точности и быстродействия устройства. Устройство содержит блок 5 управления , аналого-цифровой преобразователь 6, элемент ИЛИ 7, оперативное запоминающее устройство 9, вычислитель 10, блок 11 регистрации. В устройство введены генератор 1 тактов, делитель 2 частоты, элемент И 3 и 4, а блок 5 управления выполнен на элементах И 12 и 13 и триггерах 14 и 15. Это позволяет уменьпить погрешность измерения по сравнению с известным от единиц до десятков процентов. Искпючение фазовращателя позволяет расширить частотный диапазон измерений в сторону низких и инфранизких частот. Отсутствие фазосдвигающего блока, переход, процессы в котором занимают 8-10 периодов входного сигнала, а так-а же независимость времени измерения, которое может быть выбрано меньше одного периода, от частоты входного сигнала, повышает быстродействие устройства . 2 з.п. ф-лы, 2 ил. & (Л utt оо о со О5 О5

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19> (11) А1 (51)4 G 01 R 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCH0MV.ÑÂÈÄETEËÜÑÒÂÓ (21) 3998290/24-21 (22) 30.12.85 (46) 30.04.87. Бюп. 11" 16 (72) М.Я.Минц, В.Н.Чинков, Ю.А.Немшилов и И .А.Карпов (53) 621.3 17(088;8) (56) Патент CIllA N- 4523289, кл. G 01 R 23/02, 1979.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Э (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАК.ТЕРИСТИК СИНУСОИДАЛЬНОГО СИГНАЛА (57) Изобретение относится к цифровой электроизмерительной технике, а именно к измерению амплитуды, фазы и частоты синусоидальных сигналов.

Цель изобретения — расширение функциональных возможностей, повышение точности и быстродействия устройства.

Устройство содержит блок 5 управления, аналого-цифровой преобразователь 6, элемент ИЛИ 7, оперативное запоминающее устройство 9, вычислитель 10, блок 11 регистрации. В устройство введены генератор 1 тактов, делитель 2 частоты, элемент И 3 и 4, а блок 5 управления выполнен на элементах И 12 и 13 и триггерах 14 и 15.

Это позволяет уменьшить погрешность измерения по сравнению с известным от единиц до десятков процентов. Исключение фазовращатепя позволяет расширить частотный диапазон измерений в сторону низких и инфранизких частот.

Отсутствие фазосдвигающего блока, переход, процессы в котором занимают

8-10 периодов входного сигнала, а также независимость времени измерения, которое может быть выбрано меньше одного периода, от частоты входного сигнала, повьппает быстродействие устройства. 2 з.п. ф-лы, 2 ил.

1 130736

Изобретение относится к цифровой электроизмерительной технике, а именно к измерению амплитуды, фазы и частоты синусоидальных сигналов.

Цель изобретения — расширение 5 функциональных возможностей за счет измерения частоты и фазы синусоидального сигнала, повышение точности и быстродействия измерения, расширение частотного диапазона. fO

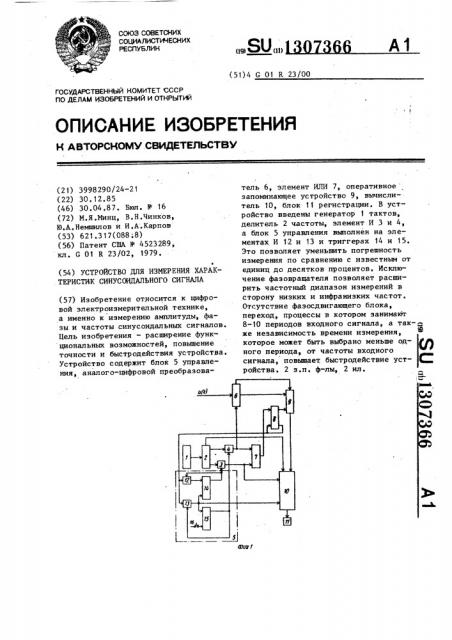

На фиг. 1 изображена структурная схема предлагаемого устройства, на фиг. 2 — функциональная схема вычислителя.

Устройство содержит генератор 1 тактов, делитель 2 частоты, элементы

И 3 и 4, блок 5 управления,. аналогоцифровой преобразователь (АЦП) 6, элемент ИЛИ 7, счетчик 8 тактов, оперативное запоминающее устройство (ОЗУ)20 ,9, вычислитель 10 и блок 11 регистрации.

Выход генератора 1 тактов подключен к делителю 2 частоты, первый, второй и третий выходы которого сое- 25 . динены соответственно с первыми входами элементов И 4 и 3 и третьим входом вычислителя 10. Вторые входы элементов И 4 и 3 подключены к второму и третьему выходам блока 5 уп- 3Q равления. Выход элемента И 3 соединен с точкой, объединяющей один вход элемента ИЛИ 7 и второй вход вычислителя 10, первый вход которого .. подключен к первому выходу блока 5 управления. Выход элемента И 3 соединен с точкой, объединяющей один вход элемента ИЛИ 7 и второй вход вычислителя 10, первый вход которого подключен к первому выходу блока 5 4р управления. Информационный и управляющий записью входы ОЗУ 9 соединены соответственно с информационным выходом и выходом "Конец преобразования" АЦП 6, а выход ОЗУ 9 подклю- g5 чен к четвертому информационному входу вычислителя 10, подключенного к

- блоку 11 регистрации.

Блок 5 управления выполнен на элементах И 12 и 13, триггерах 14 и 5О !

5 и кнопке 16 "Пуск".

Вход блока 5 управления подключен к объединенным первым входам .элементов И 12 и 13, вторые входы которых соединены с единичными выходами TpHF 55 геров 14 и 15, которые являются со- . ответственно вторым и третьим выходами блока 5 управления. Выход элемента И 12 подключен х нулевому входу

6 2 триггера 14, а выход элемента И 13 к точке, объединяющей единичный вход триггера 14, нулевой вход триггера

15 и первый выход блока 5 управления.

Кнопка 16 "Пуск" соединена с единичным входом триггера 15.

В состав вычислителя 10 входят дешифратор (@III) 17, распределитель

18 тактовых импульсов (РТИ), входной буферный регистр (входной БР) 19, схема 20 ускоренного переноса (СУП), блок 21 микропрограммного управления (БМУ), постоянное запоминающее устройство 22 микрокоманд (ПЗУМ), блок

23 арифметико-логических устройств (БАЛУ), оперативное запоминающее устройство (ОЗУ) 24, постоянное запоминающее устройство 25 программы вычислений (ПЗУП), БМУ 26, регистр 27 и выходной буферный .регистр (выходной

БР) 28.

Третий, второй и четвертый входы вычислителя 10 подключены соответственно ко второму входу РТИ 18, первому и второму входам входного БР 19, а первый вход - к точке, объединяющей первые входы БМУ 21 и РТИ 18.

Первый и второй выходы РТИ 18 соединены соответственно со вторым входом

БМУ 21 и первым входом (с, ОС) БМУ

26, третий и четвертый выходы — соответственно с первым и вторым входами (с) БАЛУ 23, а третий и четвертый входы подключены соответственно к третьему выходу дешифратора 17 и второму выходу ПЗУМ 22. Первый и второй выходи дешифратора 17 соединены соответственно со вторым входом выходного БР 28 и третьим входом входного БР 19, а первый вход - с первым выходом ПЗУП 26. Третий выход ПЗУП

25 подключен к четвертому входу (ЗМ, К,-К } БМУ 26, à его второй выход и вход соединены соответственно с третьим входом (УА - A ) и выходом (МА -МА ) БМУ 21. Четвертый вход (Ф)

БМУ 21 подключен к точке, объединяющей четвертый выход (С, СПО) БАЛУ

23 и третий вход (Ф) БМУ 26. Второй выход (Фв) БМУ 26 соединен с седьмым входом (С,, Cn„) БАЛУ 23, а первый выход (МА -МА ) и второй вход (УФ УФ, УАь-УА ) — соответственно с входом и первым выходом ПЗУМ 22, у которого третий выход подключен к первому входу ОЗУ 24, а четвертый выход через регистр 27 соединен с шестым входом (ВАю ВДэ Ко К э Гь Fo) БАПУ 23 °

3 1307366

Третий вход (В, В„) БАЛУ 23 подключен к выходу входного БР 19, первый выход (Х, У) и четвертый вход (С -С„) соответственно подключены ко входу и выходу СУП 20, пятый вход (M()-Êп) и второй выход (Ao-A„) — к выходу и второму входу ОЗУ 24, а третий выход — к точке, объединяющей третий и первый .входы соответственно ОЗУ 24 и выходного БР 28. Выход выходного 10 ет

БР 28 является выходом вычислителя 10.

Сущность предлагаемого изобретения состоит в следующем.

Пусть сигнал, например напряжение U(t) частоту которого необходи- 15 мо измерить, представляет сумму гармонического сигнала

sin 2(оТ

+ — — — ---); (8)

24) T

1 — — (1

) (10)

2(в)Т

2 (у11 — Bvs);

1 (aU -aU ), 1 (12) где

1 яin2„T

h=()(g- = (1 — — — — -) (13)

4 lO 2Т2

По csin(w()t и шума (помехи) n(t) Первый член в выражении (14) от частоты не зависит.

Обозначим

Таким образом, min E = шах Г (1 т.е. оценка частоты получается из условия

max Г ы

После того, как частота найдена, могут быть определены оценки В и С по формулам (11) и (12), а по ним— амплитуда и фаза сигнала по формулам

U =ГВ + Ci (16) Ч= arctg

В

С (17)

Однако такой алгоритм достаточно сложен для технической реализации.

Поэтому рассмотрим возможные упрощения. С этой целью приведем .квадратичную Форму Г((,)) переменных U и U5 к диагональному виду. В.соответствии с известными методами приведения квадратичной формы к главным осям, функционал Г запишется так:

ИВ+ ВС =0

РВ+ус = V, 50 (6) где

55 (7) Г= д (Л,f + f ) = „ f + Е, 1

U(t) = Бщяш(шоС+Ч)+п() (2) где U,(,)о,(— соответственно амплиту-25 да, круговая частота и начальная фаза измеряемого напряжения.

Представим выражение (2) в следующем виде 30

U(t) = Восояиу+СояЫ(у+п(), (3) где Во=ц„,яж

Со=11о,соя(() — квадратурные составляющие амплитуды сиг-35 нала.

Тогда среднеквадратическое отклонение на интервале (О,Т) равно

40 с= — — ) PU(t)-Bcoswt-Csinwt) dt; (4) т

BB: j (U(t)-Bcosu>t-Csinwt)cosult=0; о (5)

)U(t) -Bcos w t-Csin(()t)sin(Bent=0 ас ) о

Систему уравнений (5) после несложных преобразований запишем в виде т

U(t)cos(B)tgt; о т

ВВ = — — ) U(t)sinntgt, о

4 Т(в) (1 — соя2(()Т) (9) 1

Решение системы уравнений (6) даПосле преобразований получим: т

1 1 1

U (B)t — — -(1)2+ив-26(1 U ) (14)

Т д о о s о 5 о

Г((и) = (yves+(Ю2 280,цз ) (15)

1307366

s 1пыС

+ — — — -) 4) t

s inst — — — — -) ldt г связаны с с " Ц5 преобразованием

1 где Л = — -(1

1

Д вЂ” (1

2 при этом f u ортогональным

Uc = Ъ„1f1 + Ъ гf2, Us — Ь21f g + Ьгг f2, 10

15 и = Ь1„Uc + b2 US, Гг = Ь12 Uc + Ъ220, Отсюда п

f

1 Т

2 Т то — Пг + 1/а

1 1 с д (23) состояние, во-вторых, через элемент

50 И 13 подается на нулевой вход триггера 15 и единичный вход триггера 14, переключая указанные триггеры соответственно в нулевое и единичные состояния, и, в-третьих, поступает на

55 третий вход вычислителя 10. Потенциалом триггера 15 элементы И 4 и 13 закрываются, а потенциалом триггера

14 элементы И 3 и 12 открываются.

Импульсом, поступившим по третьему

1. Коэффициенты b«b2„, Ъ12 и Ь2г находятся из уравнений (). — 3„)Ъ11 — ЯЬ21 = 0;

+ Ьг

21 (у — Лг )Ъ 12- ВЬгг= О 1

b12+ b22 1. олучим т

U(t) sI-n (-2- -t) 4t;(19)

Т о т

Т

U () совы(— — -t) с1 t . (20)

2 о

Если сдвинуть начало отсчета в сеТ редину интервала (О,Т), т, е. Й = -2- +

+ t и обозначить U(t + 2 ) = 6(t), 1 т/г

f = — — -(U(t) sinvtQt ь-Us (21)

1 т д ф т/г "гU (t) cosztdt = U . (22) т с °

-Т(2

Подставляя соотношения (22) и (23) в выражение (19), получим

Формулы (22) и (23) могут быть реализованы как в аналоговой. так и в цифровой форме. Однако в цифровой форме их реализация значительно более проста и по своей сути ближе к прототипу. Переход к дискретной форме при числе отсчетов мгновенных значений m осуществляется заменой интеграла суммой в формулах (22) и (23), которые записываются в следующем виде:

6

m/Z

Б = — —,> U (tg) s inetg; 1 =-m/2

m/2

Uc, = — —, U(tg) cos vtg, (24) =-m/2

Т где tg = ° q.

Формулы (8), (9), (10), (16), (17), (23) и (24) положены в основу работы предлагаемого устройства.

Устройство работает следующим образом.

В исходном состоянии элементы И

3, 4, 12 и 13 закрыты потенциалами триггеров 14 и 15, счетчик 8 тактов обнулен, АЦП 6 находится в ждущем режиме.

При нажатии кнопки 16 "Пуск" в блоке 5 управления триггер 15 устанавливается в единичное состояние, открывая элементы И 4 и 13. Через элемент

И 4 тактовые импульсы в моменты времени tg с первого выхода делителя 2 частоты поступают на вход запуска

АЦП 6 и через элемент ИЛИ 7 на счетный вход счетчика 8 тактов. Каждым из этих импульсов осуществляется, во-первых, запуск АЦП 6 и, во-вторых, измерение показаний счетчика 8 так- тов на единицу. Тем самым на информационном выходе АЦП 6 образуются коды мгновенных значений напряжения

U(tg), подаваемые на информационный вход ОЗУ 9, а счетчиком 8 тактов осуществляется последовательная смена адреса ячейки памяти для записи кодов

U(tg) в ОЗУ 9. Запись кода U(tg) производится по сигналу "Конец преобразования", поступающему с .соответствующего выхода АЦП 6 на вход записи ОЗУ 9. После выполнения п тактов преобразования мгновенных значений U(tg) в коды и записи их в ОЗУ 9 на втором выходе счетчика 8 тактов появляется импульс переполнения (заема), который, во-первых, устанав-. ливает счетчик 8 тактов в исходное

366 8 пающим с элемента И 13 блока 5 управления на первый вход вычислителя.

Этот импульс подается на первые входы РТИ 18 и БМУ 21.

При этом, во-первых, в РТИ 18 тактовые импульсы со второго входа поступают на первый выход, во †втор, в БМУ 21 происходит загрузка начального адреса программы, Работа БМУ 21 и 26 заключается в следующем. С приходом каждого тактового импульса они, в зависимости от состояния управляющих входов (УА „УА ), которое определяется кодом, поступающим на третий вход БМУ 21 со второго выхода ПЗУП 25 и на второй вход БМУ 26 с первого выхода ПЗУМ

22, формируют адрес ячейки памяти и соответственно ПЗУП 25 или ПЗУМ 22, из которой в последующем такте будет считана информация.

Как отмечалось выше, при включении вычислителя 10 тактовые импульсы поступают на БМУ 21. При считывании очередной информации с ПЗУП 25 на первом выходе последнего появляется команда, которая после расшифровки на ДШ 17, вызывает переключение РТИ

18 по его третьему входу и открывает выходные вентили входного БР 19 по его третьему входу. При этом тактовые импульсы со второго входа РТИ

18 поступают на второй выход, а первый выход закрывается. Тем самым управление передается на БМУ 26. С приходом первого тактового импульса на

БМУ 26 в нем происходит загрузка начального адреса микропрограммы, который поступает с третьего выхода

ПЗУП 25. В очередном такте со второго выхода ПЗУМ 22 передается на РТИ

18 управляющее воздействие, по которому тактовые импульсы начинают поступать дополнительно на третий и четвертый выходы РТИ 18. Дальнейшая работа вычислителя 10 на этапе перезаписи кодов мгновенных значений s

ОЗУ 24 состоит из и циклов, где n— число этих кодов.

Рассмотрим один цикл, поскольку все они совершенно идентичны.

Напомним, что с приходом каждого тактового импульса в БМУ 26 формируются адреса опрашиваемых ячеек

ПЗУМ 22. Разрешение выдачи адреса, маски и коды выполняемых операций для БАЛУ 23 считываются с четвертого выхода ПЗУМ 22 и через регистр

27 поступают на соответствующие вхо7 1307 входу вычислителя 10, последний переводится в рабочий режим. Работа вычислителя 10 описана отдельно, здесь же рассмотрим процесс ввода в него исходных данных и управляющих сигналов.

Тактовые импульсы со второго выхода делителя 2 частоты подаются через элемент И 3 на второй вход вычислителя 10 и через элемент ИЛИ 7 на счетный вход счетчика 8 тактов. На 10 первом выходе счетчика 8 тактов формируются последовательно адреса ячеек памяти ОЗУ 9, из которых в том же порядке, как и при записи, выводятся коды мгновенных значений U(tg) и подаются на четвертый (информационный) вход вычислителя 10, íà первый вход которого поступают синхронизирующие тактовые импульсы с третьего выхода делителя 2 частоты. После считывания 20 всех и кодов мгновенных значений

U(tg) и ввода их в вычислитель 10, на втором выходе счетчика 8 тактов появляется импульс переполнения (заема), который через элемент И 12 подается на нулевой вход триггера 14, возвращая его в исходное состояние и закрывая тем самым элементы И 3 и

12.

Вычислитель 10 после этого присту- - © пает к цифровой обработке введенного в него массива данных в следующем порядке: определяет величины U и U по формулам (24) при заданном значении и); 35 вычисляет величины „и, по формулам (18) при том же w; вычисляет функцию Г(ы) по формуле (23) .

Затем значения частоты ы последо- 40 вательно перестраиваются по определенной программе и для каждого из них повторяют указанные операции. Полученные при этом значения Г(ш) поочередно сравниваются между собой и так 45 продолжается до момента получения мак. симума сигнала Г(ы), т.е.Г„„„,,(м „).

Значение и>,, при котором функция

Г(ш) достигает максимума Г,„„„(ыо), представляет результат измерения, 50, т.е. частоту входного напряжения

U(t:), поступающий с вычислителя 10 на блок 11 регистрации.

После этого по формулам (16) и (17) производится определение ампли- 55 туды и фазы синусоидального сигнала.

Перевод вычислителя 10 в рабочий режим осуществляется, как указывалось вышее, тактовым импульсом, посту130736 ды БАЛУ 23. Использование регистра

27 позволяет сократить длительность одного такта с 246 с до 126 нс.

В начале цикла в БАЛУ 23 происходит формирование и запись в соответствующий регистр адреса ячейки ., ОЗУ 24, в которую будет записан искомый код. В первом цикле код ячейки памяти нулевой, а в последующих — на единицу больше предыдущего. Его фор- 10 мирование достигается путем подачи на БАЛУ 23 команд соответственно для первого цикла — CSR а для последующего — ILR. Запись в регистр адреса происходит по команде LNI. Признак

Фв, поступающий на седьмой вход БАЛУ

23 со второго выхода БМУ 26 для команд CSR u ILR равен единице, а для

LMI — нулю. В свою очередь, признак

Фв формируется БМУ 26 в зависимости 20 от состояния управляющих входов УФ

УФЗ, которые связаны по второму входу с первым выходом ПЗУМ 22.

Далее БАЛУ 23 по своему третьему входу принимает информацию от входного БР 19. Это происходит при подаче команды LDI через регистр 27 с четвертого выхода ПЗУМ 22 с равным единице признаком Фв. В следующем такте на четвертом выходе ПЗУМ 22 появляет- -З0 ся разрешение на выдачу адреса и данных соответственно на второй и третий выходы БАЛУ 23, а на третьем выхо-. де ПЗУИ 22 — разрешение на запись поступившей информации в ОЗУ 24. 35

По завершению записи очередного . значения кода мгновенного значения в

ОЗУ 24 БАЛУ 23 совместного с БМУ 26 осуществляют условный переход. Суть

его сводится к следующему: если коли- 40 чество совершенных циклов равно количеству мгновенных значений исследуемого сигнала, то осуществляется завершение этого программного модуля, в противном случае цикл повторяется. 45

Происходит это так. Перед началом выполнения циклов перезаписи в БАЛУ 23 производится генерация числа и — количества мгновенных значений исследуемого сигнала. Так, например, для. 50 п = 32 последовательно выполняются команды CSR и П.К и пять раз ALR.

При этом признак Фв равен для команд

CSR u ILR единице, а для команды

ALR — нулю. Генерация и 32 происхо- 55 дит путем комбинации описанных команд. Код числа и записывается в любой из девяти регистров БАЛУ 23. При выполнении условного перехода из ре6 10 гистра, содержащего код и, вычитается значение адреса ячейки памяти ОЗУ

24, увеличенное на единицу, а регистр, содержаший результат, анализируется на нуль. Это происходит при подаче команд ILR, CIA, SDR, ILR, ALR и TZR, причем признак Фв для второй команды ILR u ALR равен нулю, а в остальных случаях — единице.

Если содержимое анализируемого регистра равно нулю, что соответствует окончанию программного модуля, то на четвертом выходе БАЛУ 23 появляется нуль, а в противном случае - единица. БМУ 26, который до этого выполнял переходы ICC и ICR, по признаку Ф (т.е. по результату анализа) на третьем входе, осуществляет условный переход ICF, а затем, выполнив переходы ICC и ICR, переходит на завершение программного модуля либо возвращается на тот участок микропрограммы, откуда начинается цикл перезаписи информации. При выполнении условного перехода на БАЛУ 23 подается команда ВСА, которая с признаком Фв, равным единице, является пустой операцией.

При завершении программного модуля на втором выходе ПЗУИ 22 появляется команда, по которой РТИ 18 выдачу тактовых импульсов по второму, четвертому и пятому выходам прекращает.

В .то же время первый выход РТИ 18 открывается. Тем самым управление передается на БМУ 21. С этого момента вычислитель 10 приступает к расчету искомых величин.

Предлагаемое устройство уменьшает погрешность измерения (по сравнению с известным) от единиц до десятков процентов, даже при небольших фазовых погрешностях фазового сдвига и заданий значения синуса и косинуса, а также при малых нелинейных искажениях, весьма характерных для практики.

Техническое преимущество предлагаемого устройства (по сравнению с известным) состоит в неограниченном расширении частотного диапазона измерений в сторону низких и инфранизких частот за счет исключения операции фазового сдвига, а следовательно, и фазовращателя, техническая реализация которых в инфранизкочастотном диапазоне очень и очень сложна.

Предлагаемое устройство (по сравнению с известным) имеет более высокое быстродействие по двум причинам. Во!

1 13073

f5 ответственно вторым и третьим выходапервых, в связи с отсутствием фазосд ви гающег о бл ок а п ер ex îä ные пр оцессы в котором занимают 8-10 периодов входного сигнала. Во — вторых, время измерения Т в предлагаемом устройстве не зависит от частоты входного сигнала и может быть выбрано меньше одного периода. В прототипе это время составляет 2-3 периода входного сигнала. Таким образом, в прототипе время измерения составляет 10-13 периодов входного сигнала, в предполагаемом устройстве — меньше одного периода. Это особенно важно при измерениях в инфранизком диапазоне частот. бб 12 блока управления, подключенного сВо ими вторым и третьим выходами к вторым входам соответственно первого и второго элементов И.

2. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что блок управления содержит первый и второй элемент И, первый и второй триггер, кнопку "Пуск", причем вход блока управления подключен к объединенным первым входам элементов И, вторые входы которого соединены с единичными выходами первого и второго триггеров соответственно, которые являются соми блока управления, выход первого элемента И подключен к входу установ1, Устройство для измерения харак- ) ления и блок регистрации, причем пер-25 ля, а выход второго элемента И к первым и вторым входам соответственно 5 элемента ИЛИ и аналого-цифрового преобразователя, первый вход которого

Формула изобретения теристик синусоидального сигнала, содержащее аналого-цифровой преобразователь, оперативно запоминающее устройство, вычислитель, блок управвый выход блока управления соединен с первым входом вычислителя, выход которо го подключ ен к входу р егис тратора,о т л и ч à ю щ е е с я тем,что,с целью расширения функциональных возможностей, повышения точности и быстродействия измерения, в него введены генератор тактов, делитель частоты, два элемента И, элемент ИЛИ, счетчик тактов, причем выход генератора тактов подключен к входу делителя частоты, первый и второй выходы которого соединены с первыми входами соответственно второго и первого элемента И, а третий выход — с третьим входом вычислителя, выход первого эле мента И подключен к вторым входам элемента ИЛИ и вычислитеявляется входом устройства, а первый и второй выходы подключены соответственно к первому и второму входам оперативного запоминающего устройства, выход которого соединен с четвертым входом вычислителя, а третий вход оперативного запоминающего устройства соединен с первым выходом счетчика тактов, первый вход которого соединен с выходом элемента ИЛИ, а второй выход счетчика тактов подключен к его второму входу и входу

40 ки.нуля первого триггера, выход второго элемента И вЂ” к входу установки. единицы первого триггера и входу установки нуля второго триггера, кнопка

"Пуск" соединена с входом установки единицы второго триггера, выход второй схемы И является нужным выходом блока управления.

3 ° Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что вычислитель содержит дешифратор, распределитель тактовых импульсов, входной буферный регистр, схему ускоренного переноса, первый и второй блок микропрэграммного управления, первое и второе пос-, тоянное запоминающее устройство, блок арифметически-логических устройств, оперативное запоминающее устройство, регистр, выходной буферный регистр, причем первый вход вычислителя подключен к первым входам первого блока микропрограммного управления и распределителя тактовых импульсов, второй и четвертый входы подключены соответственно к первому и второму входу входного буферного регистра, третий вход вычислителя — к второму входу распределителя тактовых импульсов, первый и второй выходы которого соединены соответственно с вторым входом первого блока микропрограммного управления и первым входом второго блока микропрограммного управления, третий и четвертый выходы — соответственно с первым и вторым входами блока арифметически-логического устройства, а третий и четвертые входы подключены соответственно к третьему выходу дешифратора и второму выходу первого постоянного запоминающего устройства, первый и второй выходы дешифратора соединены соответственно!

ФУРА

Составитель Е.Губанов

Редактор А.Ревин Техред А.Кравчук Корректор А.Обручар

Заказ 1627/44 Тираж 731 Подписное

ЗНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

13 130736 с вторым входом выходного буферного регистра и третьим входом входного буферного регистра, а вход — с первым выходом второго постоянного запоминающего устройства, третий выход которо- 5

ro подключен к четвертому входу второго блока микропрограммного управления, второй выход и вход соединены соответственно с третьим входом и выходом первого блока микропрограммного управления, четвертый вход которого подключен к четвертому выходу блока арифметически-логических устройств и третьему входу второго блока микропрограммного управления, второй выход 15 которого соединен с седьмым входом блока арифметически-логических устройств, а первый выход и второй вход соответственно с входом и первым выходом первого постоянного запоминающего устройства, у которого третий выход подключен к первому входу оперативного запоминающего устройства, а четвертый выход через регистр соединен с шестым входом блока арифметически-логических устройств, третий вход которого подключен к выходу входного буферного регистра, а первый выход и четвертый вход подключены соответственно ко входу и выходу схемы ускоренного переноса, пятый вход и второй выход — к выходу и второму входу оперативного запоминающего устройства, а третий выход — к третьему входу оперативного запоминающего устройства и первому входу выходного буферного регистра, выход которого является выходом вычислителя.