Цифровой измеритель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к технике измерения частот методом дискретного счета. Цель изобретения - повышение быстродействия. Устройство содержит генератор 1 эталонной частоты , формирователь 5 импульсов измеряемой последовательности, элементы И 9, 11, 10, счетный триггер 12,счетчики 13, 14 импульсов. Для достижения поставленной цели в устройство введены N селекторов 3 последовательностей , N-входовый элемент ИЛИ 7, элемент И 4, формирователь 2 сдвинутых последовательностей, триггер 8, образованы новые . Каждый селектор 3 последовательностей состоит из двух элементов И, триггера. В устройстве сокращено время с момента подачи сигналов измеряемой частоты F. до начала процесса счета, т.е. повышено быстродействие. 1 з.п. ф-лы, 3 ил. сл со о со О5 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 С 01 R 23 10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А 9ТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3823809/24-21 (22) 07. 12. 84 (46) 30. 04. 87. Ввл. У (72) В.П. Улитенко, P. В. Коровин, И. И. Ковтун и E. В. Пугач (53) 621. 317 (088.8) (56) Шляндин В;М. Цифровые измерительные устройства. М.: Высшая школа, 1981.

Авторское свидетельство СССР

М 612179, кл. G О1 R 23/10, 1978. (54) ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к технике измерения частот методом дискретного счета. Цель изобретения — ловы= шение быстродействия. Устройство соЛК 1307368 А 1 держит генератор 1 эталонной частоты, формирователь 5 импульсов измеряемой послеДовательности, элементы

И 9, 11, 10, счетный триггер 12,счетчики 13, 14 импульсов. Для достижения поставленной цели в устройство введены N селекторов 3 последовательностей, N-входовый элемент ИЛИ 7, элемент И 4, формирователь 2 сдвинутых последовательностей, триггер 8, образованы новые связи. Каждый селектор 3 последовательностей состоит из двух элементов И, триггера. В устройстве сокращено время с момента подачи сигналов измеряемой частоты .

F. до начала процесса счета, т.е. повышено быстродействие. 1 з.п. ф-лы, 3. ил.

1 13073

Изобретение относится к технике измерения частот методом дискретного счета.

Цель изобретения — повышение быстродействия.

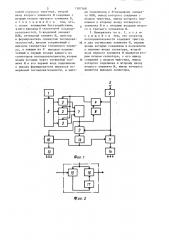

На фиг. 1 изображена функциональная схема цифрового измерителя частоты; на фиг. 2 — селектор последовательностей; на фиг. 3 — временные диаграммы работы цифрового измерителя частоты.

Цифровой измеритель частоты содержит генератор 1 эталонной частоты, формирователь 2 сдвинутых последовательностей, селекторы 3 последовательностей, четвертый элемент И 4, формирователь 5 импульсов измеряемой последовательности, входную шину 6, многовходовый элемент ИЛИ 7, триггер

8, второй элемент И 9, третий элемент 2О

И 10, первый элемент И 11, счетный триггер 12, второй счетчик 13 и первый счетчик 14.

Каждый селектор 3 последовательностей состоит из элементов И 15 и 25

16 и триггера 17.

Цифровой измеритель частоты содержит генератор 1 эталонной частоты,последовательно соединенные формирователь 5 импульсов измеряемой последа- 3g вательности, вход которого соединен с входной шиной 6, первый элемент И

11 и первый счетчик 14 импульсов, последовательно соединенные второй элемент И 9, счетный триггер 12, тре- 5 тий элемент И 10 и второй счетчик 13, причем первый вход второго элемента

И 9 соединен с первым входом первого элемента И 11, второй вход которого соединен с выходом счетного триггера 4р

12, а второй вход второго элемента

И 9 объединен со вторым входом третьего элемента И 10, а также N селекторов 3 последовательностей, N-входовой элемент ИЛИ 7, четвертый элемент 45

И 4, триггер 8 и формирователь 2 сдвинутых последовательностей, входом соединенный с выходом генератора

1 эталонной частоты, а каждым из N выходов подключенный к первым входам каждого из селекторов 3 последовательности, вторые входы которых через четвертый элемент И 4 и его первый вход подключен к выходу формирователя 5 импульсов измеряемой последовательности, а выходы подключены к

N-входовому элементу ИЛИ 7, выход . которого соединен со входом триггера

8, выход которого подключен к второ68 2 му входу четвертого элемента И 4, и со вторыми входами второго 9 и третьего 10 элементов И.

Каждый селектор 3 последовательности содержит триггер 17 и два логических элемента И 15 и 16, первые входы которых соединены и подключены к первому входу селектора 3, второй вход первого логического элемента

И 15 является вторым входом селектора 3, а его выход соединен со входом триггера 17, выход которого подключен ко второму входу второго элемента И 16, выход которого является выходом селектора 3.

Формирователь 2 сдвинутых последовательностей формирует и последовательностей импульсов с периодом

ТЗ причем каждая следующая последовательность сдвинута относительно предыдущей на интервал времени t q = где t — длительность импульсов каждой последовательности, связанная с периодом Т зависимостью и

ХЭ и

Цифровой измеритель частоты работает следующим образом.

Генератор 1 эталонной частоты вырабатывает периодическую последовательность импульсов (фиг. Зв) с частотой Г е = I/T >, которая поступает на формирователь 2 сдвинутых последовательностей, в результате чего формирователь 2 на своих выходах формирует сдвинутые последовательности (фиг. 3 г,д,е,ж), поступающие на селекторы 3 последовательностей и в них на первые входы логических элементов И 15 и 16. Однако на выходы элементов И 15 и 16 эти последовательности не проходят, так как на вторых входах элементов И 15 отсутствуют сигналы с выхода логического элемента И 4, а на вторых входах логических элементов И 16 отсутствуют разрешающие сигналы с выходов триггеров 17.

В исходном состоянии счетчики 13 и 14 установлены в нулевое состояние, триггер 12 находится в нулевом состоянии, при котором на его выходе отсутствует разрешающий сигнал для элементов И 10 и 11, триггер 8 находится в единичном состоянии, при котором логический элемент И 4 открыт для прохождения импульсов измеряемой последовательности и, наконец, триггеры 17 селекторов 3 последовательности находятся в нулевом состоянии, 3 13073 при котором разрешающий потенциал на вторых входах элементов И 16 отсутствует. Цепи установки счетчиков и триггеров в исходное состояние для упрощения на фиг. 1 не показаны.

Сигнал измеряемой частоты F от5 х сутствует.

Работа цифрового измерителя частоты начинается с поступления на входную шину 6 исследуемого сигнала F» (момент д на фиг. 3a). Будучи преобразованным в формирователе 5 в последовательность импульсов (на фиг. Зб), он поступает на входы логических элементов И 4, 9 и 11.Поскольку логический элемент И 4 открыт разрешающим напряжением на выходе триггера 8, то первый же импульс последовательности Г„ с выхода формирователя 5 поступает на входы селекторов 3 последовательности, где проходит на вторые входы логических элементов И 15 и в одном их этих элементов совпадает (фиг. 3e) по времени с соответствующей выходной последова- я5 тельностью формирователя 2. В результате этого совпадения на выходе данного элемента И 15 появляется сигнал, который поступает на единичный вход триггера 17 данного. селектора, триг- ЗО гер 17 меняет свое состояние, в результате чего на его выходе, соединенном с логическим элементом И 16 появляется разрешающий сигнал и элемент И 16 начинает пропускать импульсы соответствующей последовательности с формирователя 2. С выхода селектора 3 последовательности эти импульсы поступают на вход логического элемента ИЛИ 7, с выхода кото- 40 рого поступают на триггер 8 и логические элементы И 9 и 10.

Первый же из прошедших импульсов последовательности с выхода элемента ИЛИ 7 совпадает с избранной последовательностью формирователя 2 и, следовательно, не совпадает с другими последовательностями, в результате чего триггер 8 переводится в противоположное состояние и снима- 5р ет со входа элемента И 4 разрешающее напряжение. Это приводит к тому, что в дальнейшем импульсы последовательности Г„ на входах селекторов

3 последовательностей будут отсутствовать и остальные селекторы выдавать сигналы на свои выходы не будут. Поступление выходного сигнала логического элемента ИЛИ 7 на второй

68 4 вход логического .>лемента И 9 одновременно с существованием на его первом входе сигнала измеряемой последовательности Т„ приводит к появлению на выходе этого элемента И сигнала (фиг.3 з, импульс а), который поступает на счетный вход триггера

12. Триггер 12 меняет свое состояние и на его выходе появляется разрешающее напряжение (фиг. Зк), отпирающее элементы И 10 и 11. Через эти элементы И обе последовательности импульсов поступают на счетные входы счетчиков 13 (фиг. Зм) и 14 (фиг. Зл), причем счетчик 13 считает количество импульсов последовательности Тз, а счетчик 14 — после— довательности Т».

Подсчет продолжается до тех пор,. пока не проиэойдет совпадение во времени импульсов тех же двух последовательностей. При совпадении на выходе элемента И 9 появится сигнал, который вернет в исходное состояние триггер 12, в результате че— го логические элементы И 10 и 11 закроются и поступление импульсов на счетчики 13 и 14 прекратится.

Таким образом, за время нахождения триггера 12 в единичном состоянии на счетчик 13 пройдут И импульсов с периодом Т,а на счетчик 14 пройдут N > импульсов с периодом Т».

Измеряемая частота Р» определяется из выражения

Nq .Т

Таким образом, в цифровом измерителе частоты сокращено время с момента подачи сигналов измеряемой частоты Р» до начала процесса счета,. т.е. повышено быстродействие.

Формула изобретения

1.Цифровой измеритель частоты, содержащий генератор эталонной частоты, последовательно соединенные формирователь импульсов измеряемых последовательностей, вход которого соединен с входной шиной, элемент И и счетчик импульсов, а также последовательно соединенные второй элемент

И, счетный триггер, третий элемент

И и второй счетчик, причем, первый вход второго элемента И соединен с первым входом первого элемента И, второй вход которого соединен с вы1зо з

5 ходом счетного триггера, второй вход второго элемента И соединен с вторым входом третьего элемента И, отличающийся тем, что, с пелью повышения быстродействия, в него введены N селекторов последовательностей, 1 -входовой элемент

ИЛИ, четвертый элемент И, триггер и формирователь сдвинутых последовательностей, входом соединенный с 10 выходом генератора эталонного периода, а каждым из N выходов подключенный к первым входам каждого из селекторов последовательности, вторые входы которых через четвертый эле- 15 мент И и его первый вход подключены к выходу формирователя импульса измеряемой последовательности, а выхо68 6 ды подключены к Б-входовому элементу ИЛИ, выход которого соединен с. входом триггера, выход которого подключен к второму входу четвертого элемента И и с вторыми входами второго и третьего эпементов И.

2. Измеритель по п. 1, о т л ич а ю шийся тем, что селектор последовательности содержит триггер и два логических элемента И, первые входы которых соединены и подключены к первому входу селектора, второй вход первого элемента И является вторым входом селектора, а его выход соединен с входом триггера, выход которого подключен к второму входу второго элемента И, выход которого является выходом селектора.

1307368

Составитель Е.Минкин

Техред А.Кравчук Корректор С.Шекмар

Редактор А.Ревин

Заказ 1627/44 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4