Цифровой фазометр среднего значения

Иллюстрации

Показать всеРеферат

Изобретение относится к области информационно-измерительной техники . Может быть использовано как в аналоговых , так и в цифровых приборах для измерения сдвига фаз. Цель изобретения - повышение точности измерения сдвига фаз. Для достижения поставленной цели в устройство введены логический блок 1, источник 7 образцового напряжения, интеграторы 10, 11, фиксатор 12 уровня, преобразователь 13 напряжения в интервал времени , ключи 14, 15. Устройство также содержит формирователи 2,3, генератор 4, элемент 5 совпадения, счетчик 6, триггер 16, ключи 8.9. В описании изобретения приведены примеры реализации логического блока 1 и блока управления. Устройство обеспечивает синхронную с входной частотой работу интеграторов 10, 11 и преобразователя 13, что позволяет исключить ряд погрешностей. 3 ил. (О (Л W V i I 0U9.f

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (19) (II) (SII 4 С 01 Р. 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, !3

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ

И А BTOPCHOMV СВИДЕТЕЛЬСТВУ (2 1) 390 3420/24-21 (22) 28.05.85 (46) 30.04.87 Бюл. Il" 16 (71) Пензенский политехнический институт (72) N.Þ.Михеев, Б.В.Чувыкин, Л.Н.Бондаренко и И,Р.Добровинский (53) 621.317.7(088.8) (56) Глинченко А.С. и др. Цифровые методы измерения сдвига фаэ. Новосибирск: Наука, 1979.

Шляндин В.M.Цифровые измерительные устройства. М.: Высшая школа, 198 1, с. 194 †!98, с. 176-178,рис.335. (54) ЦИФРОВОЙ ФАЗОМЕТР СРЕДНЕГО ЗНАЧЕНИЯ (57) Изобретение относится к области информационно-измерительной техники. Может быть использовано как в ана. логовых, так и в цифровых приборах для измерения сдвига фаз. Цель изобретения — повышение точности измерения сдвига фаз. Для достижения гоставленной цели в устройство введены логический блок 1, источник 7 образцового напряжения, интеграторы 10

11, фиксатор 12 уровня, преобразователь 13 напряжения в интервал времени, ключи 14, 15. Устройство также содержит формирователи 2,3, генератор 4, элемент 5 совпадения, счетчик 6, триггер !6, ключи 8.9, В описании изобретения приведены примеры реализации логического блока 1 и блока управления. Устройство обеспечивает синхронную с входной частотой работу интеграторов 10, 11 и преобразователя 13, что позволяет исключить ряд погрешностей. 3 ил.

1З07З

Изобретение относится к информационно-измерительной технике и мо\" жет быть использовано как в аналого-. вых, так и в цифровых приборах для измерения сдвига фаз. 5

Цель изобретения — повышение точности измерения сдвига фаз.

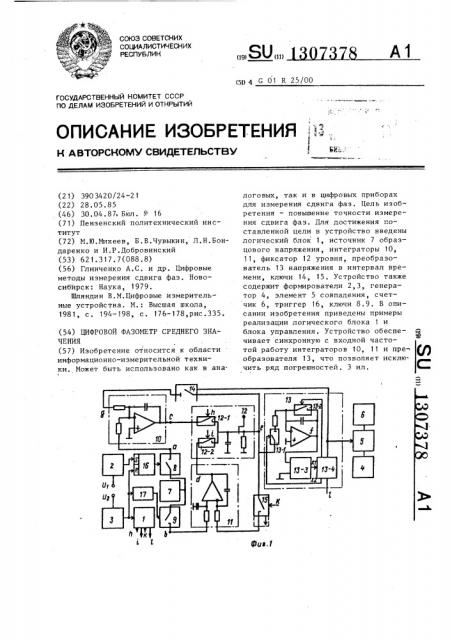

На фиг. 1 изображена структурная схема цифрового фазометра среднего значения1 на фиг.2 - временные диаг- ® раммы его работы.

Цифровой фазометр среднего значения (фиг. 1) содержит логический блок 1, формирователи 2 и 3, генератор 4, элемент 5 совпадения, счетчик 6, источник 7 образцового напряжения, ключи 8 и 9, интеграторы 10 и 11, фиксатор 12 уровня, преобразователь 13 напряжения в интервал времени, ключи 14 и 15 и тирггер 16.

Входы формирователей 2 и 3 являются входами фаэометра. Выход формирователя 3 соединен с первым входом триггера .16 и через логический блок 1 с управляющим входом ключа 9. Выход, формирователя 2 подключен к второму входу триггера 16, выход которого сое динен с управляющим входом ключа 8.

Выход источника 7 образцового напря30 жения через ключи 8 и 9 подключен к первым входам соответствующих ине теграторов 10 и 11, выходы которых соединены с первым и вторым входами фиксатора 12 уровня.

Выход фиксатора 12 уровня подключен ко входу преобразователя 13 напряжения в интервал времени и через ключи 14 и 15 — ко вторым входам интеграторов 10 и 11 соответственно.

Выход преобразователя 13 напряжения

40 в интервал времени соединен с одним из входов элемента 5 совпадения и со входом ключа 14. Второй вход элемента совпадения подключен к выходу генератора 4. Выходы блока 1 подключены к первому и второму управляющим входам фиксатора 12 уровня, к управляющим входам преобразователя 13 и ключа 15.

Цифровой фазометр среднего значения работает следующим образом (фиг.2) .

Делитель 17 частоты формирует сигнал U с периодом h в и раз большим периода входного сигнала. Интегратор 11 в течение интервала времени

h — ы t h интегрирует напряжение U

2 о

78 2 источника 7 образцового напряжения, а в течение интервала времени

h t h + Ь вЂ” . выходное напряжение фиксатора 12 уровня. В момент времени h фиксатор 12 уровня осуществляет запоминание выходного напряжения интегратора 11, Сигнал, управляющий фиксатором 12 уровня и ключами 9 и 8, подключающими входы интегратора 11 к выходам источника 7 образцового напряжения, формируется логическим блоком 1 под действием выходного сигнала формирователя 3.

Для выходного напряжения интегратора 11 в моменты времени

h 3

h -h справедливы следующие вы2 2 ражения:

V (-) =0, h

Ud (h) = Ud (2)+ j У dt;

h 1 а ((ll

U (1) — П,(Ь) „- U,(Ь) d

1 Ь где h — такт преобразования, равный r периодам Т входного сигнала, г,Π— постоянная интегрирования

2 по входам интегратора 11.

При записи выражений для U (t) использован тот факт, что фиксатор 12 в момент времени h запоминает выходное напряжение интегратора 11 и храю 3 нит его до момента времени 2 h, т.е.

U (t)/ g t(— h = U (h) = — U

3 h е 2 d h о

ho

Подставляя = —, преобразуем

2 выражения для U (t) к виду:

UZ(h)=-U=U

h о d

3 и, (-1) =О, 2

Далее процесс работы интегратора 11 периодически повторяется.

Интегратор 10 в течение интервала времени 0 c t c h интегрирует напряжение на выходе ключа 8, подключающего напряжение Б источника 7 опорного напряжения к входу интегратора 10 в течение и интервалов вре1307378

4 асср

U (1 t; о мени t, определяемых фазовым сдви гом (между входными напряжениями

U< и U . Формирование интервалов времени t îñóùåñòâëÿþò формирователи 2 и 3 совместно с триггером 16. (В течение интервала времени задаваемым преобразователем 13, интегратор 10, наряду с напряжением U интегрирует выходное напряжение Uz фиксатора 12 уровня, поступающее на вход интегратора 10 через ключ 14, управляемый выходным сигналом преобразователя 13 напряжения в интервал времени.

Для выходного напряжения интегратора 10 в моменты времени 0;

h., 3, 2 2

h — h справедливы выражения п) ц Й

h о о

h = n T, ho 4со

h.р= о т = тх tgp

U d t „-„ Ц а;

1 о о

U /3/2h)=Uc(h)+ о ho4c0

2 й

Логический блок(фиг.3а) состоит из кварцевого генератора, трех двухвходовых элементов И, двух триггеров

55 с раздельными входами, счетчика HMпульсов, элемента ИЛИ-НЕ и двух формирователей, кажцый из которых содержит три элемента ИЛИ-НЕ и двухвходовый элемент И. ний ц,) 0 цс() U (О)+,- U0,d t;

h 1 о

1 ц,(gy - ц,(z -" - J tl, а о х ц (2h) — U,(h) + .U d о где о = h — постоянная времени .интего рирования по входам интегратора 10.

Выполняя операцию интегрирования и учитывая равенство х ср

h ) Udt= j Ц dt о о получим выражения для ц,(г) в виде: х с / ) "о о

t„

U 01) =n„- цап

1 о

3 и 1 (U(-h) = (Udt

2 2 1,1 о о

U,(2h) =n„- Ц,аt.

1 о

Решая совместно систему уравнеопределим выражение для выходного

f0 интервала времени t, преобразователя 13:

Формирование интервала времени

t осуществляет преобразователь 13, который может быть построен, например, как это показано на фиг.3 по двухтактной схеме. В интервал вре20 мени t преобразуется выходное напряжение фиксатора 12, присутствующее на его выходе в течение интервала вре

h мени — c t h. В качестве опорного

25 напряжения преобразователя 13 напряжения в интервал времени используется также выходное напряжение фиксатора 12, присутствующее на его входе в течение интервала времени

30 3

Ь(t — h. 2

Совокупность генератора 4, элемента 5 совпадения и счетчика 6 представ-. ляет собой преобразователь в цифро35 вой код интервала времени t формируемого преобразователем 13.

При этом выходной код определяется выр аже нием

Синхронная с входной частотой работа интеграторов и преобразователя напряжения в интервал времени позво45 ляет исключить погрешности, присущие прототипу.

Пример реализации логического блока 1 и блока управления устройства, входящего в преобразователь 13, при5О веден на фиг.За и Зв.

1307378

Блок управления (фиг.Зв) содержит триггер с раздельными входами, два двухфазовых элемента И, элемент ИЛИНЕ и два идентичных формирователя .

Входной сигнал блока 1 поступает на формирователь а коротких импульсов, а выходной сигнал формирователя а является выходом i блока.

Выходное напряжение U представлено на фиг.2. Аналогичным образом с вы.10 хода формирователя Ь на выход h логического блока 1 поступает сигнал

U1 (фиг,2). Сигналы U è U> устанавливают триггер логического блока 1 поочередно в нулевое и единичное сос- 15 тояния. Посредством заполнения счетчика блока 1 импульсами кварцевого генератора осуществляется формирование сигнала 1, который представляет собой последовательность импульсов длительностью — (фиг.2). Из сравне4о

2 ния сигналов 1, а также сигнала с выхода нижнего триггера логического блока 1 (фиг.За) формируется сигнал К.

В блоке управления триггер устанавливается выходным сигналом формирователя С в единичное состояние, а выходным сигналом формирователя d —в нулевое состояние. При этом его прямой выход является выходом Х блока управления. Выходной формирователь, собранный на двух элементах И, осуществляет формирование сигнала Х . 35

Работа блока управления иллюстрируется диаграммой состояний, приведенной на фиг.З с.

Формула изобретения

Цифровой фазометр среднего значения, содержащий два формирователя, триггер, первый и второй ключи, генератор, делитель частоты и счетчик, причем входы формирователей являются входами устройства, а их выходы соединены с входами триггера, выход которого подсоединен к управляющему входу.первого ключа, выход генератора через второй ключ соединен с входом счетчика, отличающийся тем, что;-с целью повышения точности измерения сдвига фаз, в него дополнительно введены логический блок ис1

1 точник образцового напряжения, два интегратора, фиксатор уровня, преобраэователь напряжения в интервал времени, третий, четвертый и пятый ключи, причем выход источника образцового напряжения через первый и третий ключи соединен с первыми входами первого и второго интеграторов, выходы. которых подключены к первому и второму входам фиксатора уровня, выход которого соединен с входом преобразо вателя напряжения в интервал времени и через четвертый и пятый ключи— с вторыми входами первого и второго интеграторов, первый выход преобразователя напряжения в интервал времени соединен с управляющими входами второго и четвертого ключей, выход второго формирователя соединен с вхо— дом логического блока и входом делителя частоты, выход которого соединен с управляющим входом третьего ключа, первый, второй, третий и четвертый выходы логического блока соединены с первым и вторым управляющими входами фиксатора уровня и с управляющими входами пятого ключа и преобразователя напряжения в интервал времени.

1307378

Составитель Ю.Макаревич

Редактор А.Ревин Техред Л.Сердюкова К(рректор M.Äeì÷èê

Заказ 1628/45 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полйграфическое предприятие, г. Ужгород, ул. Проектная, 4