Устройство для нормализации чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к иячяслительной технике и позволяет нормализовать как положительные, так и отрицательные числа с плавающей запятой , представленные в обратном коде. Целью изобретения является расширение функциональных возможностей за счет нормализации отрицательных чисел . Поставленная цель достигается тем, что в устройстве, содержащем шифратор 4, сумматор-вычиситепь 5, сдвигатель 6 и узел 3 анализа, содержащий элементы И, группу элементов ИЛИ, группы элементов НЕ, в узел 3 анализа дополнительно введены элемент ИЛИ, группы элементов ИЛИ, группа элементов И и элементы И с соответствующими связями. 2 ил. (Я с Со О Ч 1 СП 4;

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (511 4 G .06 F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4008925/24-24 (22) 03.01.86 (46) 30.04.87. Вюл. Ф 16 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) Н.И,Глотов, В.Е.Шахматов и О.П.Саримахмудова (53) 681.325(088 ° 8) (56) Авторское свидетельство СССР

У 1140113, кл. G 06 F 7/38, 1983.

Процессор ЕС 2060, Т02. Арифметико-логический блок. — М.: 1977, с.16, 65, 156.

„„SU„„1307454 А 1 (54) УСТРОЙСТВО ДПЯ НОРМАЛИЗАЦИИ

ЧИСЕЛ (57) Изобретение относится к вычислительной технике и позволяет нормализовать как поло;кительные, так и отрицательные числа с плавающей запятой,представленные в обратном «оде.

Целью изооретения является расщирение функциональных возможностей за счет нормализации отрицательных чисел. Поставленная цель достигается тем, что в устройстве, содержащем шифратор 4, сумматор-вычиситель 5„ сдвигатель 6 и узел 3 анализа, содержа" щий элементы И, группу элементов ИЛИ, группы элементов НЕ в узел 3 анали1

9 за дополнительно введены элемент ИЛИ, группы элементов ИЛИ, группа элементов И и элементы И с соответствующими связями. 2 ил .

1307454 знаке числа, через элемент ИЛИ 13

1 передается на выход, а через элемент

НЕ 14., перекрывает все элементы И группы 15. Если, например, две старшие тетрады равны нулю, то на выходе элемента И 10 появляется потенциал, который через элемент И 17>, элемент

ИЛИ 13 и элемент И 15 передается на выход (сдвиг вправо на 2), а через элемент НЕ 14 перекрывает после3 дующие элементы группы И 15. Если ненормализованное и отрицательное число содержит, например, две старшие тетрады, равные единице, то на выходе элемента ИЛИ 10 появляется потенциал, который через элемент И 18 и далее так же, как и для положительных чисел, передается выход (сдвиг вправо на 2), сигналы с выхода поступают на вход шифратора 4, который формирует, в зависимости от величины сдвига двоичный код,. управляющий сдвигателем 6 в виде блока мультиплексоров, число коммутируемых входов которых равно (N+1). При этом на первые входы всех мультиплексоров с входа 2 поступают разряды числа, сдвинутого вправо на тетраду, на вторые входы — разряды несдвинутого числа, на третьи входы — разряды числа, сдвинутого влево на тетраду, на четвертые входы — разряды числа, сдвинутого влево на две тетрады и т.д. Освободившиеся при сдвиге влево разряды заполняются нулями. Получившийся на выходе шифратора код является одновременно кодом коррекции порядка, который складывается или вычитается на сумматоре-вычитателе 5 с исходным порядком нормализуемого числа. На выходе устройства получают нормализованное число и скорректированный порядок.

Формула и з о б р е т е н и я

Устройство для нормализации чисел, / содержащее сумматор- вычи слит ель, сдвигатель, шифратор и узел анализа, содержащий первую группу элементов

ИЛИ, две группы элементов И, группу элементов НЕ и два элемента И, причем инверсные входы старшего и младшего разрядов знака входа устройства соединены соответственно с первым и вторым входами первого элементе И у — ла анализа, первый и второй входы второго элемента И которого соединеИзобретение относится к вычислительной технике и может быть использовано при построении процессора для обработки чисел с плавающей запятой.

Цель изобретения — расширение функ 5 циональных возможностей за счет нормализации отрицательных чисел.

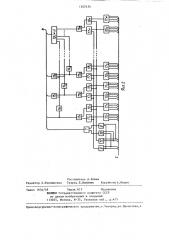

На фиг.l представлена структурная схема устройства для нормализации чисел; на фиг.2 — функциональная схема 1О узла анализа.

Устройство для нормализации чисел содержит выход 1 устройства, вход 2 устройства, узел 3 анализа, шифратор

4, сумматор-вычитатель 5 и сдвигатель 6.

Узел 3 анализа содержит элемент

ИЛИ 7, первый 8 и второй 9 элементы

И, первую 10 и вторую ll группы эле" ментов ИЛИ, третий элемент И 12, третью группу 13 элементов ИЛИ, группу 14 элементов НЕ 14 первую группу

15 элементов И, .четвертый элемент

И 16, вторую 17 и третью !8 группы элементов И.

Устройство для нормализации чисел работает следующим образом.

Ненормализованное число в обратном коде с двумя знаковыми разрядами с входа 2 поступает на узел 3 анализа и одновременно на вход сдвигателя

6, порядок числа поступает также с входа 2 на первый вход сумматора-вычитателя 5. Число представленное с плавающей запятой, имеет основание 35

"16". Поэтому нормализация осуществляется потетрадно. На элементах И 8, 9, 12 и 16 узла 3 анализа осуществляется анализ знаковых разрядов. Если число положительное, то устанавливается потенциал на выходе элемента И 8, если число отрицательное, то потенциал устанавливается на выходе элемента И 12, при переполнении числа (знаковые разряды при этом разные) 45 на выходе элемента И 9 или элемента

И 16 устанавливается потенциал, который через элемент ИЛИ 7 передается на шифратор 4 как сигнал на сдвиг вправо и на сумматор-вычитатель 5 как сигнал, управляющий сложением и вычитанием. Если число нормализованно, то несовпадение значений разрядов: первой старшей тетрады обеспечивает на выходах элементов ИЛИ IQ и 11!по- 55 тенциал, который через элемент И 17„ при положительном знаке числа или через элемент И 18 при отрицательном з 1307 ны соответственно с инверсным входом старшего и с прямым входом младшего разрядов знака входа устройства, прямые входы разрядов мантиссы вхоДы которого соединены соответственно с входами элементов ИЛИ первой группы узла анализа, вход первого элемента

НЕ группы и выходы элементов И первой группы которого соединены соответственно с входами разрядов, кроме 10 старшего, шифратора, прямые входы старшего н младшего разрядов знака и разрядов мантиссы входа устройства соединены соответственно с входами разрядов информационного входа сдви- 15 гателя, прямые входы разрядов порядка устройства соединены соответственно с входами разрядов первого информационного входа сумматора-вычитателя, второй информационный вход ко- 20 торого соединен с входом величины сдвига сдвигателя и выходом шифратора, выходы сдвигателя и сумматора-вычитателя сдвигателя и сумматора-вычитателя являются выходом устройства, 25 причем в узле анализа выход первого элемента И соединен с первыми входами элементов И второй группы, вторые входы которых соединены с выходами соответствующих элементов ИЛИ пер--Ю вой группы, выход k-го элемента НЕ группы (k=1-(N-1); N — количество тетрад мантиссы числа) соединен c k-ми входами элементов И с k-го по (N-1)-й первой группы, о т л и ч а ю щ е е — 35 с я тем, что, с целью расширения функциональных возможностей за счет нормализации отрицательных чисел, 454 4 узел анализа содержит третий и четвертый элементы И, элемент ИЛИ, вторую и третьИ группы элементов ИЛИ, и третью группу элементов И, причем инверсные входы разрядов мантиссы входа устройства соединены соответственно с входами элементов ИЛИ второй группы узла анализа, выход элемента

ИЛИ которого соединен с входом старшего разряда шифратора и управляющим входом сумматора-вычитателя, прямые входы старшего и младшего разрядов знака входа устройства соединены соответственно с первым и вторым входами третьего элемента И узла анализа, причем в узле анализа второй вход первого элемента И и первый вход третьего элемента И соединены соответственно с первым и вторым входами четвертого элемента И, выход которого и выход второго элемента И соединены соответственно с первым и вторым входами элемента ИЛИ, выход третьего элемента И соединен с первыми входами элементов И третьей группы, вторые входы которых соединены с выходами соответствующих элементов ИЛИ, второй группы,.выходы элементов И второй и третьей групп соединены соответственно с первыми и вторыми входами элементов ИЛИ третьей группы, выходы элементов ИЛИ третьей группы, кроме старшего, соединены соответственно с входами элементов НЕ группы„ выход (k+1)-го элемента ИЛИ третьей группы соединен с (k t 1) "и входом k- го элемента И первой группы. юг. 1

1307454

Составитель A. Клюев

Редактор Л. Пчолинская Техред Л.Олейник Корректор А, Ильин

Заказ 1634/49 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.ужгород,ул.Проектная,4