Способ управления электроприводом лифта с двухскоростным асинхронным электродвигателем и устройство для его осуществления

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) OI) CSI) 4 Н 02 Р 5/40

М!

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3998799/24-07 (22) 30.12.85 (46) 30.04.87. Бюл. II- 16 (71) Всесоюзный научно-исследовательский и проектно-конструкторский институт по автоматизированному электроприводу в промьппленности, сельском хозяйстве и на транспорте, Одесский политехнический институт и Всесоюзный научно-исследовательский и проектно-конструкторский институт по преобразовательной технике (72) А. Н. Семячкин, Г. С. Липатов, О. А. Андрющенко и Г. А. Смердов (53) 621.316.717(088.8) (56) Монтаж лифтов и канатных дорог.

Справочник строителя. M.; Стройиздат, 1983, с. 142, Авторское свидетельство СССР

II(1030941, кл. H 02 P 5/40, 1983. (54) СПОСОБ УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДОМ ЛИФТА С ДВУХСКОРОСТНЫМ АСИНХРОНHbIM 3JIEKTP0gBHIATEJIEM И УСТРОЙСТВО

ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (57) Изобретение относится к электротехнике и может быть использовано для управления электроприводами лифтов и других подъемно-транспортных механизмов, к качеству диаграммы движения и точности останова которых предъявляются повьппенные требования, а характер нагрузки и цикличность работы эквивалентны лифтам. Целью изобретения является повышение производительности лифта и повышение точности его останова. Поставленная цель достигается путем введения уравновешивания статического момента нагрузки двигательным моментом при разгоне лифта, введением позиционирования при торможении, что обеспечивается с помощью задатчика интенсивности 4, регулятора приращения положения 6, регулятора частоты врашения 7, переключающего блока

1О, распределителя импульсов

11. 2 с. и. и 5 з. п. ф-лы. 6 ил.

1 13075

Изобретение относится к электротехнике и может быть использовано при проектировании систем электропривода лифтов и других подъемнотранспортных механизмов, к качеству диаграммы движения которых и точности останова в заданном месте предьявляются повьппенные требования, а характер нагрузки и цикличность работы эквивалентен лифтам. 10

Цель изобретения — повьппение производительности лифта и повышение точности его останова.

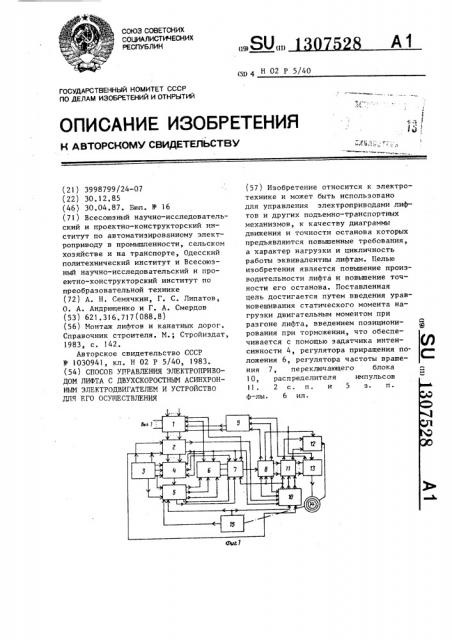

На фиг. 1 показана схема устройства управления электроприводом лифта с двухскоростным асинхронным электродвигателем; на фиг. 2 — схема регулятора частоты вращения; нафиг. 3схема регулятора приращения положения, на фиг. 4 — схема переключающего блока; на фиг. 5 — схема системы импульсно-фазового управления; на фиг. 6 — схема распределителя импульсов.

Устройство для управления электроприводом лифта с двухскоростным асинхронным электродвигателем (фиг. 1) содержит блок 1 обработки входных команд, вторым выходом связанный с пер- 30 вым входом управляющего блока 2, вторым и третьим входом соединенный соответственно с первым и вторым выходами генератора 3 тактовых импульсов, соединенного третьим, четвертым и пя- 35 тым выходами с вторым, третьим и четвертым входами задатчика 4 интенсивности, первый выход которого соединен с первым входом блока 5 синхронизации, первым, вторым и третьим выхода- 40 ми связанного с первым, вторым и тре. тьим входами регулятора 6 приращения положения, подключенного первым,вторым и третьим выходами к первому, второму и третьему входам регулятора 45

7 частоты вращения, первый выход которого связан с вторым входом системы 8 импульсно-фазового управления, соединенной третьим и четвертым выходом соответственно с вторым и третьим 50 входами блока 9 защиты, а третьим и четвертым входом и вторым выходом— с третьим и четвертым выходами и первым входом соответственно переключающего блока 10, связанного первым, вторым и третьим выходами с первым, вторым и третьим входами распределителя 11 импульсов, вторым и третьим выходом соединенного с вторым и тре28 тьим входами упр авля ем о г о выпрямителя 12, а первым десятиканальным выходом — с управляющим десятиканальным входом тиристорного преобразователя 13, силовой выход которого через двухскоростной асинхронный двигатель 14 связан с датчиком 15 частоты вращения, второй выход которого подключен к второму входу переключающего блока 1О, соединенного пятым входом с третьим входом управляющего блока 2, третьим входом — с третьим выходом управляющего блока

2, а четвертым входом — с пятым входом регулятора 7 частоты вращения, четвертым входом регулятора 6 приращения положения, шестым входом задатчика 4 интенсивности и вторым выходом управляющего блока 2, первым

1 выходом связанного с первым входом задатчика 4 интенсивности, пятый вход которого подключен к третьему входу блока 1 обработки входных команд и пятому входу регулятора .6 приращения положения, авторой выход -к четверто. му входу регулятора 7 частоты вращения, вторым выходом соединенного с четвертым входом блока 1 обработки входных команд, восьмым входом- с третьим входом системы 8 импульсно-фазового управления, а шестыми седьмымвходами — соответственно с четвертым и пятым выходами блока 5 синхронизации, второй и пятый входы которого подключены соответственно к пятому и шестому выходам генератора 3 тактовых импульсов, а третий и четвертый входык первому и второму выходам датчика

15 частоты вращения, первый шестиканальный выход системы 8 импульсно-фазового управления соединен с четвертым шестиканальным входом распределителя 11 импульсов, а первый трехфазный вход — с силовым входом управляемого выпрямителя 12, связанного силовым выходом с обмоткой низшей частоты вращения асинхронного двигателя 14, силовой вход тиристорного преобразователя 13 соединен с силовым входом управляемого выпрямителя 12, .а дополнительный выход — с первым входом блока 9 защиты, первый и второй выходы которого подключены соот-ветственно к второму и третьему входам блока 1 обработки входных команд.

Регулятор 7 частоты вращения (фиг. 2} содержит блок 16 счетчиков, блок 17 регистров, первый инвертор

528 4 и 35, блок 36 цифроаналогового преобразователя, первый вход логического элемента И-НЕ 28 объединен с первым входом блока 30 коммутатора каналов и образует второй вход регулятора 6 приращения положения, выход логического элемента И-НЕ 28 через первый инвертор 29 соединен с вторым входом блока 30 коммутатора каналов, третий вход которого объединен с вторым входом логического элемента

И-НЕ 28 и образует первый вход регулятора 6 приращения положения, четвертый вход блока 30 коммутатора каналов образует третий вход регулятора 6 приращения положения, пятый вход блока 30 коммутатора каналов соединен с выходом второго инвертора

31, вход которого образует пятый вход регулятора 6 приращения положения, первый и второй выходы блока 30 коммутатора каналов соединены соответственно с первым и вторым входом первого счетчика 32 и образуют первый и второй выходы регулятора 6 при. ращения положения, первый и второй

1 выходы первого счетчика 32 соединены соответственно с первым и вторым входами второго счетчика 34, первый и второй выходы которого соединены с первым и вторым входами третьего счетчика 35, третьи входы счетчиков

32, 34 и 35 объединены и подключены к выходу третьего инвертора 33, вход которого образует четвертый вход ре— гулятора 6 приращения положения, выход третьего счетчика 35 и третьи выходы второго и первого счетчиков

34 и 32 соединены соответственно с первым, вторым и третьим входами блока 36 цифроаналогового преобразователя, выход которого образует третий выход регулятора 6 приращения положения.

Регулятор 6 приращения положения (фиг. 3) содержит логический элемент 55

И-HE 28, первый инвертор 29, блок 30 коммутатора каналов, второй инвертор

31, первый счетчик 32, третий инвертор 33, второй и третий счетчики 34

3 1307

18, мультиплексор 19, первый ключ 20, второй инвертор 21, интегрирующий усилитепь 22, третий ключ 23, суммирующий усилитель 24, пропорциональный усилитель 25 и второй ключ 26.

Первый, второй и третий входы блока

16 счетчиков образуют соответственно первый, второй и седьмой входы регулятора 7 частоты врашения, выход блока 16 счетчиков соединен с первым >0 входом блока 17 регистров, второй вход которого подключен к выходу первого инвертора 18, вход которого образует шестой вход регулятора 7 частоты вращения, первый, второй, третий 15 и четвертый выходы блока 17 регистров соединены соответственно с первым входом цифроаналогового преобразователя 27 и с первым, вторым и третьим входами мультиплексора 19, выход ко- 20 торого образует второй выход регулятора 7 частоты вращения, второй вход цифроаналогового преобразователя 27 образует третий вход регулятора 7 частоты вращения, первые входы интегрирующего и пропорционального усилителей 22 и 25 и первые входы первого и второго ключей 20, 26 объединены и ,1 подключены к выходу цифроаналогового преобразователя 27, входы первого и второго ключей 20, 26 объединены и подключены к выходу второго инвертора

21, вход которого образует восьмой вход регулятора 7 частоты вращения, второй выход первого ключа 20 соеди- 35 нен с вторым входом интегрирующего усилителя 22, третий вход которого подключен к первому выходу третьего ключа 23, вход которого образует пятый вход регулятора 7 частоты враще- 40 ния, выход интегрирующего усилителя

22 и второй выход третьего ключа 23 объединены и соединены с первым входом суммирующего усилителя 24, второй выход второго ключа 26 соединен с 4> вторым входом пропорционального усилителя 25, выход которого подключен к второму входу суммирующего усилителя 24, третий вход и выход которого образуют соответственно четвертый 50 вход и первый выход регулятора 7 частоты вращения.

Переключающий блок 10 (фиг . 4 ) содержит первый инвертор 37, вход которого образует четвертый вход переключающего блока 10 а выход соединен с первым входом первого коммутатора 38 каналов, первый, второй, третий, четвертый и пятый входы которого подключены к первым, вторым, третьим, четвертым и пятым входам второго 39 и третьего 40 коммутаторов каналов, подключенных пятыми входами к пятому выходу задатчика 41 режима работы, соединенного первым

BblxopoM BToDbIM входом первой схемы

42 выдержки времени, вторым выходомс вторым входом второй схемы 43 выдержки времени, а третьим выходом— с вторым входом логического элемен— та И-НЕ, выход которого подключен к входу второго инвертора 45, выход первого коммутатора 38 каналов соединен с первым входом первой схемы

42 выдержки времени, четвертый вход которой связан с выходом второй схемы 43 выдержки времени, соединенной четвертым входом с выходом первой схемы 42 выдержки времени, третий вход которой образует пятый вход переключащего блока 10 и объединен с третьим входом второй схемы 43 выдержки времени, связанной первым входом с выходом второго коммутатора 39 каналов, второй, третий и четвертый входы которого образуют соответствен- 20 но первый, второй и третий входы переключающего блока 10, выход третьего коммутатора 40 каналов соединен с первым входом логического элемента 44

И-НЕ, причем первый выход переключающего блока 10 образован выходом первой схемы 42 выдержки времени, второй — выходом второй схемы 43 выдержки времени, третий — выходом второго инвертора 45, а четвертый — четвертым З0 выходом задатчика 41 режима работы.

Система 8 импульсно-фазового управления (фиг. 5) содержит блок 46 переключения и адаптации, первый, второй и третий входы которого образуют соответственно второй, четвертый и третий входы системы импульсно-фазового управления, а третий выход соединен с входом блока 47 формирова- 40 ния знака, подключенного вторым выходом к второму входу блока 48 извлечения модуля, соединенного выходом с вторым входом суммирующего усилителя

49, выход которого связан через управляемый генератор 50 с вторым входом блока 51 счетчиков, подключенного выходом к.второму входу блока 52 Dтриггеров, первым входом соединенного с входами блока 53 контроля фазировки, блока 54 формирования импуль— сов сброса и вторым выходом блока 55 синхронизации, первый выход которого подключен к входу блока 56 контроля

3 напряжения, а первый, второй и третий 55 входы образуют первый трехфазный вход системы 8 импульсно-фазового управления, первый выход блока 46 переключения и адаптации соединен с первым

28 6 входом суммирующего усилителя 4У, второй выход — с первым входом блока

48 извлечения модуля, второй выход блока 55 синхронизации фазных напряжений подключен к первому входу блока 51 счетчиков, а выход блока 54 формирования импульсов сброса соединен с третьим входом блока D-триггеров 52, причем первый шестиканальный выход системы 8 импульсно-фазового управления образован выходами блока

D-триггеров 52, второй выход — первым выходом блока 47 формирования знака, третий — выходом блока 53 контроля фазировки, а.четвертый — выходом блока 56 контроля напряжения. !

Распределитель 11 импульсов (фиг. 6) содержит генератор 57.промежуточной частоты, десять схем 58-67 совпадения, две схемы 68, 69 объединения и бгок 70 импульсных трансформаторов. Первые входы первой и второй схем 58, 59 совпадения объединены и образуют третий вход распределителя 11 импульсов, объединенные первые входы. седьмой, восьмой, девятой, десятой схем 64-67 совпадения и первой и второй схем 68 и 69 объединения образуют второй вход распределителя 11 импульсов, второй вход первой схемы 68 объединения образует первый канал четвертого шестиканального входа распределителя 11 импульсов, второй вход — второй канал четвертого шестиканального входа распределителя 11 импульсов, объединенные первые входы третьей, четвертой, пятой, шестой схем совпадения 60-63 и третьи входы первой и второй схем

68 и 69 объединения образуют первый вход распределителя 11 импульсов, объединенные вторые входы шестой и десятой схем 63 и 67 совпадения образуют третий канал четвертого шестиканального входа распределителя 11 импульсов, обьединенные вторые входы пятой и девятой схем 62 и бб совпадения образуют четвертый канал четвертого шестиканального входа распределителя 11 импульсов, объединенные вторые входы второй, четвертой и вось. мой схем59, 61 и 65 совпадения образуют пятый каналчетвертого шестиканального входа распеделителя 11 импульсов, объединенные вторые входы первой, третьей и седьмой схем 58, 60 и 64 совпадения образуют шестой канал четвертого шестиканального входа расп

7 13075 делителя 11 импульсов, выход генератора 57 промежуточной частоты соединен с третьими входами всех десяти схем 58-67 совпадения и с четвертыми входами схем 68, 69 объединения, выходы с первой по десятую схему 58-67 совпадения и схем 68 и 69 объединения подключены соответственно к входам с первого по двенадцатый блока

70 импульсных трансформаторов, первыйИ и второй выходы которого образуют соответственно второй и третий выходы распределителя 11 импульсов, выходы с третьего по двенадцатый блок 70 импульсных трансформаторов образуют 15 первый десятиканальный выход распределителя ll импульсов.

Способ управления электроприводом лифта с двухскоростным асинхронным электродвигателем осуществляют следу- 20 ющим образом.

При получении от системы автоматики лифта команды на движение в ту или иную сторону блок 1 обработки входных команд вырабатывает на своих вторых выходах соответственную команду "Подъем" или "Спуск", а на первых

В момент растормаживайия двигателя к его валу прикладывается момент нагрузки, величина и знак которого, определяются степенью уравновешенности кабинной и противовесной ветви канатов и однозначно определяются величиной груза, находящегося в этот момент времени в кабине лифта. При этом в результате растормаживания весь неуравновешенный груз, ранее удерживающийся механическим тормозом, прикладывается к валу двигателя, который должен быстро набрать под воздействием системы регулирования двигательный момент, по величине равный статическому моменту нагрузки, но противоположный ему по знаку. При этом, если не принимать специальных мер по уравновешиванию статического момента нагрузки двигательным моментом, кабина лифта начнет движение в сторону, определяемую действием момента нагрузки, а при приложении управляющего воздействия в виде оптимальной диаграммы движения произойдет ее существенное искажение. Введение в начале цикла движения этапа уравновешивания позволяет устранить ис- 50 кажение задаваемой диаграммы движения и осуществить разгон до установившейся скорости именно по той диаграмме движения, которая и задана, т,е, по оптимальной траектоРии движения. После окончания разгона движения на установившейся скорости осуществляют не на естественной механической характеристике, статизм кото28 8 рой составляет как правило около 5%, а на регулировочных механических характеристиках, не имеющих статизма, т.е. на которых частота вращения электродвигателя не зависит от нагрузки. При этом в зависимости от знака момента нагрузки на валу двигателя формируются или двигательные моменты по обмотке высшей частоты вращения, или тормозные методом динамического торможения по обмотке низшей частоты вращения. Такое разделение двигательных и тормозных режимов по различным обмоткам двигателя позволяет существенно снизить потери в статоре двигателя и, следовательно, его нагрев. Основным преимуществом изобретения является то, что к точке начала замедления кабина лифта подходит всегда на одной и той же скорости не зависимо от момента нагрузки на валу двигателя, что позволяет осуществить процесс замедления в заданную точку остановки без корректировки диаграммы движения на участке замедления и осуществлять процесс замедления по заданной оптимальной диаграмме движения в заданную точку остановки, строго поддерживая заданные оптимальной диаграммой движения величины ускорения и рывка, что существенно повышает комфортные показатели лифта в целом и повышает его производительность в силу отсутствия в конце диаграммы движения участка пониженной скорости. Для получения высокой точности останова на участке замедления в течение всего времени замедления осуществляется процесс позиционирования путем введения в управляющее воздействие составляющей пропорциональной рассогласованию положения заданного и полученного, т,е. f д !Ю, что позволяет произвести остановку на уровне заданного этажа с точностью не хуже +1 мм без участка понижейной скорости, тем самым повышая производительность лифта.

Устройство, реализующее данный способ управления, функционирует следующим образом.

13075

1 рс () рс р . р рс

U (t) = П,(- ) + U,(t), Таким образом, введение на вход регулятора 7 частоты вращения сигнала

55.U (t), пропорционал> Horo заданному

Q выходах — команду растормажив ания электромеханического тормоза, в результате чего происходит растормаживание механической тормозной системы и к валу двигателя 14 прикладывается момент нагрузки. В результате управляющий блок 2 выходит из исходного состояния и по своему второму выходу переводит регулятор 6 приращения положения, регулятор 7 частоты вращения 10 и переключающий блок 10 в рабочее состояние, однако задатчик 4 интенсивности в это время переводится в состояние ожидания следующей команды от управляющего блока 2, При этом 15 система регулирования находится в состоянии уравновешивания, и задание частоты вращения от задатчика 4 интенсивности на вход регулятора 7 частоты вращения не поступает. С нача- 20 лом вращения двигателя при его растормаживании с выхода датчика 15 частоты вращения сигнал обратной связи по частоте вращения 1,, представляь>ос ющий собой частотно-импульсный сигнал, через блок 5 синхронизации поступает на второй вход регулятора б приращения положения и с его третьего выхода в виде аналогового сигнала поступает на третий вход регулЫ- З0

GS тора 7 частоть1 вращения, полностью определяя поведение системы регулирования на этапе уравновешивания. При этом знак сигнала управления U определяется логическим сигналом з>.gnM g5

> представляющим собой знак направления вращения двигателя 14, и воздействует на систему регулирования таким образом, чтобы удержать на месте кабину лифта на этапе уравновешивания 40 п1>и резком приложении к валу двигателя момента нагрузки. Учитывая, что сигнал U представляет собой рассогласование по положению заданного к полученному, т.е.! 45

I ! !!, = к, в!кп!! jlz, — к ., /ж, о

1 а также то, что на этапе уравновешивания сигнал задания частоты вращения ! равен нулю, т. e. f < = 0 поведение 3 системы регулирования в период уравновешивания определяется сигналом

<ар ! О

U = К sign Г dt> ь>ос

О что приводит к удержании кабины лифта на этаже при приложении момента нагрузки к валу двигателя независимо

28 10 от его величины и знака. По окончании времени уравновешивания управляющий блок 2 переходит в состояние "диаграмма" и, вырабатывая на своих первых выходах последовательность логических сигналов, управляет работой задатчика

4 интенсивности, инициируя появление на его первом выходе сигнала задания частоты вращения 1с> и на втором вы1 ходе сигнала задания частоты вращения

f и на втором выходе сигнала задаЫ ния ускорения U . В блоке 5 синхронизации частот происходит разделение во времени частот задания частоты вращения fä и обратной связи f

„ь>!>с а также син>сронизация с опорной частотой f знака направления вращения ! I

sign И . Выходные сигналы Гс> Г и

) OC ц! поступают на регулятор 6 приращения, где, с одной стороны,осуществляется определение рассогласования по положению П, а с другой — распреде> ление частот задания и обратной связи по различным выходам в соответствии с уровнями логических сигналов П и (1!. С первого и второго выхода частоты Г! и f поступают на первый и второй вход регулятора 7 частоты вра. щения. При этом по каналу f может ! поступать как Г >, так и f в заь>ос висимости от уровней сигналов П и !;> (аналогично и по каналу f ). В регуляторе скорости осуществляется определение разности частот задания и обратной связи по частоте вращения, суммирование с ней сигналов U> и 11„ а также преобразование полученной суммы в соответствии с его передаточной функцией ПИ-регулятора

Работой цифроаналогового регулятора 7 частоты вращения управляет блок 5 синхронизации сигналами с четвертого и пятого выхода F и F соответственно. Выходной сигнал регулятора 7 частоты вращения U имеет вид ускорению, придает системе регулирования инвариантность по управляющему воздействию. Воздействуя на вход системы 8 импульсно-фазового управле!

307528 !2!

50 вращения, осуществляет изменение его параметров, коэффициента передачи и постоянной времени. Блок 9 защиты осуществляет защиту двигателя и силовых тиристоров от токов короткого замыкания и перегрузки, воздействуя своим первым выходом на второй вход блока 1 обработки входных команд. При

I I срабатывании защиты система регулирования автоматически переводится в

55 ния, выходной сигнал U регулятора 7 частоты вращения изменяет угол регулиРованиЯ 0(TH1IHoTo1IsHH THPHcTQPHQIo преобразователя 13 или управляемого выпрямителя 12, Распределитель 11 импульсов осуществляет распределение импульсов регулирования в зависимости от состояния логических сигналов В,Н и ДТ на своих первом, втором и третьем входах. Работой распределителя

11 импульсов управляет переключаюший блок 10, который в Аункции входных

1 команд sign П sign G3 и 11„ь создает определенную комбинацию команд В, Н . и ДТ на выходах, при этом на установившейся скорости и при работе привода с моментом нагрузки, близким к нулю, в зависимости от знака сигнала управления sign U двигатель 14 переводится либо в двигательный режим работы по обмотке высшей частоты врашения командой E или Н, в зависимости от направления движения, либо— в тормозной по обмотке низшей частоты вращения командой ДТ, обеспечивая при этом равенство скорости заданной и полученной. Управление двигателем

14 в двигательных режимах обеспечивается тиристорным преобразователем

13, выполненным по реверсивной схеме и содержащем 10 тиристорных ключей, а в тормозном — с помошью управляемого выпрямителя 12. В зависимости от режима работы ручной или автоматический переключающий блок 1Î формирует на своем четвертом выходе высокий или низкий уровни и тем самым переключает вход системы 8 импульсно-фазового управления либо к выходу регулятора 7 частоты вращения в автоматическом режиме работы, либо к внутрен1 нему источнику опорного напряжения в ручном режиме работы. В исходном состоянии логический сигнал ао блокирует работу переключающего блока 10.

В режиме динамического торможения переключающий блок 10, воздействуя на восьмой вход регулятора 7 частоты исходное состояние а . При подаче команды на замедление регулятор 6 приранения положения воздействует на систему регулирования таким образом, чтобы свести к нулю рассогласование по положению и тем самым в заданную точку без участка пониженной скорости и с высокой точностью.

Регулятор 7 частоты вращения выполнен в виде цифроаналогового адаптивного ПИ-регулятора. Цифровая часть регулятора 7 частоты вращения осуществляет определение разности частот задания скорости и обратной связи по скорости, которые поступают на первый и второй входы регулятора 7 по каналам f и 7 на первый и второй вход блока счетчиков 16. На третий вход блока счетчиков 16 поступает тактовая частота Г, определяющая периоды счета импульсов частот f и 1 и период обнуления блока 16. Канал частоты Г! поступает на вычитающий вход блока 16 счетчиков, а канал частоты — на суммирующий вход, В результате этого на выходах блока 16 счетчиков за период счета импульсов, определяемый тактовой частотой Рз, накапливается код разности частот задания и обратной связи по скорости в двоичном коде, По импульсам второй тактовой частоты F этот код перепиь сывается в блок 17 регистров. Частоты I и F< сдвинуты по времени друг относительно друга на 180 эл.град., в результате чего сначала по частоте

F происходит запись полученного кода разности частот в блок 17 регистров, а затем по частоте происходит запись полученного кода разности частот в блок 17 регистров, а затем по частоте F происходит обнуление блока 16 счетчиков. Затем этот процесс повторяется. Код разности частот задания и обратной связи с первого выхода блока 17 регистров поступает на первый вход цифроаналогового преобразователя 27, на выходе которого образуется аналоговый сигнал, пропорциональньп разности заданной и полученной частот вращения, суммированный с сигналов П посту.ь пающим на второй вход цифроаналогового преобразователя 27. Аналоговая часть регулятора 7 частоты вращения представляет собой адаптивный пропорциональна-интегральный регулятор, содержащий отдельно интегральную со13

1307528 14

55 ставляющую, выполненную на интегрирующем усилителе 2, отдельно пропорциональную составляющую, выполненную на пропорциональном усилителе 25, и суммирующий усилитель 24, на третий вход которого поступает сигнал U пропорциональный заданному ускорению.

Изменение в режиме динамического торможения постоянной времени регулятора 7 частоты вращения осуществляется

I с помощью ключа 20, а коэффициента передачи — с помощью ключа 26, причем в режиме динамического торможения происходит замыкание ключей 20 и 26, в результате чего происходит уменьшение постоянной времени и увеличение коэффициента передачи. Ключ

23 осуществляет шунтирование емкости в обратной связи интегрирующего усилителя 22 на стоянке лифта с наложенным тормозом, так как при этом происходит размыкание обратной связи по частоте врашения. При разряде ко— ды с второго, третьего и четвертого выходов блока 17 регистров, поступающие на входы мультиплексора 19, позволяют контролировать максимальное рассогласование Sm заданной и полу. (пал ченной скоростей и производить аварийное отключение привода, переводя систему регулирования в исходное состояние.

Регулятор 6 приращения положения выполнен в виде цифрового интегрирующего регулятора и формирует на выходе сигнал полярность которого определяется как (I знаком разницы частот f u f так ь оР и уровнями логических си»"налов Г и (д(. Основной алгоритм работы регулятора б приращения положения реализован на мультиплексоре, составляюшим блок 30 коммутатора каналов ° Ha

его входы поступают частоты задания, частоты вращения f< обратной связи по частоте вращения Г, сумма час1 l »ос тот Г(., + f формируюпаяся элеос ментами 28 и 29, а также управляющие сигналы с и П, В зависимости от ( уровней управляющих сигналов четвертого и пятого входов блока 30 коммутатора каналов на его первый и второй выходы поступает та или иная частота. Частоты с выхода блока 30 коммутатора каналов поступают на входы

f0

40 первого счетчика 32, на первые выходы которого последовательно включены счетчики 34 и 35, причем первые входы счетчиков представляют собой входы вычитания, а вторые — суммирования.

Таким образом, благодаря тому, что одна из частот поступает на вычитающий вход, а другая — на суммирующий на выходах счетчиков осуществляется

I накопление кода разности частот, что по своему принципу соответствует интегрированию разности частот. Обнуление счетчиков производится при переходе системы регулирования в исходное состояние сигналом а с выхода инвертора 33. Двоичный код с выхода счетчиков поступает на входы блока

36 цифроаналогового преобразователя, на выходе которого образуется аналого- вый сигнал рассогласования положений

П

Переключающий блок 10 представляет собой комбинационное логическое устройство, которое в соответствии с заложенными в него алгоритмом по состоянию входных управляющих сигналов sign UI1 sign Q и ci)„@ формирует выходные координаты В, Н и ДТ. Входной сигнал а, поступающий на .первые входы коммутаторов каналов 38, 39 и

40, через инвертор 37 блокирует работу коммутаторов в исходном состоянии. В автоматическом режиме работы, определяемом задатчиком 14 режима работы, с его пятого выхода логический сигнал поступает на пятые входы коммутаторов каналов 38, 39 и 40 и организует формирование сигналов ВА, НА, ДТА в автоматическом режиме в зависимости от состояния логических сигналов з дп П, sign M и Я„, При этом

ВА = („ni(n !!, + sign (. ninn(nj;

НА . = (Ä sign U„ + sign Б sign И)»

ДТА = (sign U(„ si ig Ыа у„д + sign UI1((x " " M Q(() В ручном режиме работы управление осуществляется с помощью кнопок задатчика 41 режима работы, на выходах которого формируются команды ручного режима работы ВР, HP и ДТР. Команды

BA u BP поступают на первый и второй входы схемы 42 выдержки времени, а команды HA u HP — на аналогичные вхо1307528

1 1 с с с 360

55 ды схемы 43 выдержки времени. На третьи входы схем 42 и 43 вьдержки времени поступает тактовая частота Г, 1000 Гц, Назначение схем 42 и 43, вьдержки времени — создать задержку на подачу команд В и Н на распределитель 11 импульсов при переключении групп тиристоров для исключения возможности коротких замыканий. Вьдержка времени, формируемая схемами 42 и

43 вьдержки времени составляет 11мс, что вполне достаточно для запирания тиристоров, выходящих из работы, и не является большим с точки зрения влияния на регулировочные характери-! стики системы регулирования. Для по вышения надежности работы схемы 42 и 43 выдержки времени сблокированы перекрестными связями по своим выхо— дам, т ° е. выходной сигнал Н схемы 43 выдержки времени подан на четвертый вход схемы 42 выдержки времени, а его выходной сигнал В подан на четвертый вход схемы 43 выдержки времени. Логические команды ДТА с выхода коммутатора каналов 40 и ДТР с третьего выхода задатчика режима работы

41 поступают на входы логического элемента 44-Н-HE и через инвертор 45 сформированная команда ДТ поступает на выход переключающего блока 10.

ДТ = ДТА ° ДТР = ДТА + ДТР.

Логическая команда ДТ не имеет в своем канале элементов выдержки времени в силу того, что управление режимом динамического торможения осуществляется от отдельного управляемого выпрямителя 12 и отдельной обмоткой двигателя 14.

Система 8 импульсно-фазового управления выполнена в виде аналого— цифровой системы управления. На входе системы 8 импульсно-фазового управления установлен блок 46 переключения и адаптации, на входы которого поступают аналоговый сигнал управления U с выхода регулятора 7 частоты врашения и логические управляющие сигналы Режим" ИДТ из переключающего блока 10. В соответствии с уровнем логического сигнала "Режтж" блок 4 переключения и адаптации пропускает на второй выход сигнал управления в ручном режиме, С третьего выхода блока 46 переключения и адаптации сигнал управления поступает на блок 47 формирования знака, на втором выходе

40 которого формируется сигнал з 1п необходимый для работы переключающего блока 10, а с первого выхода анало- . гичный сигнал поступает на первый вход блока 48 извлечения модуля, управляя работой последнего таким образом, что на его выходе всегда фор— мируется сигнал, пропорциональный модулю сигнала управления, т.е, /11„, поступающий íà первый вход суммирующего усилителя 49. Суммирующий усилитель 49 осуществляет ограничение по максимуму и по минимуму сигнала ! U I „а также производит изменение величины ограничения по максимуму в режиме динамического торможения путем воздействия на второй вход суммирующего усилителя 49 сигналом с первого выхода блока 46 переключения и адаптации, что необходимо при переходе привода от двигательного к тормозному режиму работы. С выхода суммирующего усилителя 49 сигнал управления поступает на вход управляемого генератора 50, на выходе которого образуется частота Г обратно пролорпиональная сигналу управления на входе, которая поступает на первый вход блока 51 счетчиков. Блок 51 счетчиков осуществляет подсчет числа импульсов за период синхронизирующего напряжения каждой из фаз и при появлении логической единицы в старшем разряде по своему первому входу записывает эту единицу в блок D-триггеров 52, на выходе которого при этом формируется импульс управления тиристором с углом регулирования, определяемого по выражению

Синхронизируюш.-;е напряжения, поступающие на вторые входы блока 51 счетчиков, на входы блока 54 формирования импульсов сброса, блока 53 контроля фазировки и вторые входы блока

D-триггеров 52 с второго выхода блока 55 синхронизации фазных напряжений, организуют появление импульсов на выходах блока D-триггеров 52 под положительной и отрицательной полуволной фазных напряжений фаз А, В и

С. Блок 56 контроля напряжения осущестьляет контроль напряжения сети, и при его сню ении более чем íà 15Х подает в блок 9 защиты команду на отключение. Блок 53 контроля фазировки

1307528

30 осуществляет защиту привода от изме- нения последовательности фаэ и от обрыва любой иэ фаз питающего напряжения.

Распределитель 11 импульсов осуществляет распределение импульсов, выработанных системой 8 импульсно-Аа зового управления между тиристорами тиристорного преобразователя 13 и управляемого выпрямителя 12 в зави- 10 симости от входных управляющих команд В, Н и ДТ. Распределитель ll импульсов содержит в качестве основных узлов 10 одинаковых схем совпадения 58-67 и две схемы объединения 15

68 и 69, Из десяти тиристоров тиристорного преобразователя 13 восемь работают в одном из режимов — либо в режиме "Вверх", либо в режиме

Вниз . В связи с этим логические 20 сигналы включения групп тиристоров

В и Н поступают каждый на четыре схе. мы совпадения, например логический сигнал  — на первые входы схем 6467 совпадения, а логический сигнал — 25

Н вЂ” на первые входы схем 60-63 совI падения. На вторые входы схем 60-67 совпадения поступают импульсы от системы S импульсно-фазового управления. о (+В), g,(-В), (+C), нь(-C).

Каждая схема совпадения содержит выходной транзистор (в качестве усилителя мон ности импульсов), инвертор и логический элемент И-НЕ. Логическая команда, например, В высоким логичес- ким уровнем разрешает прохождение импульсов через схему совпадения, а низким уровнем блокирует его работу.

Аналогично действуют логические команды H для схем 64-67 совпадения и

ДТ для схем 58-59 совпадения. Однако в тиристорном преобразователе 13 имеется два тиристора, включенных в фазу А, которые работают как в режиме

11

Вверх, так и в режиме Вниз, В

11 I I 45 связи с этим в канале фазы А установлены две схемы 68 и 69 объединения, на входе которой установлен логический элемент 2-2И-ИЛИ-HE на входы которого подаются логический элемент, сигналы В и Н и импульсы 11 (+А) для схемы 68 объединения и o .(-А) для схемы 69 объединения. При наличии на одном из входов схем объединения хотя бы одного логическог