Цифровой частотный детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике . Цель изобретения - расширение частотного диапазона детектирования , уменьшение погрешности детектирования во всем частотном диапазоне и устранение потери информации. Детектор содержит формирователь 1 импульсов , D-триггер 2, эл-т ИЛИ 5, два фильтра нижних частот (ФНЧ) 6 и 7, дифференциальный усилитель (ДУ) 8 и два канала 3 и 4 обработ.ки сигнала , состоящих каждый из ключа 9, тактового генератора 10, счетчика 11, цифрового компаратора 12, регистра 13 и двух формирователей 14 и 15 импульсов . Импульсы, аналогично сформированные в каналах 3 и 4, но во времени сдвинутые на текущий период входного сигнала, складываются во врем ени на эл-те ИЛИ 5, На его выходе образуется последовательность импульсов постоянной длительности, но различной частоты следования, которая через ФНЧ 6 и 7, имеющие различные частоты среза , поступает в ДУ 8, где осуществляется вычитание входных сигналов. Цель достигается введением канала 4, эл-та ИЛИ 5, ФНЧ 7 и ДУ 8. 3 ил. (Л 00 о О СО .1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1)4 Н 03 0 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3827357/24-09 (22) 17 ° 12,84 (46) 30.04.87. Бюл. № 16 (72) В,И.Закиров, Н,Д,Сергеев и Б.Ф.Воробьев (53) 62 1.376.3(088,8) (56) Патент Японии ¹ 52-35274, кл. Н 03 D 3/00, 1977.

Авторское свидетельство СССР

¹ 1061241, кл. Н 03 D 3/00, 1982. (54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР (57) Изобретение относится к радио4 технике, Цель изобретения — расширение частотного диапазона детектирования, уменьшение погрешности детектирования во всем частотном диапазоне и устранение потери информации, Детектор содержит формирователь 1 импульсов, D-триггер 2, эл-т ИЛИ 5, „„SU„„1307534 А 1 два фильтра нижних частот (ФНЧ) 6 и 7, дифференциальный усилитель (ДУ)

8 и два канала 3 и 4 обработки сигнала, состоящих каждый из ключа 9, тактового генератора 10, счетчика 11, цифрового компаратора 12, регистра

13 и двух формирователей 14 и 15 импульсов. Импульсы, аналогично сформированные в каналах 3 и 4, но во времени сдвинутые на текущий период входного сигнала, складываются во времени на эл-те ИЛИ 5, На его выходе образуется последовательность импульсов постоянной длительности, но различной частоты следования, которая через ФНЧ

6 и 7, имеющие различные частоты среза, поступает в ДУ 8, где осуществляется вычитание входных сигналов. Цель ру достигается введением канала 4, эл-та

ИЛИ 5, ФНЧ 7 и ДУ 8. 3 ил.

1 13075

Изобретение относится к радиотехнике и может использоваться в радиоприемных устройствах для частотного детектирования в широком диапазоне частот и уровней сигнала, Цель изобретения — расширение частотного диапазона детектирования, уменьшение погрешности детектирования во всем частотном диапазоне и устранение потери информации. 10

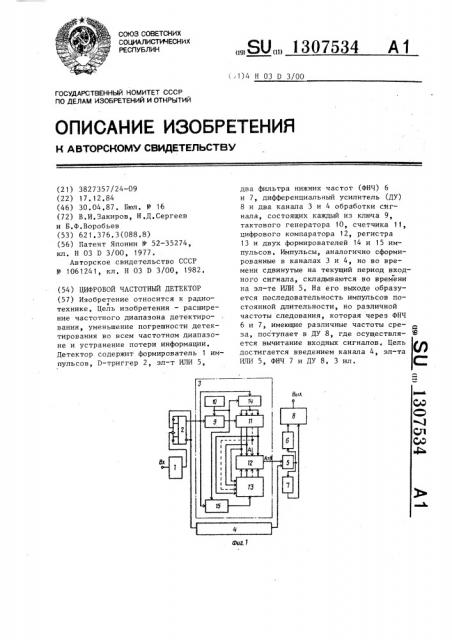

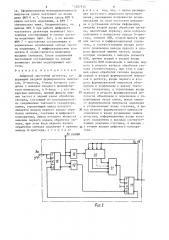

На фиг. 1 приведена структурная электрическая схема цифрового частотного детектора, на фиг, 2 — структурная электрическая схема формирователей импульсов, на фиг. 3 — временные 15 диаграммы, поясняющие работу цифрового частотного детектора, где a — входное напряжение, б — напряжение на выходе входного формирователя, в — напряжение на прямом выходе Э-триггера, 20

r — напряжение на выходе второго формирователя импульсов первого канала. обработки сигнала, д — напряжение на выходе первого формирователя импульсов первого канала обработки сиг- 5 нала, е — напряжение на выходе ключа первого канала обработки сигнала, ж— число импульсов, записанное в память регистра первого канала обработки сигнала, з — напряжение на выходе цифро- ЗО вого компаратора первого канала обработки сигнала, и — напряжение на инверсном выходе D-триггера, к — напряжение на выходе ключа второго канала обработки сигнала, л — напряжение на выходе цифрового компаратора второго канала обработки сигнала, м— напряжение на выходе элемента MJIR,, н — напряжение на выходе первого фильтра нижних частот, о — напрАже- 40 ние на выходе второго фильтра нижних частот, п — напряжение на выходе дифференциального усилителя, Цифровой частотный детектор содержит входной формирователь 1 импульсов,45

D-триггер 2, первый канал 3 обработки сигнала, второй канал 4 обработки сигнала, элемент ИЛИ 5, первый фильтр нижних частот (ФНЧ) 6, второй фильтр нижних частот (ФНЧ) 7, дифференциаль- 5g ный усилитель 8, При этом первый и второй каналы 3 и 4 обработки сигнала содержат ключ 9, тактовый генератор 10,счетчик 11, цифровой юмпаратор 12, регистр 13, первый формирова- 55 тель 14 импульсов, второй формиров,ртель 15 импульсов, кроме того, каждый формирователь 14 и 15 импульсов (фиг. 2) содержит первый и второй IK34 2 триггеры 1б и 17, первый и второй элементы И 18 и 19, счетчик 20 и элемент И-HE 21.

Цифровой частотный детектор работает следующим образом, Рассмотрим, например, интервал времени, в течение которого модулирующая функция изменяется от наибольшего положительного значения до наименьшего отрицательного, что соответствует уменьшению частоты входного сигнала (фиг. 3a), В моменты перехода входного сигнала из плюса в минус на выходе входного формирователя

1 образуются короткие импульсы положительной полярности (фиг, Зб), частота следования которых делится на два с помощью D-триггера 2, На выходах D-триггера 2 образуются противофазные импульсы, длительность которых равна периоду несущей частоты (фиг,Зв и Зи), Рассмотрим работу первого канала

3, второй канал 4 работает аналогичным образом, но со сдвигом во времени на период входного сигнала, Под действием импульса, поступающего с Dтриггера 2, на выходе ключа 9 образуется последовательность прямоугольных импульсов тактовой частоты, поступающих с тактового генератора tO (фиг,2е).

Длительность этой последовательности равна периоду входного сигнала. Число импульсов в последовательности равно отношению частоты тактового генератора 10 к текущему значению частоты входного сигнала, Счетчик 11 осуществляет счет импульсов последовательности. Состояния триггеров счетчика

11 определяют значения потенциалов на первых входах цифрового компаратора

12. Эти же значения потенциалов устанавливаются на информационных входах регистра 13, используемого в качестве элемента памяти, Информация с регистра 13 поступает на вторые входы цифрового компаратора 12, По окончании счета под действием импульса 113апись" (фиг, Зг), возникающего на выходе формирователя I5, осуществляется параллельный прием информации со счетчика 11 в регистр 13, После этого под действием импульса "Сброс", поступающего с выхода формирователя 14 (фиг, Зд), осуществляется обнуление счетчика 11, Импульсы "Запись" и "Сброс" формируются по заднему фронту сигналов, поступающих с прямого выхода Dтриггера 2. Эти импульсы разделены

1307534 4 ва времени, их длительность равна периоду тактовой частоты.

Сигнал с выхода D-триггера 2 поступает на объединенные 3, С-входы

JK-триггера 16 и переводит его в состояние логической "1" по прямому ..ыходу. К-входы JK-триггера 16 и JKтриггера 17 подключены к шине нулевого потенциала ° При этом сигнал тактовой частоты через открытый элемент

И 18 поступает на счетный вход счетчика 20. Через заданное время с на информационных выходах счетчика

20 возникают сигналы логической "1", при этом на выходе элемента И-.НЕ 21 15 возникает переход напряжения от логической "1" до логического "0", переводящий JK-триггер 17 в состояние логической " 1" по прямому выходу. При этом счет прекращается, счетчик 20 Zp обнуляется, а сигнал логического "0", возникающий на инверсном выходе JKтриггера 17, объединенным с R-входом

JK — триггера 16, переводит последний в исходное состояние. Сигнал логичес- 25 кой "1" на инверсном выходе JK-триггера 16 открывает элемент И 19, через который первый же импульс тактовой частоты, поступающий íà R-вход 3Ктриггера 17 переводит последний в ис- 30 ходное состояние, Одиночный импульс, длительность которого равна периоду тактовой частоты, задержанный на время t относительно заднего фронта

Зад 1 импульса, поступающего с выхода Dтриггера 2, снимается с прямого выхода JK-триггера 17. Разница в работе формирователей 14 и 15 заключается в различных задержках формируемых импульсов t z y с „„ . Это достига- 40 ется тем, что в формирователях 14 и

15 используются разряды соответствующих счетчиков.

Цифровой компаратор 12 осуществляет непрерывное сравнение чисел им- 45 пульсов, поступаюших со счетчика 11 и регистра 13, Допустим, что на счетный вход счетчика 11 последовательно поступает 100 импульсов. Время, в те- чение которого поступают импульсы, 50 соответствует текущему значению пери-. ода входного сигнала, допустим N-му периоду. Во время работы счетчика 11 в N-ом периоде входного сигнала в па мяти регистра 13 хранится число, соот55 ветствующее количеству импульсов,подсчитанных счетчиком 11 в предыдущем

N-1периоде входного сигнала, Так как ер д короч записанное в память регистра !3, будет меньше числа 100 (число А), которое счетчику 11 предстоит подсчитать, Пусть в памяти регистра 13 хранится число 90 (число В), На фиг, Зж это число условно изображено в виде последовательности импульсов. От момента времени, соответствующего переднему фронту импульса "Запись, возникшего в N-1 периоде входного сигнала, до момента времени, соответствующего подсчету 91-го текущего импульса N-го периода, на выходе цифрового компаратора 12 образуется уровень логического "0", а от момента подсчета 91-го импульса в N-ом периоде входного сигнала до момента времени, соответствующего переднему фронту импульса "Запись", возникшего в том же периоде сигнала, на выходе цифрового компаратора 12 возникает уровень логической

" 1", Таким образом, на выходе А ) В цифрового компаратора 12 возникает импульс положительной полярности, длительность которого равна разности текущего и предыдущего периодов входного сигнала (фиг, Зз). При постоянных значениях тактовой частоты и средней частоты входного сигнала длительность этих импульсов будет однозначно определяться глубиной модуляции, т,е отношением девиации частоты к несущей, При линейном законе модуляции длительность этих импульсов будет постоянной.

Аналогичные импульсы возникают на выходе второго канала 4, но во времени они будут сдвинуты на текущий период входного сигнала (фиг. Зл). Элемент

ИЛИ 15 осуществляет сложение во времени выходных импульсов каналов 3 и

4. Таким образом, на выходе элемента

ИЛИ 5 образуется последовательность импульсов постоянной длительности, но различной частоты следования (фиг. Зм). Следует отметить, что при отсутствии модуляции последовательность импульсов не возникает вследствие равенства всех периодов входного сигнала. Следовательно, будет отсутствовать постоянная составляющая, являющаяся ложной информацией, Кроме того, при изменении среднего значения несущей частоты пропорционально изменяется длительность импульсов на выходе элемента ИЛИ 5, но скважность импульсов за счет изменения среднего значения несущей частоты не изменяет1307534 ся. Сформированная последовательность импульсов далее поступает на входы двух ФНЧ 6 и 7, Частота среза ФНЧ 6 равна частоте модуляции, а ФНЧ 7 значительно ниже, Следовательно, на выходе ФНЧ 6 при работе цифрового частотного детектора возникает постоянная составляющая и сигнал частоты модуляции (фиг. Зн), а на выходе

ФНЧ 7 -- постоянная составляющая и 10 значительно ослабленный сигнал частоты модуляции. В дифференциальном усилителе 8 осуществляется вычитание входных сигналов. После подавления постоянной составляющей на выходе 15 возникает сигнал модулирующей частоты.

Формул а изобретения

Цифровой частотный детектор, со- 20 держащий входной формирователь импульсов, D-триггер, С-вход которого соединен с выходом входного формирователя импульсов, а D-вход — с его инверсным выходом, первый фильтр ниж- 25 них частот и первый канал обработки сигнала, состоящий из последовательно соединенных тактового генератора, ключа, управляющий выход которого является входом первого канала обра- 30 ботки сигнала, счетчика и цифрового компаратора, выход которого является выходом первого канала обработки сигнала, при этом вход первого канала обработки сигнала подключен к прямому З5 выходу D — триггера, о т л и ч а юшийся тем, что, с целью расширения частотного диапазона детектирования, уменьшения погрешности детектирования во всем частотном диапазоне и устранения потери информации, введены второй канал обработки сигнала, идентичный первому, вход которого подключен к инверсному выходу D-триггера, элемент ИЛИ, второй фильтр нижних частот и дифференциальный усилитель, к соответствуЮщим входам которого подключены выходы первого и второго фильтров нижних частот, входы которых соединены с выходом элемента

ИЛИ, причем первый и второй входы элемента ИЛИ подключены к выходам первого и второго каналов обработки сигнала соответственно, при этом в каждый канал обработки сигнала введены первый и второй формирователи импульсов и регистр, входы первого и второго формирователей импульсов объединены и подключены к выходу тактового генератора, а управляющие входы первого и второго формирователей импульсов объединены и подключены к управляющему входу ключа, выход первог0 формирователя импульсов подключен к установочному входу счетчика, а выход второго формирователя импульсов подключен к входу разрешения записи регистра, информационные входы которого подключены к выходам соответствующих разрядов счетчика, а выходы— к вторым входам цифрового компаратора.

1307534

Н о о

Составитель Г. Каракозов

Техред М.Ходанич Корректор Н.Король

Редактор А.Долинич

Тираж 902

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Заказ 1640/53

Подписное

Производственно-полиграфическое предприятие, r.Óæãoðoä, ул.Проектная, 4