Устройство для объединения кореллированных импульсных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной техникеу и может быть использовано при передаче по общему импульсфВыход суммы Выход переноса Г- ному каналу связи аналоговой информации от нескольких абонентов. Цель изобретения - повьшение помехозащищенности . Для достижения поставленной цели в устройство введены элементы 3,4 задержки, элементы 5,6,7, совпадения, элемент ИЛИ 9. Устройство также содержит одноразрядный двоичный сумматор 1, триггер 2 памяти и элемент ИЛИ 8. Повьшение помехозащищенности обеспечивается уменьшением искажения входных сигналов за счет обеспечения возможности их расфазировки и повьшения надежности. 1 ил. (Л Ц LT | СЛ со

СОЮЗ СОВЕТСКИХ

СОЯ4АЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 Н 03 М 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3547537/24-21 (22) 26.01.83 (46) 30,04.87. Бюл. № 16 (72) М.Д, Венедиктов, Б.Ш. Златкин, В.И. Механошина и А.В. Иытаркин (53) 621.374(088.8) (56) Авторское свидетельство СССР

¹ 476682, кл. Н 03 M 3/00, 1972. (54) УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ КОРРЕЛИРОВАННЫХ ИМПУЛЬСНЫХ СИГНАЛОВ (57) Изобретение относится к импульсной технике и может быть использовано при передаче по общему импульсному каналу связи аналоговой информации от нескольких абонентов. Цель изобретения — повышение помехозащищенности. Для достижения поставленной цели в устройство введены элементы 3,4 задержки, элементы 5,6,7, совпадения, элемент ИЛИ 9. Устройство также содержит одноразрядный двоичный сумматор 1, триггер 2 памяти и элемент ИЛИ 8. Повышение помехозащищенности обеспечивается уменьшением искажения входных сигналов за счет обеспечения возможности их расфазировки и повышения надежности. 1 ил.

1307592

Изобретение относится к импульсной технике и может быть использовано при передаче по общему импульсному каналу связи аналоговой информации от нескольких абонентов. 5

Цель изобретения — повышение помехозащищенности путем уменьшения искажений входных сигналов за счет обеспечения и возможности их расфазировки и повышение надежности работы устройства.

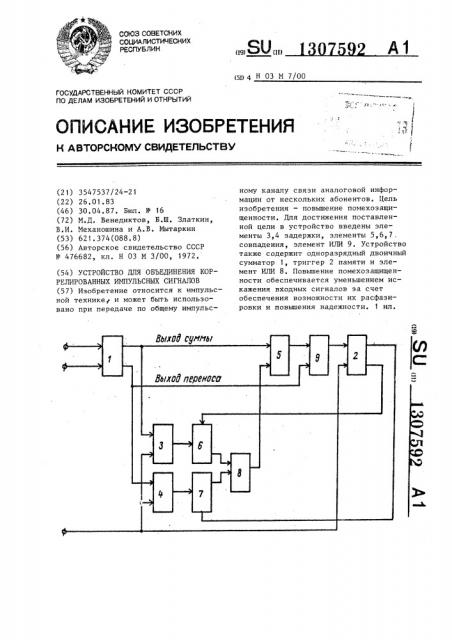

На чертеже представлена функциональная схема устройства для объединения коррелированных импульсных сигналов.

Устройство для объединения коррелированных импульсных сигналов содержит одноразрядный двоичный -сумматор

1 и триггер 2 памяти ° Выход суммы одноразрядного двоичного сумматора соединен с входом элемента 3 задержки, а выход переноса подключен к входу элемента 4 задержки, Кроме того, выход суммы одноразрядного двоич25 ного сумматора 1 подключен к одному из вхоцов элемента 5 совпадения.

Выход элемента 3 задержки и инверсный выход триггера 2 памяти подключены к входам элемента 6 совпадения, а выход элемента 4 и прямой выход триггера 2 памяти подключены к входам элемента 7 совпадения, Выходы элементов 6 и 7 совпадения через элемент ИЛИ 8 подключены к второму входу элемента 5 совпадения, выход кото- 35 рого и выход переноса одноразрядного двоичного сумматора 1 подключены к информационному входу триггера 2 памяти через элемент KlH 9.

Устройство работает следующим об- 40 разом.

При совпадении символов "1" в объединяемых сигналах на выходе переноса одноразрядного двоичного сумматора 1 возникает импульс. Этот импульс про- 45 ходит через элемент ИЛИ 9 на информационный вход триггера 2 памяти и независимо от состояния триггера 2 памяти в предыдущий момент времени устанавливает его в единичное состоя- 50 ние.

Таким образом, если в объединяемых сигналах в данном такте имеется одновременно символ "1", то на выходе устройства формируется символ "1".

При совпадении символов "0" в объединяемых сигналах на выходах суммы и переноса одноразрядного двоичного сумматора импульсы не образуются, На информационный вход триггера 2 памяти импульс не поступает, и независимо от предыдущего состояния триггер устанавливается в нулевое состояние.

Таким образом, при совпадении символов "0" на выходе устройства импульс отсутствует, Если в одном из объединяемых сигналов возникает символ "1", а в другом — символ "0", то на выходе переноса одноразрядного двоичного сумматора 1 импульс отсутствует, а на выходе суммы возникает импульс, Если в предыдущем такте совпадали символы

"1", то на выходе триггера 2 памяти, а также на выходе элементов 3 и 4 задержки на такт возникают импульсы.

Эти импульсы проходят через элементы

6 и 7 совпадения и элемент ИЛИ 8 на элемент 5 совпадения. С выхода элемента 5 совпадения через элемент

ИЛИ 9 импульс поступает на информационный вход триггера памяти и поддерживает его в единичном состоянии.

Если в предыдущем такте в объединяемых сигналах совпадали символы

"0", то на выходе триггера 2 памяти импульс отсутствует. Отсутствуют импульсы также на выходах элементов 3 и 4 задержки на такт, элементов 6 и 7 совпадения, элемента ИЛИ 8, элемента

5 совпадения и элемента ИЛИ 9. Поэтому на информационном входе триггера

2 памяти импульс отсутствует и триггер остается в нулевом состоянии.

Если в предыдущем такте в объединяемых сигналах совпадали символы "1" и "0", то на выходе элемента 3 задержки формируется импульс, а на выходе элемента 4 импульс отсутствует °

Если триггер 2 памяти в предыдущем такте находился в единичном состоянии, то на выходах элементов 6 и 7 совпадения, элемента ИЛИ 8, элемента

5 совпадения и элемента ИЛИ 9 импульс отсутствует и триггер 2 памяти переходит в нулевое состояние. !

Если в предыдущем такте триггер 2 памяти находился в нулевом состоянии, то на выходе элемента. 6 совпадения формируется импульс ° Этот импульс проходит через элемент ИЛИ 8, элемент

5 совпадения и элемент ИЛИ 9 на информационный вход триггера 2 памяти и устанавливает его в единичное состояние.

1307592

Составитель О. Ханджян

Техред М. Ходанич Корректор Л. Пилипенко

Редактор А. Огар

Подписное

Заказ 1641/55 Тираж 902

ВНИИПИ Государственного комитета. СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Поэтому если в одном из суммируемых сигналов возникает символ "1", а в другом — символ "0", выходной сигнал устройства представляет собой чередующуюся последовательность символов "1" и "0" ° Память на один такт осуществляется триггером 2 памяти и элементами 3 и 4 задержки.

Формула из обретения 10

Устройство для объединения корре-. лированных импульсных сигналов, содержащее одноразрядный двоичный сумматор, к входам которого подключены первая и вторая входные шины соответственно, первый элемент ИЛИ, триггер памяти и шина тактовой частоты, о т" л и ч а ю щ е е с я тем, что, с целью повьш ения помехозащищенности и 20 повышения надежности работы, в него дополнительно введены два элемента задержки, три элемента совпадения, второй элемент ИЛИ, причем выходы суммы и переноса одноразрядного двоичного сумматора через первый и второй элементы задержки соединены соответственно с первыми входами первого и второго элементов совпадения, к вторым входам которых подключены соответственно прямой и инверсный выходы триггера памяти, входы управления первого и второго элементов задержки подключены к шине тактовой частоты, выходы первого и второго элементов совпадения через первый элемент ИЛИ подключены к первому входу третьего элемента совпадения, Ъ второй вход которого подключен к выходу суммы одноразрядного двоичного сумматора, выход третьего элемента совпадения и выход переноса одноразрядного двоичного сумматора соединены с входами второго элемента ИЛИ, выход которого подключен к управляющему входу триггера памяти, вход синхронизации которого соединен с шиной тактовой частоты.