Устройство сопряжения процессора с арифметическим расширителем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки информации для подключения арифметического расширителя или других внешних устройств типа вычислителя элементарных функций, функционального преобразователя и является усовершенствованием устройства по а.с. № 1182529. Целью изобретения является сокращение непроизводительных затрат времени за счет исключения пустых команд, необходимых для временного согласования работы функционального раширителя и ЭВМ. Это достигается введением в устройство схемы прерываний , содержащей второй элемент И 14, третий элемент ИЛИ 15, формироватрль .импульса готовности (одно . :, вибратор) 12, триггер 8 прерывания и шифратор 16 вектора прерывания. Предложенное решение позволяет полезно использовать время процессора . на интервале времени работы функционального распшрителя. 3 ил. (Л а 14) lrt.r

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 G 06 F 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ. (61) 1182529 (21) 3985177/24-24 (22) 05. 12 ° 85 (46) 07.05.87. Бюл. Ф 17 ,(72) А.Д.Брагин, А.Н.Каменков, Л.И.Коняхина и С.Д.Бороненко (53) 68 1.327. 11(088.8) (56) Авторское свидетельство СССР

В 1182529, кл. G 06 F 13/00, 1984. (54) УСТРОЙСТВО СОПРЯЖЕНИЯ ПРОЦЕССОРА С АРИФМЕТИЧЕСКИМ РАСШИРИТЕЛЕМ (57) Изобретение относится к вычислительной технике-и может быть использовано в устройствах обработки информации для подключения арифметического расширителя или других внешних устройств типа вычислителя элементарных функций, функционального

„„SU„„1 09031 А2 преобразователя и является усовершенствованием устройства lI0 а.с.

9 1182529. целью изобретения является сокращение непроизводительных затрат времени за счет исключения "пустых" команд, необходимых для временного согласования работы функционального раширителя и 3ВМ. Это достигается введением в устройство схемы прерываний, содержащей второй элемент

И 14, третий элемент ИЛИ 15 формироват ль .импульса готовности (одновибратор) 12, триггер 8 прерывания и шифратор 16 вектора прерывания.

Предложенное решение позволяет по- лезно использовать время процессора ф на интервале времени работы функционального расширителя. 3 ил, 1 13090

Изобретение относится к вычислительной технике и может быть использовано в устройствах обработки инфор-, мдции для сопряжения процессора элект-. ронно-вычислительной машины (ЭВИ) с 5 арифметическим (функциональным) расширителем (ФР), в качестве которого могут применяться, например, устройства вычисления элементарных функций, устройства комплексного быстрого 10 преобразования Фурье (БПФ) и другие функциональные преобразователи, и является усовершенствованием устройства по авт. св. N 1182529.

Цель изобретения — сокращение непроизводительных затрат времени.

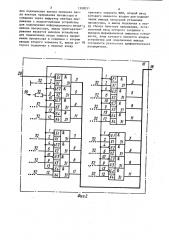

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 шифратор вектора прерывания; на фиг. 3 — временная диаграмма работы устройства.

Устройство содержит (фиг ° 1) магистральный приемопередатчик 1, второй элемент ИЛИ 2, первый элемент И 3, блок 4 памяти, триггер 5, триггеры 6

25 и 7 первой и второй групп, триггер 8 прерывания, одновибратор 9, одновибратоты 10 и 11 первой и второй групп, формирователь 12 импульса готовности (одновибратор), первый элемент ИЛИ

13, второй элемент И 14, третий элемент ИЛИ 15, шифратор 16 вектора прерывания, информационные вход 17, вход-выход 18 и выход 19 устройства, выход 20 записи микрокоманды, группы 35 выходов 2 1 и 22 записи и считывания операндов, вход 23 начальной установки, вход 24 признака адреса данных, входы 25 и 26 признаков вывода и ввода, выход 27 начальной установки, 40 входы 28 и 29 признаков готовности результата и ввода вектора прерывания, выход 30 запроса прерывания устройства.

Шифратор . 16 содержит (фиг. 2) 45 группу элементов И 31 и группу монтажных перемычек 32.

Устройство работает следующим образом.

При обмене информацией с информационного входа-выхода 18 через приемопередатчик 1 на адресный вход блока 4 поступают адреса ячеек, в которых записан позиционный двоичный код признаков для формирования сигналов записи-считывания, поступивших на выходы 20-22. По управляющему сигналу признака адреса данных с входа 24

3 1 2 двоичный код из блока 4 поступает в триггеры 5 — 7. В каждый такой момент в один из триггеров 5 — - 7 может быть записана логическая "1", являющаяся разрешением срабатывания одновибраторов 9 — 11 при приходе с входов 26 и 25 управляющих сигналов признаков ввода (вывода) данных. После загрузки последнего операнда в ФР производится загрузка микрокоманды (инструкции), после чего ФР выставляет на вход 28 сигнал "0", означающий состояние ожидания результата. Через неко.торое время в ФР завершается формирование результата и сигнал на входе 28 становится активным (логическая " 1"), поданному перепаду запускается одновибратор 12; формирующий сигнал установки триггера 8 в состояние " 1". По этому сигналу формируется сигнал требования прерывания на выходе 30, поступающий в процессор, который реагирует на этот сигнал (логическая " 1"), выполняя команды спасения состояния прерываемого процесса.

Затем процессор производит считывание вектора прерывания из устройства. Для этого на вход 29 подается сигнал чтения шифратора 16, на котором при помощи монтажных перемычек 32 на входах элементов И 31 задаются логические "0" и "1" кода вектор-адреса путем стандартного подсоединения разрядов информационного входа к шинам источника питания устройства ОВ или

+5B. Код вектора через информационный вход-выход 18 считывается процессором.

Затем осуществляется считывание результата. Приемопередатчик 1 переключается на вывод информации сигналами считывания операндов. Триггер 8 устанавливается в "i по окончании вычислений в ФР и сбрасывается в "0" считыванием вектора или сигналом сброса.

Формула изобретения

Устройство сопряжения процессора с арифметическим расширителем по авт, св. N- 1182529, о т л и ч а ющ е е с я тем, что, с целью сокращения непроизводительных затрат времени, в устройство введены шифратор вектора прерывания, триггер прерывания, формирователь импульса готовности, второй элемент И и третий элемент

ИЛИ, причем первый вход второго элемента И является входом устройства130903 для подключения выхода признака ввода вектора прерывания процессора и соединен через шифратор вектора прерывания с входом-выходом устройства для подключения информационного входа-5 выхода процессора, выход триггерапрерывания является выходом устройства для подключения входа запроса прерывания процессора и соединен с вторым входом второго элемента И, выход ко- ®О торого подключен к первому входу

1 ф третьего элемента ИЛИ, второй вход которого является входом для -подключения выхода начальной установки процессора, а выход подключен к входу сброса триггера прерывания, установочный вход которого соединен с выходом формирователя импульса готовности, вход которого является входом устройства для подключения выхода. готовности результата арифметического расширителя.

Фиг.2

1309031

ВВод

Выоод загрузка загрузка

Иод оекпюр- Чтенае

ЯА ((8) lA (24) Выдод (2Я

Вдод (2б) Иод оектора(2

Вых.Тр. (б)

3an.! операн

Вых. ОВ((О) запЛ/опера

Вых. Тр. (6) зап. 2 oneð÷

Bow. 0B (10) зап 2.опер

Вых. Тр, (з) зап. MK

Вых. OB(9) зап. ИК

Вых. Тр. (7) Вых. ОВ ((Готоо (2

Вых. ПП( рабаты- Время захоата бание ФР прерывания о 9В/7

ФагЗ

Составитель В, Вертлиб

Редактор Н.Тупица Техред М.Ходанич Корректор А.Зимокосов

Заказ 1800/42 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная, 4