Перемножитель сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к электрическим вьиислительным устройствам и может быть использовано в аналоговых вьгаислительных машинах. Целью изобретения является повышение точности работы. Перемножитель сигналов содержит сумматор 3, первый, второй, третий , четвертый, пятый, шестой, седьмой и восьмой четырехпозиционные коммутаторы 4-9, 11, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой квадраторы 12-19, первый и второй дополнительные сум (Л со о со о NU 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (192 (И) (594 G06G 7 6

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

К А ИТОРСКОИМ СВИДЕТЕЛЬСТВУ

4иа.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3955794/24-24

{22) 25. 09. 85 (46) 07.05.87. Бюл. К- 17 (71) Специальное конструкторско-технологическое бюро Физико-механического института им. Г.В.Карпенко (72) А.М.Брискин, Е.И.Клим и А.С.Родин (53) 681. 335 (088 8) (56) Алексеенко А.Г. и др. Применение прецизионных аналоговых ИС. И.: Радио и связь, 1981, с. 99, рис. 3.21;

Авторское свидетельство СССР

Ф 1103244, кл. G 06 G 7/16, 1983. (54) ПЕРЕМНОЖИТЕЛЬ СИГНАЛОВ (57) Изобретение относится к электри- . ческим вычислительным устройствам и

1 может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности работы. Перемножитель сигналов содержит сумматор 3, первый, второй, третий, четвертый, пятый, шестой, седьмой н восьмой четырехпозиционные коммутаторы 4-9, 11, первый, второй, тргтий, четвертый, пятый, шестой, седьмой и восьмой квадраторы 12-19, первый и второй дополнительные сум1309048 маторы 20 и 21, блок 22 вычитания, ния. Перемножитель сигналов характесинхронный детектор 23, фильтр 24 ризуется повышенной точностью работы . нижних частот, делитель 25 частоты, за счет снижения аддитивной погрешгенератор 26 коммутирующего напряже- ности. 2 ил.

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является иовы- 5 шение точности работы.

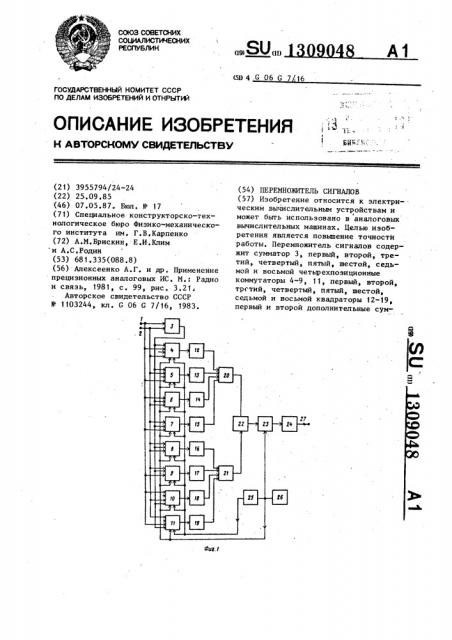

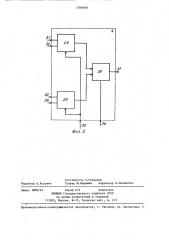

На. фиг. 1 изображена функциональная схема перемножителя сигналов, на фиг. 2 — функциональная схема четырехпозиционного коммутатора, вариант.

Устройство включает входы первого и второго сигналов-сомножителей 1 и 2, сумматор 3, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой четырехпозиционные

15 коммутаторы 4-11, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой квадраторы 12-19, первый и второй дополнительные сумматоры 20 и 21, блок 22 вычитания, синхронный детектор 23, фильтр 24 нижних частот, делитель 25 частоты, генератор 26 коммутирующего напряжения, выход 27, первый, второй и третий переключатели 28-30, первый, агорой, третий и четвертый информационные входы 31-34, первый и второй управляющие входы 35 и 36 и выход 37.

Перемножитель сигналов работает следующим образом, 30

С первого и второго входов 1 и 2 сигналы-сомножители и их сумма с выхода сумматора 3 периодически с частотой коммутации через первыи, второй, третий, четвертый, пятый, шестой35 седьмой и восьмой четырехпозиционные коммутаторы 4-11 поступают на первый, второй, третий н четвертый квадраторы 12-15. Выходные напряжения этих квадраторов суммируются в первом дополнительном сумматоре 20. Выходные сигналы пятого, шестого, седьмого и восьмого квадраторов 16-19 суммируются во втором дополнительном сумматоре 21. 45 . Погрешности всех квадраторов имеют случайный характер, а величину этих погрешностей можно положить равной по абсолютной величине. В блоке

22 вычитания полезный сигнал суммируется, а составляющие аддитивной погрешности вычитаются. С учетом их случайного характера выходной сигнал синхроннorо детектора имеет вид

V = K(liU,О +.12 3„, (U, + U

+ П,П )Sgnsin2gt + „(U +

+ U ) (Sgnsingt + Sgncosgt), где К вЂ” коэффициент пропорциональности, U U — первый и второй сигналы-сом н ожнт ели,"

8„ — модуль среднеквадратичной погрешности квадраторов;

Ю вЂ” частота коммутации.

Проведем нормирование напряжения на выходе синхронного детектора 23 по коэффициенту передачи при полезном сигнале — произведении первого и второго сигналов-сомножителей. Для этого положим один из сигналов-сомножителей, например второй, равный нулю, и определим соотношение составляющих адцитивной погрешности на частотах коммутации. Учитывая, что на выходе включен фильтр 24 нижних частот, а большая из составляющих погрешности имеет более высокую частоту, можно считать, что в предлагаемом неремножителе сигналов аддитивная погрешность меньше, чем в известном в 4/8„ь.раз.

Формула изобретения

Перемножитель сигналов, содержащий сумматор, первый и второй входы которого являются входами соответственно первого и второго сигналов-сомножителей перемножителя, первый четырехпозиционный коммутатор, первый информационный вход которого соединен з 1309048 4 ,с выходом сумматора, первый и второй рым информационным входом третьего, входы сумматора соединены соответст- с первыми информационными входами пявенно с вторым и четвертым информа- того и седьмого и с третьими информационными входами первого четырехпо- ционными входами шестого и восьмого зиционного коммутатора, выход кото- 5 четырехпозиционных коммутаторов, четрого подключен к входу первого квад- вертый информационный вход первого

I ратора, синхронный детектор, выход четырехпозиционного коммутатора соекоторого соединен с входом фильтра динен с вторыми информационными вхонижних частот, выход которого являет- дами второго и четвертого, с третьися выходом перемножителя, генератор 10 ми информационнььл входами пятого и коммутирующего напряжения, выход ко- седьмого, с первыми информационными торого подключен к входу делителя входами шестого и восьмого и с четчастоты, к управляющему входу синх- вертым информационным входом третьеронного детектора и к первому управ- го четырехпозиционных коммутаторов, ляющему входу первого четырехпозици- 15 выходы второго, третьего и четвертого онного коммутатора, второй управляю- четырехпозиционных коммутаторов подщий вход которого соединен с выходом ключены к входам второго, третьего делителя частоты, о т л и ч а ю— и четвертого квадраторов, выходы кошийся тем, что, с целью повыше- торых соединены с соответствующими ния точности, в него введены второй, 20,âõîäàìè первого дополнительного сумтретий, четвертый, пятый, шестой, матора, выход которого подключен к седьмой и восьмой четырехпозиционные пеРвомУ вхоДУ блока вычитаниЯ, выхоД коммутаторы, второй, третий, четвер- которого соединен с входом синхронтый, пятый, шестой, седьмой и вось- ного детектора, выходы пятого, шесмой квадраторы, первый и второй до- 25 того, седьмого и восьмого четырехпо полнительные сумматоры и блок вычи- зиционных коммутаторов соответствентания, причем к первому информацион- но через пятый, шестой, седьмой и ному входу первого четырехпозиционно- восьмой квадраторы подключены к вхого коммутатора подключены первый ин- дам второго дополнительного сумматоформационный вход второго, третьи 3О ра, выход которого соединен с вторым информационные входы третьего и чет- входом блока вычитания, первый и вертого, вторые информационные входы второй управляющие входы первого чепятого и шестого и четвертые информа- тырехпозиционного коммутатора соедиционные входы седьмого и восьмого че- иены соответственно с первыми и тырехпозиционных коммутаторов, вто- 35 вторымй управляющими входами второй информационный вход первого че- рого, третьего, четвертого, пятырехпозиционного коммутатора соеди- того, шестого, . седьмого и восьнен с четвертыми информационными мого четырехпоэиционных коммутавходами второго и четвертого, с вто- торов. (1309048

Составитель 0.0трацнов

Техред М.Кодаиич Корректор Л.Пилипенко

Редактор А.Ворович

Тираж б73 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Заказ 1800(42

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4