Устройство для сжатия и развертывания информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может использоваться в системах .хранения, поиска и обработки информации . Изобретение позволяет повысить информативность устройства, которое осуществляет побайтное сжатие и развертывание данных, представленных в двоичнодесятичном коде, и содержит регистры 1,2, дешифраторы 3-6, преобразователи 7,8, 16,17 кода, элемепты ИЛИ 9,23-25,30,31, элемент 10 запрета, мультиплексоры 11,12, 22, блок 13 управления, счетчики 14,15 и элементы И 18-21,26-29. Де1пифраторы 3,4 выполнены па элементе 2И - ИЛИ. Де шифраторы 5,6 выполнены на элементе ЗИ-- ИЛИ: Преобразователи 7,8 кода выполнены на элементах И и элементах ИЛИ. Прр образователи 16,17 кода выполнены на элементах И, элементе ИЛИ а сумматорах по модулю два. Блок 13 управления содержит э, 1ементы ИЛИ, три1теры, деп ифраторы, генератор тактовых импульсов и элементы И. Применение изобретения в системах обработки данных способствует экономии объема па.мяти, требуемой для хранения десятичных данных, и экономии времени об.мепа данными. 1 з.п. ф-лы. 7 ил. 2 табл. (Л со о со о о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я) 4 G 08 С 15, 06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ; .д

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ M.:. .: (21 ) 4034505 24-24 (22) 20.01.86 (46) 07.05.87. Бюл ¹ 17 (71) Азербайлжанский полите«нический институт им. Ч. Ильдрыма (72) T. М. Аскеров, Ш. Ш. Гахраманов, Э. Б. Алиев и М. М. Дамадаев (53) 621.398 (088.8) (56) Авторское свидетельство СССР

¹ 613320, кл. G 06 F 7(00, 1973.

Авторское свидетельство СССР № 991471, кл. G 08 С 15/06, G 06 F 15/20.

1981. (54) УСТРОЙСТВО ДЛЯ СЖАТИЯ И

РАЗВЕРТЫВАНИЯ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может использоваться в системах хранения, поиска и обработки информации. Изобретение позволяет повысить информ ативность устройства, которое осуществляет побайтное сжатие и развертыва„„Я0„„1309070 А 1 нис данных, прсдставлснны«в двоичнодесятичном коде, и содержит регистры 1,2, деп ифраторы 3 — 6, преобразователи 7,8, 16 17 кода, элементы ИЛИ 9 23 25,30,3(, элемент (О запрета, мультиплексорь1 I i, 12, 22, блок 13 управления. счетчики 14,15 и элементы И 18 — 2 I.26 — 29. Деш ифраторы

3,4 выполнены на элементе 2И- ИЛИ. Де= шифраторы 5,6 выполнены на элементе ЗИ-—

ИЛИ. Преобразователи 7,8 кода вьп1олнсны на элемента«И и элементах ИЛИ. Про= обpазоватсли 16,17 кода выполнены на элемента«И. элементе ИЛИ и сумматорах по модулю два. Блок 13 управления содержит элементы ИЛИ, триггеры, дсшифраторы, генератор тактовы«импульсов и элементы

И. Применение изооретения в системах обработки данны«способствует эконом ии объема памяти, требуемой для хранения десятичны«данны«, и экономии времени обмена данными. I з.п. ф — лы. 7 ил. 2 табл

1309070

Изобретение относится к вычислительной технике и может использоваться в системах хранения, поиска и обработки информации.

Цель изобретения — повышение информативности устройства.

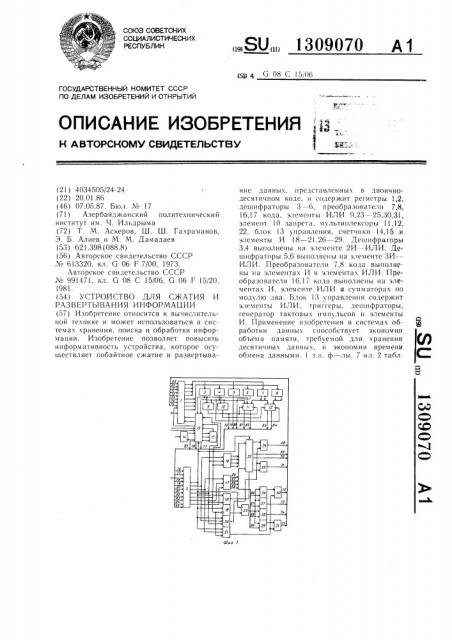

На фиг. 1 показана структурная схема устройства для сжатия и развертывания информации; на фиг. 2 и 3 — дешифраторы; на фиг. 4 и 5 — преобразователи кода; на фиг. 6 — функциональная схема блока управления; на фиг. 7 — дешифратор.

Устройство для сжатия и развертывания информации содержит (фиг. 1) первый регистр двоично-десятичного кода, второй регистр 2 сжатого кода, первый, третий, второй, четвертый дешифраторы 3 — 6 (распознаватели тетрад), первый, второй преобразователи 7 и 8 кода, первый элемент

ИЛИ 9, элемент ЗАПРЕТ 10, первый, второй мультиплексоры 11 и 12, блок 13 управления, первый, второй счетчики 14 и 15, третий, четвертый преобразователи 16 и 17 кода, первый — четвертый элементы И 18—

21, третий мультиплексор 22, четвертый шестой элементы ИЛИ 23 — 25, пятый восьмой элементы И 26 — 29 и второй, третий элементы ИЛИ 30 и 31.

Первый 3, третий 4 дешифраторы выполнены (фиг. 2) на элементе 2И вЂ” -ИЛИ 32, второй 5, четвертый 6 дешифраторы выполнены (фиг. 3) на элементе ЗИ вЂ” ИЛИ 33.

Первый 7, второй 8 преобразователи кода выполнены (фиг. 4) на элементах И 34 — 38 и элементах ИЛИ 39 и 40. Третий 16, четвертый 17 преобразователи кода выполнены (фиг. 5) на элементах И 41 — 44, элементе

ИЛИ 45 и сумматорах 46 и 47 по модулю два.

Блок 13 управления содержит (фиг. 6) первый элемент ИЛИ 48, первый, второй триггеры 49 и 50, первый дешифратор 51 (элемент ветвления), второй элемент ИЛИ, 52, генератор 53 тактовых импульсов, первый, второй элементы И 54 и 55, третий, четвертый элементы ИЛИ 56 и 57, второй дешифратор 58 (элемент ветвления), пятый, третий триггеры 59 и 60, третий дешифратор 61 (элемент ветвления), пятый элемент ИЛИ 62, четвертый триггер 63, четвертый и пятый дешифраторы 64 и 65.

Первый — пятый дешифраторы (элементы ветвления) выполнены (фиг. 7) на элементах И 66 и 67.

Устройство производит побайтное сжатие и развертывание данных, представленных в двоично-десятичном коде и в каждый момент времени может выполнить или сжатие или развертывание.

В режиме сжатия устройство работает следующим образом.

Перед началом сжатия код исходных данных вводится в регистр 1, а код длины данных — в счетчик 14 (фиг. 1). Разрешение сжатия осуществляется подачей единичного сигнала на нулевой вход триггера

59 (фиг. 6) блока 13 управления. Этот сигнал, устанавливая триггер 59 в ноль. проходит через элемент ИЛИ 48 и устанавлива5 ет триггер 49 в единичное состояние. Таким образом, блок 13 у правления подготавливается к сжатию содержимого первого байта регистра 1, к первой тетраде которого подключены (фиг. 1) распознаватели 3 и 5 и преобразователь 7, а к второй тетраде регистра 1 подключены распознаватели

4 и 6 и преобразователь 8. При этом, если значение первой тетрады регистра 1 равно нулк) или девяти, на выходе распознавателя 3 появляется единичный сигнал. Аналогично работает распознаватель 4 применительно к второй тетраде регистра 1.

Выходные сигналы распознавателей 3 и 4, логически складываясь элементом ИЛИ.

9, образуют первый разряд (Z,) сжато о

20 кода байта.

Если значение первой тетрады регистра

1 равно или больше пяти, на выходе распознавателя 5 возникает единичный сигнал.

Аналогично работает и распознаватель 6 применительно к второй тетраде регистра !.

Выходные сигналы распознавателей 5 и 6 образуют соответственно второй (Z, ) и третий (2 ) разряды сжатого кода байта.

Преобразователи 7 и 8 преобразуют содержимые первой и второй тетрады по

30 табл. г а б л и ц а 1

Код

Входной

0001

01

01

0111

0011

0101

Если на выходе хотя бы одного из распознавателей 3 и 4 возникает единичный сигнал, на выходе элемента ИЛИ 9 возникает единичный сигнал (т.е. 7,=1), который воздействуя на прямой управляющий вход

1309070

3 мультиплектора 11, вызывает соединение выходов распознавателей 3 и 4 с выходами этого мультиплексора 11. В противном случае возбуждается инверсный управляющий вход мультиплексора 11, что вызывает подключение его выходов к выходам преобразователя 7. Таким образом, формируются четвертый (Z ) и пятый (2,") разряды сжатого кода байта.

Если на выходе распознавателя 3 возникает нулевой, а на выходе распознавателя 4 — единичный сигнал, на выходе элемента ЗАПРЕТ 10 появляется единичный сигнал, который вызывает подключение выходов мультиплексора 12 к выходам преобразователя 7. Если же на выходе распознавателя 4 возникает нулевой сигнал, он возбуждает инверсный управляющий вход мультиплексора 12, что вызывает подключение его выходов к выходам преобразователя 8. Таким образом, формируется шестой (Z, ) и седьмой разряды сжатого кода байга. Очевидно, что все семь разрядов Z,, Z<, Z„Z,", Х;, Z„Z"„ñæàòîãî кода байта формируются одновременно, начиная с момента занесения кода в регистр 1.

Устройство остается в таком состоянии до перехода единицы из триггера 49 в триггер 50 (фиг. 6), что осуществляется первым (считая с момента установления триггера

49 в единичное состояние) тактовым сигналом от генератора 53.

Первый тактовый сигнал переводит единицу из триггера 49 в триггер 50, выход которого соединен с первыми входами дешифраторов 51 и 58 (элементов ветвления) и элементов И 54 и 55. Так как триггер 59 находится в нулевом состоянии, на выходе элемента И 66 дешифратора 51 (фиг. 7) возникает единичный сигнал, который синхронизирует первые семь входов регистра

2, что вызывает запись кода Z„, Z„, Z,, Z", Z, Z", Z," в первые семь разрядов регистра 2. Этот же сигнал, проходя через элемент ИЛИ 52 (фиг. 6), уменьшает содержимое счетчика 14 на единицу. Если на выходах распознавателей 3 и 4 имеются единичные сигналы, на выходе элемента И 54 (фиг. 6) блока 13 управления возникает единичный сигнал, который, проходя через элемент ИЛИ 57, устанавливает в счетчике

15 код <101». Если на выходе хотя бы одного из распознавателей 3 и 4 имеется нулевой сигнал, на выходе элемента 54 возникает нулевой сигнал, который, поступая на инверсный вход элемента ИЛИ 56, вызывает запись кода «111» в счетчик 15. Дешифратор 58 подключает через элемент И

66 вход триггера 60 к выходу триггера 50, если содержимое счетчика 14 не равно нулю, т.е. если сжимаемый байт не был последним. В противном случае на выходе элемента И 67 дешифратора 58 возникает

55 единичный сигнал, информирующий о конце процесса сжатия.

Если содержимое счетчика 14 нс равно нулю, необходимо выполнить подготовительную для сжатия следующего байта, работу.

Это осуществляется на следующих двух тактовых состояниях блока 13 управления.

Второй тактовый сигнал сдвигает единицу из триггера 50 через дешифратор 58 в триггер 60 (фиг. 6), который формирует единичныЙ сигнал на выходе элемента И

66 дешифратора 61. Этот сигнал сдвигает содержимое регистра 1 на один байт влево.

Третий тактовый сигнал сдвигает единицу из триггера 60 через элемент ИЛИ 62 в триггер 63, который своим выходным сигналом уменьшает содержимое счетчика 15 на единицу и возбуждает дешифраторы 64 и 65. Если триггер 59 находится в нулевом состоянии, единичный сигнал возникает на выходе элемента И 66 дешифратора 64.

Этот сигнал сдвигает содержимое регистра

2 на один разряд влево. Дешифратор 65 контролирует количество указанных сдвигов, так как его второй вход (вход условия) соединен с выходом счетчика 15. Пока содержимое счетчика 15 не обнулено, все следующие тактовые сигналы переводит единицу из триггера 63 через элемент И 66 дешифратора 65 и элемент ИЛИ 62 в тот же триггер 53, т.е. содержимое регистра 2 сдвигается влево ровно на столько разрядов, каково показание счетчика 15, указывающего длину сжатого байта. Обнуление счетчика !5 вызывает возникновение единичного сигнала на выходе элемента И 67 дешифратора 65, который через элемент

ИЛИ 48 устанавливает триггер 49 в единичное состояние.

Таким образом, устройство переходит в готовое для сжатия следующего байта состояние. Все остальные байты исходного кода сжимаются аналогичным образом.

В результате регистр 1 освобождается, а регистр 2 хранит сжатый код, который может быть извлечен из устройства.

B режиме развертывания устройство работает следующим образом.

В регистр 2 вводится код сжатых данных, а в счетчик 14 — длина этих данных в сжатых байтах. В таком состоянии устройство готово к развертыванию самого правого (на фиг. 1 самого нижнего) сжатого байта регистра 2. Подача сигнала на единичный вход триггера 59 (фиг. 6) вызывает установку через элемент ИЛИ 48 триггера 49 в единичное состояние. В этом состоянии преобразователь 16 перекодирует код Z, Z,, Z, а преобразователь 17 код Z,, Z +, Z," (фиг. 1) в соответствии с табл. 2, где для преобразователя 16 К =2, ) = 4, а для преобразователя !7 К= 3, у = 6.

1309070

Таблица 2

Код входной

0 0

00 0

О 1

0 1

1 0

1 0

1 1

1 1

0001

0010

0011

0100

1000

0111

0110

0101

Если Z =О, значения обеих тетрад отличаются от нуля и от девяти, и, следовательно, Z„, Z» и Z», Z," есть сжатые коды соответственно первой и второй тетрад.

Поэтому сигнал Z< — — О, воздействуя на инверсный управляющий вход мультиплексора 22, вызывает подключение его выходов к выходам преобразователя 16.

Этот же сигнал через элемент ИЛИ 23 передает на выходы элементов И 26 — 29 код с выходов преобразователя 17.

Таким образом, при Z =О работают оба преобразователя 16 и !7, которые по сжатым кодам формируют тетрады развертываемого байта. Разряды этого байта, проходя через мультиплексор 22, элементы

И 26 — 29 и элементы ИЛИ 24,25,30 и 31 поступают на первый байт регистра 1.

Если Z =1, это означает, что в составе исходного байта была тетрада, значение которой равно или нулю, или девяти. Если такая тетрада одна и она является первой, Z< = 1, Z5 — — О, если она является второй, Z, О, Z", = 1, если же обе тетрады являются тактовыми, Z, = Z"-1. Следовательно, при Z, =1 в разрядах Z„", Z, содержится развертывающая информация и поэтому преобразователь !6 должен быть логически отключен, что обеспечивается подключением разряда Z, на инверсный управляющий вход мультиплексора 22.

При Z, = 1, Z» = 1 и Z", =-О, разряды

Z,", Z» содержат сжатый код второй тетрады, а код первой тетрады, значение которой равно нулю или девяти, формируется элементом И 20, на входы которого поступают сигналы от разрядов Z,, Z и Х;; .

99. В первом случае все развертывающие блоки устройства бездействуют и поэтому йа вход pet èñòðà 1 поступает код «0000 0000»

Во втором случае срабатывает элемент И 21

Условие Z = 1 означает, что значение первой тетрады равно нулю или девяти. Условие Z< = 1 означает, что значение первой тетрады находится между пятью и девятью.

Следовательно 7, Zp 7.", =1 означает, что значение первой тетрады равно девяти, а

7, 7 Х, = 1 означает, что значение первой тетрады равно нулю.

Поэтому, при 7> Z» Z, 1 элемент И

20 вырабатывает единичный сигнал, который, проходя через элементы ИЛИ 24 и 25, поступает на первый и четвертый входы первой тетрады регистра 1, на второй и третий входы которой поступают нулевые сигналы с выходов мультиплексора 22.

Одновременно с элементом И 20 срабатывает элемент И 19, на вход которого поступают сигналы разрядов Х, и Z

Условие ZI Z =1 означает, что значение второй тетрады не равно нулю или девяти и поэтому она должна быть получена с выхода преобразователя 17. Это реализуется единичным сигналом с выхода элемента И !9, который проходит через элемент ИЛИ 23 и вызывает передачу кода с выходов преобразователя 17 через элеменр5 ты И 26 — -29. Сигналы с выходов элементов

И 26 — 29, проходя через элементы ИЛИ

30 и 31, поступают на первый и четвертый разряды второй тетрады регистра 1, на второй и третий разряды которой поступают сигналы с выходов элементов И 27 и 28.

В случае Z< = =1, Z» = О, 7» =! разряды

»»

Z,, Z, содержат сжатый код первой тетрады, а код второй тетрады формируется элементом И 21, на входы которого поступают сигналы Z<, Zq, Z, Назначение сигналов Z,, Z такое же, как и назначение рассмотренных сигналов

Z, Z»,, Когда Х, Z< — — 1, срабатывает элемент И 21, единичный сигнал с выхода которого, проходя через элементы ИЛИ 30 и 31, поступает на нервый и четвертый вхо4р ды второй тетрады регистра 1, на второй и третий входы которой поступают нулевые сигналы от выходов элементов И 27 и 28.

Одновременно срабатывает н элемент И 18, на входы которого поступают Z< Z<. Условие Z Z = 1 означает, что значение первой тетрады не равно нулю или девяти и код этой тетрады формируется преобразователем 17. Г1оэтому единичный сигнал с входа элемента И 18 вызывает передачу кода с выхода преобразователя 17 через мультиплексор 22 и элементы ИЛИ 24 и 25 на первую тетраду регистра 1.

При Zi — — 7» = Z< — — 1 значения первой и второй тетрад равны нулю или девяти. т.е. значение развертываемого байта представляет собой число 00 или 09, или 90, 1309070

Формула иг>обрет(нгг..г

7 и как было показано выше (случай Z Z>Z"=

1) на вторую тетраду регистра поступает код «1001», а на первую тетраду регистра 1 — код «0000». В третьем случае срабатывает элемент И 20 (слу<гай Z, Z, 7.;"; =1) и на вход первой тетрады регистра 1 поступает код «1001», а на вход второй тетрады регистра 1 поступает код «0000». В четвертом случае срабатывают элементы И 20 и 21 и на вход регистра поступает код

«1001 1001».

Первый тактовый сигнал (считая с момента начала развертывания) сдвигает единицу из триггера 49 в триггер 50 (фиг. 6).

Так как триггер 59 находится в единичном состоянии, на выходе элемента И 67 дешифратора 51 возникает единичный сигнал, который синхронизирует входы первого байта регистра 1, что вызывает запись развернутого байта в регистр 1. Этот же сигнал, проходя через элемент ИЛИ 52, уменьшает содержимое счетчика 14 на единицу и тем самым отмечает факт развертывания одного байта. Если Z< 2.";Х = 1, сжатый код байта имеет длину, равную пяти. В противном случае это длина равна семи. Поэтому при

Z37. Zf —— 1 срабатывает элемент И 55 (фиг. 6) и единичный сигнал с его выхода, проходя через элемент ИЛИ 57, устанавливает в счетчике 15 код «101». В противном случае нулевой сигнал с выхода элемента

И 55, проходя через элемент ИЛИ 56, устанавливает в счетчике 15 код «111».

Дешифратор 58 подключают через элемент И 66, вход триггера 60 к выходу триггера 51, если содержимое счетчика 14 не равно нулю, т. е. если развернутый байт не был последним. B противном случае на выходе элемента И 67 дешифратора 58 возникает сигнал о конце процесса развертывания.

Если счетчик 14 не обнулен, необходимо выполнить подготовительную работу для развертывания следующего байта, что осуществляется на следующих двух состояниях блока !3 управления, которые инициируются тактовыми сигналами, начиная с второго.

Второй синхросигнал от генератора 53 сдвигает единицу из триггера 50 в триггер 60, который вызывает единичный сигнал на выходе элемента И 67 дешифратора 61. Этот сигнал сдвигает содержимое регистра 1 на один байт вправо.

Третий тактовый сигчал сдвигает единицу из триггера 60 через элемент ИЛИ 62 в триггер 63, выходной сигнал которого уменьшает содержимое счетчика 15 на единицу и возбуждает дешифраторы 64 и 65. Единичный сигнал возникает на выходе элемента И 67 дешифратора 64 и сдвигает содержимое регистра 2 на один разряд вправо.

Дешифратор 65 контролирует количество сдвигов содержимого регистра 2. Пока счетчик 15 не обнулен, все следующие синхросигналы от генератора 53 переводят едини25

8 цу из триггера 63 через элемент 1! 66>;1(шифратора 65 в т(>Г жc триггер 63. 1!О(,ге обнуления счетчика 15 срабатыва(т элемент И 67 дешпфратора 65, сигнал с которого, проходя через элемент И, 1И 48, уланавливает триггер 49 в еднничш>е с<>стояние, и устройство переходит в с()cT()>lllllc готовности для развертывания Очеред<и>п> байта.

Все остальные байты ) BBI3c1) TI>l 13;I I() I (я аналогичным образом. В резульга rc р(гистр 2 освобождается, а регггстр 1 нагj>ужается развернутыми байтами. которы(ч О;1.— но извлечь из устройства.

Применение изобретения в си(.гcxl,>x работки данных способствует экоггочп>1 >б;,(. ма памяти, требуемой для хранения цси; .:1HbIx данных, и экономии време>гн (п>ч f1<1 данными.

1. Устройство для сжатия и развертывания информации, содержащее блок х Ii))(113леHèÿ, первые выxод и вxoä котороп> сосдинены соответственно с вычитающим ВхоДОМ И ВЫХОДОМ II(>РВОГО (l(>ТЧИKI>IC выход и Bxo. I, соединены соответсгв Illlo с вычитающим вxo To»I и Выxoäoxl ВToj)oï> счетчика, третий — — шестой Выхо.ll>l соединены с входами соответственно сдвиг влсBo, сдВИГ BflpdBO и(.рвОГО р(.ГIICT1)d И СтВ11Г 13,1<. во, сдвиг вправо второго регистра, первый выход второго регистра соединен с прямыми входами первого, второго элементов И и с первым входом третьего элемента И, второй выход соединен с инверсным Вхо.то)1 псрвого элемента И и третьим входом блока управления, третий выxoä cоединен с инверсным входом второго элемента И и гствертым входом блока управления, четвертый восьмой элементы И, от>гггчаю(г(еее,г тсч, что, с целью повышения информативности уcTройства, в него введены дсшифраторы, I)j)собразователи кода, элементы ИЛИ, элемент запрет и мультиплексоры, входыгвыходы первого и второго регистров являк)тся соответственно первыми и вторым и информационными входами/выходам и устройства, первые выходы первого регистра соединены с соответствующими входами первого, второго дешифраторов и первого преобразов»теля кода, вторые выходы перво>О регистра соединены с соответствующими входами третьего, четвертого дешифраторов н второго преобразователя кода, Вы хо z пер Во го дешифратора соединен с пятым входоч блока управления, первым входом. первого элемента ИЛИ, инверсным входоч элемента

ЗАГ!РЕТ и первыч информационным входом первого мультиплексора, выход третьего дешифратора cocgll llcll с шестым Bxo;1oM блока управления, вторым входом первого элемента ИЛИ, прямым входом элемента

1309070

10

ЗАПРЕТ, вторым информационным входом первого мультиплексора и инверсным управляющим входом второго мультиплексора, первый, второй выходы первого преобразователя кода соединены с соответствующими третьим, четвертым информационными входами первого мультиплексора и первым, вторым информационными входами второго мультиплексора, первый, второй выходы второго преобразователя кода соединены с соответствующими третьим, четвертым информационными входами второго мультиплексора, выход элемента ЗАПРЕТ соединен с прямым управляющим входом второго мультиплексора, выход первого элемента ИЛИ соединен с прямым и инверсным управляющими входами первого мультиплексора и первым информационным входом второго регистра, выходы второго, четвертого дешифраторов, первого и второго мультиплексоров соединены с соответству|ощими вторыми информационными входами второго регистра, четвертый выход которого соединен с первым входом третьего преобразователя кода и вторым входом третьего элемента И, пятый выход соединен с первыми входами четвертого преобразователя кода и четвертого элемента И, шестой и седьмой выходы соединены соответственно с вторым и третьим входами четвертого преобразователя кода, первый — четвертый выходы которого соединены с соответствующими первыми информационными входами третьего мультиплексора и первыми входами соответствующих пятого — восьмого элементов И, выходы пятого и восьмого элементов И соединены с первыми входами соответственно второго и третьего элементов ИЛИ, вторые входы третьего преобразователя кода, четвертого элемента И объединены и подкл1очены к третьему выходу второго регистра, третий вход четвертого элемента И, инверсный вход четвертого элемента ИЛИ, седьмой вход блока управления и инверсный управляющий вход третьего мультиплексора объединены и подключены к первому выходу второго регистра, третьи входы третьего элемента И и третьего преобразователя кода объединены и подключены к второму выходу второго регистра, первый выход первого элемента И и выходы третьего преобразователя кода соединены соответственно с прямым управляющим и соответствуюгцими вторыми информационными входами третьего мультиплексора, первый и второй выходы которого соединены с первыми входами соответственно пятого и шестого элементов ИЛИ, выходы второго — четвертого элементов И соединены соответственно с прямым входом четвертого элемента ИЛИ, вторыми входами пятого, шестого элементов ИЛИ и вторыми входами второго, третьего элементов

ИЛИ, выход четвертого элемента ИЛИ соединен с вторыми входами пятого--восьмого

10 элементов И, выходы второго, третьего, пятого, шестого элементов ИЛИ, шестого, седьмого элемcHTQB И и третий, четвертый выходы третьего мультиплексора соединены с соответствующими информационными входами первого регистра, восьмой, девятый входы блока управления и информационный вход первого счетчика являются соответственно первым — третьим уиравляюгцими входами устройства, седьмой — десятый выходы блока управления соединены соответственно с тактовыми входами первого, второго регистров, первым и вторым информационными входами второго счетчика.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит генератор тактовых импульсов, элементы И, элементы

ИЛИ, триггеры и дешифраторы, выход первого элемента ИЛИ соединен с информационным входом первого триггера, выход которого соединен с информационным входом второго триггера, выход которого соединен с первым входом первого, второго дешифраторов, первого и второго элементов И, первый и второй выходы первого дешифратора соединены с соответствующими первым и вторым входами второго элемента ИЛИ и являются седьм ым и восьм ым выходам и блока управления. выход первого элемента

И соединен с первыми входами третьего, четвертого элементов ИЛ И, выход второго элемента И соединен с вторыми входами третьего, четвертого элементов ИЛИ, выходы которых являются девятым, десятым выходами блока управления, выход второго дешифратора соединен с информационным входом третьего триггера, выход которого соединен с первыми входами третьего дешифратора и пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен с информационным входом четвертого триггера, выход которого соединен с первыми входами четвертого, пятого дешифраторов и является вторым выходом блока управления, первый и второй выходы пятого дешифратора соеди иены соответствен но с вторым входом пятого элемента ИЛИ и первым входом первого элемента ИЛИ, выход пятого триггера соединен с вторыми входами первого, третьего, четвертого дешифраторов и первого, второго элементов И, выход генератора тактовых импульсов соединен с тактовыми входам и первого- — четвертого три ггеров; второй вход второго дешифратора, второй вход пятого дешифратора, третий, четвертый входы второго элемента И, третий, четвертый входы первого элемента И, пятый вход второго элемента И, объединенные вход установки в «О» пятого триггера и второй вход первого элемента ИЛИ и объединенные вход установки в «1» триггера и третий вход первого элемента ИЛИ являются соответственно первым — девятым входами бло1309070 фиг.2

7,3 ка управления, выход второго элемента

ИЛИ, первый, второй выходы третьего дешифратора, первый и второй выходы четвер12 того дешифратора являются соответственно первым, третьим — шестым выходами блока управления.

7Г 15

h 15

ОШ

П/П

om РР2 7

Составитель М. Никулеиков

Редактор Н. Рогулич Техред И. Верес Корректор Л. Зимокосов

Заказ 1438/44 Тираж 544 Г!одиисное

ВНИИПИ Государственного комтпта СССР ио делам изобретений и открытий

113()35, Москва, Ж- -35, Раугиская иаб., д. 415

Производственно-полиграфическое предприятие, г. Ужгород, ул. П роек гиая, 4