Устройство для выработки синхросигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и, в частности , предназначено для использования в системах обработки данных. Целью изобретения является расширение функциональных возможностей за счет обеспечения приостанова вьщачи синхроимпульсов и повторного запуска с различных моментов времени. Отличительной особенностью устройства является запоминание адреса блока памяти, по которому осуществляется приостанов устройства и последующее возобновление работы устройства либо с начального адреса, либо с запомненного. Поставленная цель достигается за счет введения триггеров, элемента ИЛИ, элемента И, блока сравнения. 1 ил. (С

СОЮЗ СОВЕТСНИХ

СОЩИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„80„„1310793 А 1 (511 4 С 06 F 1/04

1Г1 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . I

Н АВТОРСКОМУ .СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ГЮ ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 4007697/24-24 (22) 06 ° 01.86 (46) 15.05.87. Бюл. У 18 (71) Институт ядерных исследований Н УССР (72) В.И. Кирищук и В.И. Гаврилюк (53) 681.3(088.8) (56) Патент США 11 4231104, кл. G 06 Р 1/04, 1980.

Патент Великобритании 9 1509059, кл. G 06 P 1/04, 1978. (54) УСТРОЙСТВО ДЛЯ ВЫРАБОТКИ СИНХРОСИГНАЛОВ (57) Изобретение относится к области вычислительной техники и, в частности, предназначено для использования в системах обработки данных. Целью изобретения является расширение функциональных возможностей за счет обеспечения приостанова выдачи синхроимпульсов и повторного запуска с различных моментов времени. Отличительной особенностью устройства является запоминание адреса блока памяти, по которому осуществляется приостанов устройства и последующее возобновление работы устройства либо с начального адреса, либо с запомненного. Поставленная цель достигается за счет введения триггеров, элемента ИЛИ, элемента И, блока сравнения. 1 ил.! 310793

Изобретение относится к вычислительной технике и, в частности, предназначено для использования в системах обработки данных.

Цель изобретения — расширение фун- 5 кциональных возможностей за счет обеспечения приостанова выдачи синхроимпульсов и повторного запуска с различных моментов времени.

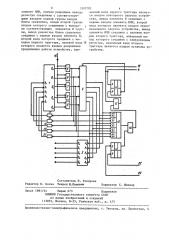

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит блок 1 постоянной памяти, регистр 2, блок 3 постоянной памяти, вход 4 останова устройства, элементы И 5-9 группы, 15 блок 10 сравнения, триггер 11, элемент ИЛИ 12, триггер 13, элемент

И 14, вход 15 запуска устройства, вход 16 начальной установки устройства, элементы 17-21 задержки, вход 22

20 разрешения продолжения работы устройства и вход 23 повторного запуска устройства.

Устройство работает следующим образом.

В исходном состоянии сигналами по входам 15 и 22 устройства триггеры 11 и 13 устанавливаются в "0".

В блоке 1 постоянной памяти младшие выходные разряды соединены через элементы 17-21 задержки с адресными входами.

Блок 1 памяти программируется таким образом, что в каждой ячейке записан адрес следующей ячейки в некоторой замкнутой последовательности так, что при работе устройства блок 1 памяти постоянно, циклически адресуется к самому себе, формируя на сво- 40 их выходах тактовые сигналы.

Выходы блока 1 памяти соединены с информационными входами регистра 2, с помощью которого разрешается или запрещается передача данных в зависи- 4> мости от потенциала на синхровходе регистра 2, поступающего с инверсного выхода триггера 11.

Так как триггер ll установлен в

"0", то на его инверсном выходе имеется "1", которая разрешает прохождение сигналов через регистр 2.

При этом разрешается передача счетной последовательности с выходов блока 1 постоянной памяти на адресные входы блока 3 постоянной памяти, а прохождение сигналов с выхода блока 10 сравнения через элемент И 14 блокируется триггером 13, В. случае поступления сигнала к входу 4 останова устройства "1" триггер 11 устанавливается в !", тем самым останавливая генерацию тактовых импульсов на выходах устройства. После поступления сигнала к входу 22 разрешения продолжения работы устройства триггер 11 устанавлив;ется в "0", блокирует сигнал с выхода блока 10 сравнения и запускает с самого начала счетную последовательность, для чего необходимо еще подать сигнал "0" на вход 16 начальной установки устрой\ ства.

При поступлении сигнала "I" к входу 23 повторного запуска устройства триггер 13 устанавливается в "1", разрешая прохождение сигнала с выхода блока 10 сравнения в момент совпацения состояния выходов блока 1 памяти и содержимого регистра 2 через элементы 12 и 14 на нулевой вход триггера 11, сброс в "0" которого приводит к продолжению начатой последовательности: тактовых импульсов.

Затем при поступлении сигнала к входу 23 триггер 13 устанавливается в "0" и устройство продолжает свою работу.

Формула и з обретения

Устройство для выработки -синхросигналов, содержащее два блока постоянной памяти, регистр, группу элементов задержки, группу элементов И, причем выходы первого блока постоянной памяти соединены соответственно с первыми входами элементов И группы, вторые входы которых объединены и подключены к входу начальной установки устройства, выходы элементов И группы соединены с соответствующими информационными входами регистра и с входами соответствующих элементов задержки группы, выходы которых соединены с соответствующими адресными входами первого блока постоянной памяти, разрядные выходы регистра соединены с адресными входами второго блока постоянной памяти, выходы которого.,являются информационными выходами устройства, о т л и ч а ю щ е— е с я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения приостанова выдачи синхроимпульсов и повторного запуска с различных моментов времени, в устройство введены блок сравнения, два триггера, элемент И и

3 13! 0793 4 элемент ИЛИ, причем разрядные выходы ничный вход первого триггера являетрегистра соединены с соответствую- ся входом повторного запуска устройщими входами первой группы входов ства, выход элемента И соединен с блока сравнения, входы второй группы первым входом элемента ИЛИ, второй входов которого соединены с выхода- - вход которого является входом перно) ми соответствующих элементов И груп- начального запуска устройства, выход пы, выход равенства блока сравнения элемента ИЛИ соединен с нулевым вхосоединен с первым входом элемента И, дом второго триггера, инверсный выI второй вход которого соединен с вы- ход которого соединен с синхровходом ходом первого триггера, нулевой вход 1О регистра, единичный вход второго которого является входом разрешения триггера является входом останкова успродолжения работы устройства, еди- тройства.

Составитель Н. Топорова

Редактор Е. Копча Техред И.Попович Корректор С. Шекмар

Заказ 1891/44 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4