Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может использоваться в микропроцессорных системах с микропрограммным управлением. Цель изобретения - увеличение быстродействия . Устройство содержит региистр адреса, блок памяти микропрограмм регистр микроопераций, блок анализа условий, коммутатор, схему сравнения и генератор тактовых импульсов. Цель изобретения достигается тем, что при безуслов}1ых переходах генератор формирует укороченную по длительно - сти серию синхроимпульсов работы устройства . . ил. (Л X :л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (я) 4 G 06 Р 9/22

Ч" с

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АBTOPCHOMV СВИДЕТЕЛЬСТВУ с.. "1 с

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3949665/24-24 (22) 09.09.85 (46) 15.05.87. Бил. 9 18 (72) Г.В.Галкин, Л.Д.Минутин и О.О.Попов (53) 681.325 (088,8) (56) Майоров С.А °, Новиков Г,И.

Принципы организации цифровых машин, — Л.: Машиностроение, 1974, с. 203, рис. 6.4, М айоров С, А., Нов ик ов Г. И, Структура 3BM. — Л,: Машиностроение, 1979, с. 314, рис ° 10.4, (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может использоваться в микропроцессорных системах с микропрограммным управлением. Цель изобретения — увеличение быстродействия. Устройство содержит регнстр адреса, блок памяти микропрограмм регистр микроопераций, блок анализа условий, коммутатор, схему сравнения и генератор тактовых импульсов. Цель изобретения достигается тем, что при безусловных переходах генератор формирует укороченную по длительно. сти серию синхроимпульсов работы уст- ф ройства. 2 ил.

131081

5 2 налов блоком 4 и задержки на прохождение А1 или А2 через открытое плечо коммутатора 5, При состоянии признака ПР=О открывается плечо для Аl, при ПР = 1 — для A2/Аl либо А2 заносится в регистр 1; по этому адресу в блоке 2 начинается выборка. Выборка

i-го признака происходит путем дешифрации кода УСОП в дешифраторе 8 и выдачи разрешающего сигнала на i-1 элемент И (9-i), Далее сигнал распространяется через элемент ИЛИ 10 и инвертор 11, При условном переходе схема 6 вырабатыв ает "0" (А1ФА2), по которому генератор 7 выдает синхроимпульсы на регистр 1 с задержкой, с учетом за- 55 держки формирования достоверных сигI Изобретение относится к вычисли. тельной технике, в -частности к микропроцессорам с микропрограммным управлением, Цель изобретения — увеличение 5 быстродействия устройства.

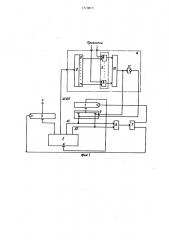

На фиг,l представлена функциональная схема устройства; на фиг,2 — алгоритм функционирования устройства.

Устройство (фиг. 1) содержит ре- !О гистр адреса, блок 2 памяти микропрограмм, регистр 3 микроопераций, блок 4 анализа условий, коммутатор

5, схему 6 сравнения и генератор 7 тактовых импульсов.

Блок 4 анализа условий содержит дешифратор 8, группу 9 элементов И, элемент ИЛИ 10 и инвертор 11.

Устройство работает следующим образом.

В исходном положении регистр 1 адреса обнуляется, в результате происходит выборка по нулевому адресу начальной микрокоманды из блока 2 памяти микропрограмм. С момента вы25 дачи этой микрокоманды начинается первый такт работы устройства, После микроинструкции F записывается в ре гистр 3 микроопераций, код признака

УСОП поступает на управляющий вход З-0 блока 4. Старшие и младшие разряды адреса A) и А2 поступают на коммутатор 5 и схему 6 сравнения, которая управляет генератором 7.

С началом такта происходит декоди- 35 рование кода УСОП в дешифраторе 8, прохождение разрядов адреса Al или

А2 через коммутатор 5, процедура сравнения Al и А2 в схеме 6 и запись поля F в регистр 3. Далее алгоритм 40 функционирования зависит от типа перехода к следующей микрокоманде.

При безусловном переходе схема

6 вырабатывает сигнал "1" (Аl=А2), по которому генератор 7 сразу выдает 45 импульс на синхровход регистра 1, В регистр заносится очередной адрес

А следующей микрокоманды (A=Al=A2), по которому в блоке 2 начинается ее выборка, 50

Формул а изобретения

Микропрограммное устройство управления, содержащее регистр адреса, регистр микроопераций, блок памяти микропрограмм, коммутатор, блок анализа условий и генератор тактовых импульсов, причем первый и второй выходы блока анализа условий соединены с первьм и вторым управляющими входами коммутатора, выход поля микроопераций блока памяти микропрограмм соединен с информационным входом регистра микроолераций, выход к оторого являет ся выходом микроопераций устройства, входы условий устройства являются информационными входами блока анализа условий, управляющий вход которого соединен с выходом поля условий блока памяти микропрограмм, выход старших разрядов адреса которого соединен с первым информа— ционным входом коммутатора, второй информационный вход которого соединен с выходом младших разрядов адреса блока памяти микропрограмм, адресный вход которого соединен с выходом регистра адреса, выходы перво

ro и второго режимов синхронизации генератора тактовых импульсов соединены соответственно с синхровходами регистра микроопераций и регистра адреса, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, в него введена схема сравнения, причем выходы старших и младших разрядов адреса блока памяти микропрограмм соединены соответственно с первым и вторым входами схемы сравнения, выход которой соединен с входом запуска генератора тактовых и мпул ь сов .

Прнзнани фиУ 1! 310815

Составитель 1О.Ландов

Редактор М,Дылын Техред Л.Олейник Корректор С. Черни

Заказ 1892/45 Тираж б73 Подписное

В НИИПИ Государственного коми тета С ССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул, Проектная, 4.