Адаптивный анализатор плотности распределения вероятностей

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для анализа статистических характеристик случайных процессов в условиях недостатка априорной информации. Цель изобретения - повышение точности оценки гистограммы. Анализатор содержит усреднитель 1, блок 2 вычитания, формирователь 3 модуля сигнала, блок 4 вычисления максимума , дискриминатор 5 знака, блок 6 синхронизации, триггер 7, элементы И 8, 15. 16, счетчики 9,17, элементы ШШ 12,13, цифроаналоговый преобразователь 10, элемент 11 сравнения , регистр 14 сдвига, блоки 18, 19 памяти, блок 20 элементов ИЛИ. Работа анализатора основана на адаптивном вь иислении масштаба преобразования на этапе обучения и вычисления гистограммы в полученном масштабе на этапе оценивания. 2 ил. (Л Сдд 00 4: фиеА

СОЮЗ СОВЕТСНИ)(СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19). (11) (594 С 06 F 15 36

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

KF ":" ." "

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 3

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21,) 4024380/24-24 (22) 19.02.86 (46) 15.05.87, Бюл. № 18 (72) В.И.Якименко, Т.Н.Редуто, Ю.А.Мироненко и Ц.Б.Эпштейн (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 877564, кл. С 06 Р 15/36, 1980.

Авторское свидетельство СССР

Ф 1078435, кл. С 06 F 15/36, 1982. (54) АДАПТИВНЫЙ АНАЛИЗАТОР ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ (57) Изобретение относится к области вычислительной техники и предназначено для анализа статистических характеристик случайных процессов в условиях недостатка априорной информации ° Цель изобретения — повышение точности оценки гистограммы. Анализатор содержит усреднитель 1, блок 2 вычитания, формирователь 3 модуля сигнала, блок 4 вычисления максимума, дискриминатор 5 знака, блок 6 синхронизации, триггер 7, элементы

И 8, 15. 16, счетчики 9,17, элементы ИЛИ 12, 13, цифроаналоговый преобразователь 10, элемент 11 сравнения, регистр 14 сдвига, блоки 18, 19 памяти, блок 20 элементов ИЛИ. Работа анализатора основана на адаптивном вычислении масштаба преобразования на этапе обучения и вычисления гистограммы в полученном масштабе на этапе оценивания. 2 ил, 1 13

Изобретение относится к вычислительной технике и предназначено для определения статистических характеристик случайных процессов в условиях недостатка априорной информации, например в системах связи для анализа распределения интервалов между сообщениями или распределения количества ошибок в пачке импульсов.

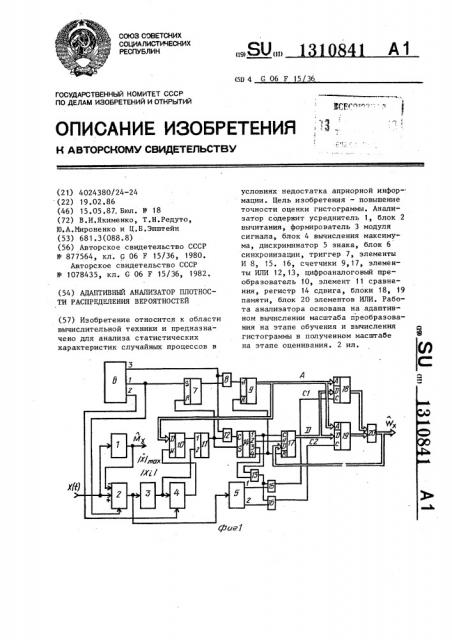

Целью изобретения является повышение точности оценки гистограммы, На фиг. 1 представлена структурная схема адаптивного анализатора, на фиг.2 - структурная схема блока синхронизации.

Анализатор (фиг. 1) содержит усреднитель 1, блок 2 вычитания, формирователь 3 модуля сигнала, блок 4 вычисления максимума, дискриминатор 5 знака, блок 6 синхронизации, триггер 7, элемент И 8, счетчик 9, цифроаналоговый преобразователь 10, эле мент 11 сравнения, элементы ИЛИ 12 и 13, регистр 14 сдвига, элементы

И 15, 16, счетчик 17, блоки 18, 18 памяти, блок 19 элементов ИЛИ.

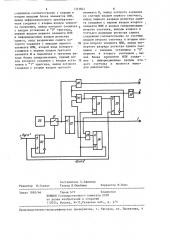

Блок 6 синхронизации (фиг.2) содержит генератор 20 тактовых импульсов, переключатель 21, счетчики

22-24, триггер 25, элементы И 26-28, элемент 29 задержки. Выход переполнения счетчика 22 подключен к первому выходу блока 6 синхронизации, первые входы элементов И 26 и 27 соеэ динены соответственно со входом и выходом переполнения счетчика 22, а второй вход элемента И 26, инверсный вход элемента И 27 и первый вход элемента И 28 подключены к инверсному выходу триггера 25. Выход элемента И 27 через элемент 29 задержки соединен с вторым выходом, выход элемента И 26 — с третьим выходом блока 6 синхронизации, вход

R триггера 25 и вход S триггера 30 подключены ко входу начальной установки, Адаптивный анализатор осуществляет вычисление плотности распределения вероятностей за два этапа: этап обучения и этап оценивания функции W„.

В исходном состоянии блоки анализатора установлены в нулевое состояние, а в блоке 6 синхронизации на первом выходе формируются импульсы дискретизации исследуемого сигнала, на втором выходе — задержанные импуль1 0841 2

55 сы с частотой, равной частоте дискре тизации, на третьем выходе — импульсы тактовой частоты, определяемой быстродействием логических элементов.

С этапа обучения начинается анализ сигнала.

Вычисляемая в усреднителе 1 текущая оценка среднего значения М(х) поступает на вход блока 2 вычитания, в котором осуществляются операции цискретизации и вычитания, вследствие чего на выходе образуются отсчеты центрированного случайного процес. са х(ьг) = x(i М) — M(x)

Центрированный двуполярный сигнал в виде ряда отсчетов поступает на вход формирователя 3 модуля сигнала, в котором вычисляется абсолютное значение этих отсчетов (x> ). При считывании каждого 1-го отсчета на вход блока 4 вычисления максимума в нем по сигналу блока управляющей синхронизации разрешается операция сравнения амплитуды отсчета (х,.) с максимальным значением отсчета (х, „) из ранее поступившей последовательности отсчетов и большее из этих значений запоминается для последую его сравнения.

Так, в блоке 4 вычисления максимума производится отбор и фиксация максимального из модулей отсчетов сигнала, который является характеристикой размаха (диапазона изменения аргумента) вычисляемой функции W(x).

Следовательно, значение (х)„ „, задает шкалу измерений и величину шага аппроксимации а х = (х) „, /К, где К— количество дифференциальных коридоров (ординат) каждой из ветвей функции °

Так как определение максимального иэ значений модулей отсчетов, как правило, не требует высокой досто верности, то этап обучения может осуществляться на небольшом интервале Т К (0,2-0,3) Т, где Т вЂ” интервал вычисления оценки W(x) т.е, длительность этапа оценивания.

Этап оценивания осуществляется нри начальном условии, сформированном на этапе обучения: из первоначальных текущих данных в блоке 4 вычисления максимума получена информация об ожидаемом амплитудном диапазоне функции, а в блоке 6 синхрони131 08

30 зации тактовые импульсы начинают поступать на третий выход.

Процедура обработки в усреднителе 1, блоке 2 вычитания и формирователе 3 модуля сигнала выполняется аналогично этапу обучения, а в дискриминаторе 5 знака сигнала определяется знак отсчета.

Одновременно с этим, по сигналам с первого выхода блока 6 синхро- . 10 низации срабатывает триггер 7, открывая элемент И 8 для прохождения тактовых импульсов на счетный вход счетчика 9, текущие значения А выходного кода которого формирует 15 на выходе цифроаналогового преобразователя 10 ступенчато-изменяющееся напряжение ° При этом, величина кажЬ дой ступени зависит от значения (х) мак1 подключенного к опорному входу цифро-20 аналогового преобразователя 10 °

При выполнении соотношения А = (х„) срабатывает элемент 11 сравнения, выходной импульс которого поступая на вход установки в "ноль" триг- 25 гера 7, возвращает его в исходное состояние, при котором запрещается прохождение тактовых импульсов на вход счетчика 9 адреса.

Одновременно импульс с выхода элемента 11 сравнения поступает на информационный вход регистра 14 и через элемент ИЛИ 12 — на тактовый вход вследствие чего единичный импульс записывается в первую ячейку (раз-,,ряд) регистра 14 сдвига, являясь при этом сигналом разрешения считывания (через элемент ИЛИ 13 и элементы

И 15 или 16) блоков 18 и 18„ памяти, синхронизирующим сигналом разрешения записи кода 4, считанного по коду адреса Aw из блоков "8 или 18» памяти в счетчик 17. Очередной тактовый импульс с третьего выхода блока 6 синхронизации, поступая на тактовый вход регистра 14 сдвига, осуществляет сдвиг единичного импульса во второй разряд, что является сигналом разрешения счета для счетчика 17: его содержимое увеличивается на единицу и становится равным (11„ +1)-. По следующему сигналу— с третьего разряда регистра 14. сдвига — разрешается запись этого кода (N +1) в ту же m-ую ячейку блоков 18 или 18,памяти (в соответствии с кодом адреса A „), а по сигналу с выхода четвертого разряда осу41 4 ществляется обнуление счетчиков 9 и 17.

В результате выполнения этапов обучения и оценивания в первом и втором блоках 18, 18„ памяти накоплены оценки плотности распределения вероятностей в соответствии с отрицательным или положительными отсчетами центрированного сигнала.

Формула изобретения

Адаптивный анализатор плотности распределения вероятностей, содержащий усреднитель, регистр сдвига, элемент сравнения, два счетчика, блок синхронизации, дискриминатор знака, блок вычитания, формирователь модуля сигнала, блок вычисления максимума, два элемента И, причем вход уменьшаемого блока вычитания соединен с входом усреднителя и является входом анализатора, выход усреднителя соединен с входом вычитаемого блока вычитания и является выходом среднего значения анализатора, выход блока вычитания соединен с входом дискри минатора знака и через формирователь модуля сигнала соединен с информационным входом блока вычисления максимума и первым .входом элемента сравнения,выходы "Больше нуля" и "Меньше нуля" дискриминатора знака соединены соответственно с первыми входами .первого и второго элементов И, первый и второй выходы блока синхронизации соединены соответственно с тактовыми входами блока вычитания и блока вычисления максимума, о т л и ч а юшийся тем, что, с целью повышения точности, в него введены два элемента ИЛИ, два блока памяти, триггер, третий элемент И, блок элементов ИЛИ и цифроаналоговый преобразователь, причем, выход блока вычисления максимума соединен с входом опорного напряжения цифроаналогового преобразователя, цифровой вход которого соединен с выходом первого счетчика и адресными входами первого и второго блоков памяти, информационные входы которых соединены с выходом второго счетчика, входы разрешения считывания первого и второго блоков памяти соединены соответственно с выходами первого и второго элементов И, а выходы первого и второго блоков памяти

Составитель Е.Ефимова

Техред Л.Олейник Корректор М.Пожо

Редактор Н.Горват

Заказ 1893/46

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4 соединены соответственно с первым и вторым входами блока элементов ИЛИ, выход цифроаналогового преобразова-, теля соединен с вторым входом элемента сравнения, выход которого соединен с входом установки в "0" триггера, первым входом первого элемента ИЛИ и информационным входом регистра сдвига, вход разрешения сдвига которого соединен с выходом первого элемента ИЛИ, второй вход которого соединен с первым входом третьего элемента И и подключен к третьему выходу блока синхронизации, первый выход которого соединен с вхоДом установки в " 1" триггера, выход которого соединен с вторым входом гретьего

1 0841 6 элемента И, выход которого соединен со счетным входои первого счетчика, выход первого разряда регистра сдвига соединен с первым входом второго

1 элемента ИЛИ и входом синхронизации второго счетчика, выходы второго и третьего разрядов регистра сдвига соединены соответственно со счетным входом второго счетчика и вторым вхоt0 дом второго элемента ИЛИ, выход четвертого разряда регистра сдвига соединен с входами установки в "0" первого и второго счетчиков, выход блока элементов ИЛИ соеди15 нен с информационным входом вто— рого счетчика и является выходом анализатора.