Запоминающее устройство с одновременным считыванием нескольких слов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для буферной памяти данных. Цель изобретения - повышение быстродействия устройства . Буферное запоминающее устройство содержит блок 1 формирователей импульсов, блок 2 сравнения, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3, элемент ИЛИ 4, формирователь 5 импульсов, адресный блок считывания , включающий регистры 7 адресов считывания и дешифраторы 8 адресов считывания, адресный блок 9 записи, включающий регистр 10 адресов записи и дешифратор адресов записи, матрицу 12 ячеек 13 памяти, каждая из которых состоит из запоминающего элемента 14, элементов И 15 и 16, а также регистр 17 записываемых данных, регистры 18 считываемых данных, входы 19 и 20 адреса записи, входы 21-24 адресов считывания. Устройство обеспечивает запись данных из регистра 17 в ячейки 13, выбираемые дешифратором 11 в соответствии с кодом адреса в регистре 10, записанного с входов 19 и 20. Считывание осуществляется независимо по нескольким адресам , записанным с входов 21-24 в регистры 7. При этом дешифраторы 8 активизируют соответствующие ячейки 13 памяти, данные записываются в регистры 18 и поступают на входы устройства. Наличие блока 2 и формирователя 5 обеспечивает осуществление записи данных по требуемому адресу только в случае отсутствия считывания данных по тому же адресу. 4 ил. i 00 со со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (59 4 G 11 С 1! 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

OllHGAHHE HSOEPETEHHR // .

К А BTOPCKOMV СВИДЕТЕЛЬСТВУ (21) 4029167/24-24 (22) 25.02.86 (46) 15.05.87. Бюл. № 18 (72) С. С. Бруфман, Л. И. Галкин, А. N. Попов и B. В. Хватов (53) 681.327.6 (088.8) (56) Авторское свидетельство СССР № 752468, кл. G 11 С 11/00, 1978.

Авторское свидетельство СССР № 970464, кл. G 11 С 11./00, 1981. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С

ОДНОВРЕМЕННЫМ СЧИТЫВАНИЕМ НЕСКОЛЬКИХ СЛОВ (57) Изобретение относится к вычислительной технике и может быть использовано для буферной памяти данных. Цель изобретения — повышение быстродействия устройства. Буферное запоминающее устройство содержит блок 1 формирователей импульсов, блок 2 сравнения, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3, элемент ИЛИ 4, формирователь 5 импульсов, адресный блок считывания, включающий регистры 7 адресов считы.SU» 1310899 А1 вания и дешифраторы 8 адресов считывания, адресный блок 9 записи, включающий регистр 10 адресов записи и дешифратор адресов записи, матрицу 12 ячеек 13 памяти, каждая из которых состоит из запоминающего элемента 14, элементов И 15 и 16, а также регистр 17 записываем ых данных, регистры 18 считываемых данных, входы 19 и 20 адреса записи, входы 21 — 24 адресов считывания. Устройство обеспечивает запись данных из регистра 17 в ячейки 13, выбираемые дешифратором 11 в соответствии с кодом адреса в регистре 10, записанного с входов 19 и 20. Считывание осуществляется независимо по нескольким адресам, записанным с входов 21 — 24 в регистры 7. При этом дешифраторы 8 активизиру- <р а ют соответствующие ячейки 13 памяти, данные записываются в регистры 18 и поступают на входы устройства. Наличие блока 2 и формирователя 5 обеспечивает осуществле- С ние записи данных по требуемому адресу только в случае отсутствия считывания данных по тому же адресу. 4 ил. в

131

Изобретение относится к вычислительной технике и может быть использовано для буферной памяти, а также может применяться в системах передачи информации.

Целью изобретения является повышение быстродействия устройства.

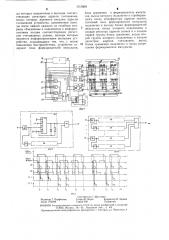

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 и 3 — две возможные модификации блока формирователей импульсов; на фиг. 4 — временные диаграммы работы предлагаемого устройства.

Предлагаемое устройство (фиг. ) содержит блок 1 формирователей импульсов, блок 2 сравнения адресов (включающий, например, группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и элемент ИЛИ 4), формирователь 5 импульсов, адресный блок 6 считывания, включающий регистры 7 адресов считывания и дешифраторы 8 адресов считывания, адресный блок 9 записи, включаю ций регистр 10 адресов записи, дешифратор

11 адресов записи, матрицу 12 ячеек 13 памяти, каждая из которых включает запоминающий элемент 14, элемент И 15, элементы

И 16, регистр 17 записываемых данных, регистры 18 считываемых данных направлений выборки, входы 19 и 20 адреса записи, входы 21 — 24 адресов считывания, вход 25 блока 1 формирователей импульсов, выход

26 блока 2 сравнения, выход 27 формирователя 5 импульсов, выходы 28 — 31 дешифраторов 8 адресов считывания, выходы 32 — ЗЗ дешифратора 11 адресов записи, выходы

34 — 36 регистра 17 записываемых данных, входы 37 — 42 регистра 18 считываемых данных, информационные выходы 43 — 44 устройства и информационные входы 45 устройства. Блок 1 формирователей импульсов содержит элемент 46 задержки, элемент

НЕ 47, формирователи 48 импульсов и элемент ИЛИ 49.

На входы 19 и 20 адресов записи устройства поступает код адреса одной из ячеек 13 памяти, в которую производится запись информации. Причем на вход 19 поступает младший разряд кода адреса, а на вход

20 — старший разряд. На входы 21 и 22 поступает код 1-го адреса, на входы 23 и 24 — код п-го адреса, причем на входы

21 и 23 поступают младшие разряды кода адреса опрашиваемых ячеек, а на входы 22 и 24 — старшие разряды.

На выходе 25 блока 1 формирователей импульсов формируется импульсный сигнал записи, поступающий на тактовый вход формирователя 5 импульсов.

С выхода 26 блока 2 сравнения на вход формирователя 5 импульсов поступает сигнал результата поразрядного сравнения кодов адреса записи с кодом адреса выборки. С выхода 27 формирователя 5 импульсов на вход адресного блока 9 записи поступает тактовый импульс записи. С выходов 32 и 33 адресного блока 9 записи поступает

0899

2 тактовый импульс записи на одни входы соответствующей группы элементов И 15, на другие входы которых поступает входная информация с регистра 17 С выходов элементов И 15 информация переписывается в соответствующие запоминающие элементы 14.

На выходах 28 — 31 дешифраторов 8 формируются сигналы разрешения выборки, которые разрешают прохождение информации из соответствующей ячейки 13 памяти через элементы И 16 на соответствуюшие входы

37 — 42 регистров 18. Причем на выходах 28 и 29 устанавливаются сигналы разрешения выборки по первому направлению, а на выходах 30 и 31 — — сигналы разрешения выборки по и-му направлению.

При циклической смене кодов адреса записи блок 1 формирователей импульсов (фиг. 2) формирует импульсные сигналы записи на выходе 25 по передним и задним фронтам младшего разряда кода адреса записи, так как смена кода записи однозначно связана с передним и задним фронтами младшего разряда. Элемент 46 задержки необходим для того, чтобы импульсный сигнал

2 записи на выходе 25 сформировался после завершения переходных процессов на выходе 26, вызванных изменением кода адреса записи. Так как формирователь 48 импульсов формирует на своем выходе импульс по переднему фронту сигнала с выхода элеЗО мента 46 задержки, то для получения импульса по заднему фронту сигнал с выхода элемента 46 задержки поступает на вход второго формирователя 48 импульсов через элемент НЕ 47.

При произвольной смене кодов адреса

3 записи блок 1 формирователей импульсов (фиг. 3) содержит по два формирователя 48 импульсов на каждый разряд кода адреса записи, формирующих импульсный сигнал записи при изменении любого разряда кода

4р адреса записи на входах 19 и 20.

Устройство работает следуюшим образом.

По фронту сменяющегося кода адреса записи на входах 19 и 20 устройства блок 1 формирователей импульсов формирует на

4 выходе 25 импульсный сигнал записи, по переднему фронту которого формирователь 5 импульсов при наличии. разрешающего сигнала на выходе 26 блока 2 сравнения формирует тактовый импульс записи на выходе 27, по переднему фронту которого адресный блок 9 записи формирует на одном из своих выходов (32 и 33) в зависимости от кода адреса записи на входах 19 и 20 устройства тактовый им пульс записи, по переднему фронту которого через соответ55 ствуюшие элементы И 15 в соответствующую ячейку 13 памяти переписывается информация с выходов 34 — 36 регистра 17 направлений записи. Таким образом, запись ин1310899

20

Формула изобретения

55 формации в ячейку 13 памяти происходит через время Т, после смены кода адреса записи на входах 19 и 20 устройства. Время

Т, равняется сумме задержек прохождения сигнала через устройства 1, 5, 1, 15 и 14.

При современной элементной базе время Т, составляет доли микросекунды.

При запрещающем сигнале на выходе 26 блока 2 сравнения формирователь 5 импульсов на выходе 27 не формирует тактовый импульс записи. Таким образом, запись новой информации в ячейку 13 памяти в момент времени, когда из нее производится выборка, не происходит, и считывание ложной информации исключено.

Выборка информации осуществляется независимо одна от другой по каждому из направлений. При этом дешифраторы 8 адреса считывания по кодам, находящимся в регистрах 7, формируют сигналы на соответствующих выходах 28 — 31, по которым через элементы И 16 передается информация из запоминающих элементов 14 матрицы 12 в регистры 18.

На диаграммах (фиг. 4) позициями 26 и 25 показаны состояния соответствующих выходов, а позициями 27 — 1 и 27 — 2 показаны возможные состояния выхода 27 управляемого формирователя 5 импульсов.

В момент времени t> 1,; tg, t, устрой ство функционирует в соответствии с описанным алгоритмом. В некоторых случаях на входах управляемого формирователя 5 импульсов возникает «состояние» импульсов, в результате чего возможны 4 ситуации (моменты времени t,, t,, t, и t,).

Устанавливаются несовпадающие коды адресов записи и выборки и управляемый формирователь 5 импульсов формирует тактовый импульс записи (моменты времени т, и t ) . Состояние выхода 27 соответствует диаграмме 27 — I. Операции записи и выборки осуществляются относительно разных ячеек 13 памяти.

Устанавливаются несовпадающие коды адресов записи и выборки, и управляемый формирователь 5 импульсов формирует тактовый импульс записи (момент времени и t ) . Состояние выхода 27 соответствует диаграмме 27 — 2. Происходит потеря информации, которая должна быть записана в данную ячейку 13 памяти.

Устанавливают совпадающие коды адресов записи и выборки и управляемый формирователь 5 импульсов не формирует тактовый импульс записи (моменты времени t и t,). Состояние выхода 27 соответствует диаграмме 27 — 1. Запись информации в ячейку 13 памяти, из которой производится выборка, не происходит.

Устанавливаются совпадающие коды адресов записи и выборки и управляемый формирователь 5 импульсов формирует тактовый импульс записи (моменты времени t и t ). Состояние выхода 27 соответствует диаграмме 27 — 2. Так как вновь записанная информация устанавливается на выходах 43 и 44 устройства через время Т после смены кода адреса записи (время Т равно суммарной задержке прохождения сигнала через устройства 1, 5, 11, 14, 15, 16 и 18), то выборка ложной информации будет исключена, если считывание информации с. выходов 43 и 44 устройства будет производится после смены адреса выборки через время, большее Т .

Рассмотрим наихудший случай с точки зрения надежной выборки информации. Такая ситуация возникает в моменты времени t7 и t, когда почти одновременно устанавливаются одинаковые коды адресов записи и выборки и из-за «состязания» сигналов управляемый форм нрователь 5 импульсов формирует тактовый импульс записи (диаграмма 27-2). Так как запись информации происходит по переднему фронту тактового импульса записи, то через время Т после установления кода адреса записи с выходов 43 и 44 устройства возможна надежная выборка информации из ячейки памяти, в которую производится запись. Из-за ограниченного быстродействия электронных схем в любом устройстве памяти, в том числе и прототипе, необходима такая задержка между записью и выборкой, т. е. устройство обеспечивает надежное функционирование при максимальном быстродействии. Потери записываемой информации, возможные в моменты времени t и t (диаграмма 27-2) и т, и t (диаграмма 27-1) крайне редки и ими можно пренебречь. Основные потери записываемой информации происходят в моменты времени tz u t (диаграммы 27-1 и 27-2).

Запоминающее устройство с одновременным считыванием нескольких слов, содержащее матрицу ячеек памяти, регистр записываемых данных, регистры считываемых данных, дешифраторы адресов считывания, дешифратор адресов записи, регистры адресов считывания, регистр адресов записи, причем первые управляющие входы ячеек памяти каждой строки матрицы подключены к соответствующему выходу де лифратора адресов записи, информационные входы которого подключены к выходам регистра адресов записи, выходы которого являются входами адресов записи устройства, информационные входы ячеек памяти столбцов матрицы объединены и подключены к выходам регистра записываемых данных, входы которого являются информационными входами устройства, одноименные управляющие входы ячеек памяти строки матрицы объединены и подключены к выходам соответствующих дешифраторов адресов считывания, вхоi310899

19

22

75 фиа 2

А арес .юпасбг

Адрес

Дыдареа

7б

77- I! ! !

t(о тб "4 гб -б t !

z, zoic

Фаг+

Составитель С. Шу.стенко

Редактор T. Парфенова Техред И. Верес Корректор И. Эрдейи

Заказ 176349 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4!5

Производственно-полиграфическое предприятие, г. Ужгоро L, ул. Проектная,4 ды которых подключены к выходам соответствующих регистров адресов считывания, входы которых являются входами адресов считывания устройства, одноименные выходы ячеек памяти каждого из столбцов матрицы объединены и подключены к информационным входам соответствующих регистров считываемых данных, выходы которых являются информационными выходами устройства, отличающееся тем, что, с целью повышения быстродействия, устройство со- 1О держит блок формирователей импульсов, 6 блок сравнения и формирователь импуль сов, выход которого подключен к стробирующему входу дешифратора адресов записи, тактовый вход формирователя импульсов подключен к выходу блока формирователей импульсов, входы которого подключены к входам регистра адресов записи и к входам первой группы блока сравнения, входы второй группы которого подключены к входам регистров адресов считывания, выход блока сравнения подключен к входу разрешения формирователя импульсов.