Логический анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой технике, может быть использовано для контроля и диагностирования цифровых устройств и является усовершенствованием изобретения по авт.св. № 1091339. Целью изобретения является расширение функциональных возможностей за счет обеспечения локализации двух-, трехи четырехбитовой ошибок. Логический анализатор содержит счетчик I с исключенным нулевым состоянием, сумматор 2 по модулю два, регистр 3, элемент И 4, группу переключателей 5, элемент ИЛИ-НЕ 6, индикатор 7, установочный , синхронизирующий и информационный входы 8,9 и 10. Возможность локализации двух-, и трехи четырехбитовой ошибок обеспечивается тем, что при формировании в регистре двоичной суммы по модулю два номеров разрядов последовательности, содержащих логическую единицу, при помощи группы переключателей и элемента ИЛИ-НЕ из нее исключаются номера одного , двух, трех соответственно ошибочных разрядов контролируемой логической последовательности. Таким образом , локализация двух-, трехи четырехбитовой ошибок сводится к последовательной локализации однобитовой ошибки. 3 ил., 2 табл. (Л го (puei

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU 1311011 (51) 4 Н 03 К 13/00, G 06 У 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1091339 (21) 4016159/24-24 (22) 29,01,86 (46) 15,05 ° 87. Бюл. Ф 18 (71) Донецкий политехнический институт (72) О,Н.Дяченко (53) 681,3 (088.8) (56) Авторское свидетельство СССР

Ф 1091339, кл. Н 03 К 13/32, 1982. (54) ЛОГИЧЕСКИЙ АНАЛИЗАТОР (57) Изобретение относится к цифровой технике, может быть использова— но для контроля и диагностирования цифровых устройств и является усовершенствованием изобретения по авт.св. N - 1091339. Целью изобретения является расширение функциональных возможностей за счет обеспече— ния локализации двух-, трех- и четырехбитовой ошибок, Логический анализатор содержит счетчик 1 с исключенным нулевым состоянием, сумматор 2 по модулю два, регистр 3, элемент

И 4, группу переключателей 5, элемент ИЛИ-НЕ 6, индикатор 7, установочный, синхронизирующий и информационный входы 8,9 и 10. Воэможность локализации двух-, и трех- и четырехбитовой ошибок обеспечивается тем, что при формировании в регистре двоичной суммы по модулю два номеров разрядов последовательности, содержащих логическую единицу, при помощи группы переключателей и элемента

ИЛИ-НЕ из нее исключаются номера одного, двух, трех соответственно ошибочных разрядов контролируемой логической последовательности. Таким образом, локализация двух-, трех- и четырехбитовой ошибок сводится к последовательной локализации однобитовой ошибки, 3 ил., 2 табл, t

: 3 1 1 0 1 1

3 Ja«с

<" «:(тc Xl O (2) (3) (! (."- <». .+, Г:>) —. Я !.-. 1, — т (<",, ) — Ж т(-, / j

» ! Г> (! 1 (С(> + <». ! нием (э (ы) =Md, h;,l

1 = (3(,/ ) + г (7) Изобретение от»о сится Jc ((5«<«:-,.>o»ox технике, может быть г.:риме»и ««О;р(я наладки, ремонта H кантрол«: цlr< >рл.вых устройств и является усове IJ!HEJ ствованием изобретения по ссног»ому авт.св. Ф 1091339.

Целью изобретения являе ся рс(с(:((«рение функциональных возможностей за счет обеспечения локализации. двух-, трех- и четырехбитовой сщи(>ик

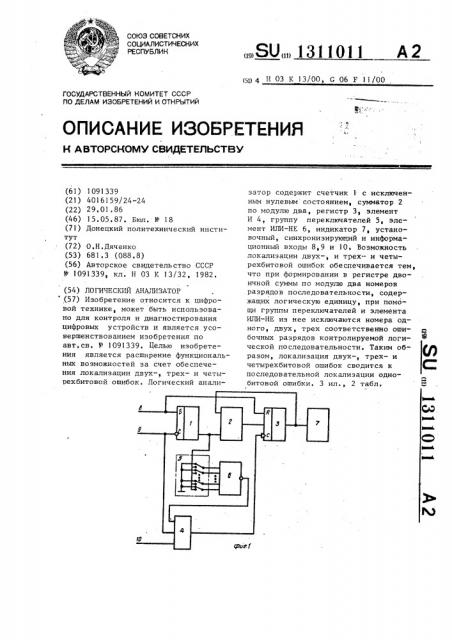

На фиг.! представлена фу»кци,н;..!.!— ная схема предлагаемого логическогo анализатора на фиг.2 — вариант реа-лизации двоичного с.тетчика с искл<>— ченным нулевым cocтоянием,* на фиг ... 3схема алгоритма поиска ошибки„

Логиче ский анализатор (<):иг,: ) содержит счетчик 1 с исклю-.ен«(ьт". левым состоянием, сумматор 2 IIО и.-дулю два, регистр 3., элеме« т И группу переключателей 5, элема»т

ИЛИ-НЕ 6 и индикатор 7, Позиция ."1»

8, 9 и 10 обозначены соответствс»«О установочный, синхро«визируl<>(Jr(Ié I! формапионный входы анализ ат О ра.

СЧЕТЧИК 2 С ИСКЛЮЧЕГП<ЫМ НуЛЕHЬ(Е со cTo5IHBPM содер?ки! (<(>иг, 2) и еpl (!-! Ã второй и третий элементы 1 ->П:. 1 : .

12 и 13, двоичный счет еик 1> и с - о:— ный триггер 15.

Логический анализатор работ;-.-;» следующим образом, Пере,п,началом работы в<-е т(ер;-ключа тели 5 разомкнуты (»и Од! и -I ç нь:-ходов счетчика 1 с исключен и:..:: (у.(с— вым состоянием не соец«!»е» .-. coо гвс-ствующим входом элеме»та И;11--(П; 6) . импульсом с входной клем и 8 с (:>тч> к

1 с исключенным 5(ус«евь>м < с>с <Оя«(<(см устанавливается в состоят>5(е 1". Ip.

ВЕРЯЕМУЮ ПОСЛЕДОВатспь тпгт«> JIO;Jна вхоцную клемму 10, »а Hx<»;rry! клемму 9 подают синхроимг«ульс.,: »(и;— ронизирующие ка>«<цый разряд »ропе...»-:— мой по следовательно сти

По фронту синхроимпульса r(polrcõ эдит запись в регистр 3,, а: ro clr,-r;r синхроимпульса — у=,э"..сп чае(5 = «(а (с >гтОЯНИЯ СЧЕтЧИКа С ИСК>Ч(>т(Е«Э:ii.!Ì --.,:,:(Е— вым состоянием.

Описанная последов атerп(п > с: г«-: а-зывается циклом работы àl>а-!изат<> .а

Состояние на выходе регисэ ра 3 (нулевой разряд регистра рас(с 1»т >иэаЕТСЯ ОТДЕЛЬНО) ОПНСЫ»аЕТСЯ У:, ((тс. .(Е С вЂ” .«Г!»:l! i:ОС.>Е«,.«>атЕ. H»OC>

З.»ачЕ»ИЕ (-! О РаЗРЯГ(а ПОС «<Е— («О«3 а Геxr J»EI oc x v. т сl (- (0 >

CO C (C(5IEJ! IP СЧ Е ТЧ ИКа (На (—,1 т(а т- Е

)5 Обс значает булевское сломоду.-ю qH;!, Сумм»рова:!»е J,«С СЬ Р ««!» КЕ i: Г>ОИЗБОДИТСЯ IIO МОДУ(TJJ

Сoc- ся»ие J .órlå«J<>x о разряда регист-!!ÿ 3 О! Исыва"= xc>l уравнением

Состоя«(ие первогo разряда регист3 or!Ere«!JHào сся у.,ав»с»ием! ДС Х . — СОС: O> !Jr! —: C-ie ".ТОГО ТРИГГЕ—

:1oc:(едс>ве«> ель»ост«> с Оп(ибка>н-..:..;". з «(рс„. с." . «(ить . в-!де

ПС < т (от>Э т т<Ь «О< т, -> - !.-р а—

>! li (! 3 в xr i= -H l- H H » - .х т> а з р я ас -. 1, > >(р>(,т>т >-, (!o ((, ((. »o!I<.«а О циб.а, т, (. «! -. ! О (. r О гь 3 r! J I в э«и се> л HI I C u ! ;> (" т>(т! c>!«o«> апитl (J ) . "1o "тто 3 д>1тт тсумм»рова»ис -«ро: схo;(ит тс> зле:,-;, (;(!, <, -.СОТ< т>к "- тт>И!<ИМЯЮ» Э»а = Е— ! (! !

; . ",,;-,. ПО ..: <С:«, Са;(:, Рая»ЫМ (>аМ О(lx!f. О(r.". l.(>. ".. ""!>P >С!В, Кром тзт О, C > > J>1 J>J I 1 P З <Э а -! И > а ",; C П (O I (CX O;., Гi < О

Ill! , ll JJ i JJ,-,i; > Ра;. -.т.(И<= »Ч«(т.! С.> 3 J, 5 >тo.; >

>( т .; Тс т «>»oc (:I с 1< ., ;! OJ< тчак);.

1311О

rpe I = i< + iz +, ° ., + i„;

1 — номера разрядов с ошибкой;. п — количество ошибочных разрядов.

Иэ формул (5), (6) вытекают следующие выводы: любая ошибка нечетной кратности будет обнаружена. Это следует иэ того, что в случае ошибки нечетной кратности

10 к К K

X х,„. =Q(х„„.+ 1) Qх„-, jag (8) т,е. к

+m х1, =1

15 где суммирование происходит по индексам i, равным номерам ошибочных разрядов.

В случае ошибок четной кратности или отсутствия ошибок к к, х„; +Kx« = О, (9)

l=1

Из формул (5) — (9) следует, что, 25 если сумма у(с ) + у (o() + + (с ) +

+ g (g) равна единице, то произошла ошибка нечетной кратности; если эта сумма равна нулю, .то произошла ошибка четной кратности или ошибочных разрядов нет, Таким образом значения нулевого r и первого r, разрядов ре-. гистра 3 позволяют судить о четной или нечетной кратности ошибок.

На фиг. 3 показан порядок локали- зации ошибочных разрядов последовательности длиной k < 2, для которой должны быть известны (r+1) контрольных сумм (одна из них соответствует разомкнутому положению всех переключателей, r остальных — каждому иэ переключателей в замкнутом положении при разомкнутых (z 1) остальных). 45

Условные обозначения на фиг.3:

А,В,С вЂ” двоичные суммы по модулю два соответствующих показаний индикатора 7 и соответствующих контрольных сумм; 50

7(з), Б(1) — 1-й разряд двоичных чисел (7,S);

У() — 1-й разряд двоичного числа (7); у, S — номера локализованных ошибочных разрядов контролируемой последовательности.

Возможность локализации однобитовой ошибки (т ° е. указания ошибочно11 4

Fo разряда последовательности) обеспечивается тем, что состояния двоичного счетчика 1 с исключенным нулеBblM состоянием егo — вйходов выходы счетчиков 14,15) соответствуют номерам разрядов контролируемой логической последовательности.

При этом в г разрядах г„ ...г„ регистра 3 записана двоичная сумма по модулю два номеров разрядов последовательности, содержащих логическую единицу.

В случае однобитовой ошибки полученная сумма будет отличаться от правильной на состояние .счетчика, соответствующее моменту ошибки, т,е. на номер ошибочного разряда, кроме того, сумма по модулю два состояний . нулевого г и первого г разрядов регистра 3 будет отличаться от суммы известных правильных состояний этих разрядов.

Осуществив сложение по модулю два полученного содержимого регистра 3 с известным правильным, получают номер ошибочного разряда в последовательности.

Локализация однобитовой ошибки (согласно фиг,3) осуществляется следующим образом. После первого цикла работы анализатора, который производится при разомкнутых переключателях, полученное показание индикатора 7 суммируют по модулю два с соответствующей контрольной суммой. Анализ нулевого и первого разряда полученного числа А покажет, что произошла ошибка нечетной кратности, Проверив бит последовательности с номером А (нулевой разряд числа А при этом отбрасывается), убеждаются в том, что этот бит ошибочен, т.е. действительно имеет место только один ошибочный бит.

Возможность локализации двух-, трех-, четырехбитовой ошибок обеспечивается тем, что при формировании в регистре 3 двоичной суммы по модулю два номеров разрядов последовательности; содержащих логическую единицу, при помощи группы переключетелей 5 и элемента HJIH-НЕ 6 иэ нее исключаются номера одного, двух, трех соответственно ошибочных разрядов контролируемой логической последовательности. Таким образом локализация двух-, трех-, четырехбитовой ошибок сводится к последова(" ) ()1 1 с тельной локализации О,.".n6!>= 01!О. . ошибки.

Если замкнут -й нарек.па:aòñ.!J. (остальные должны быт разо-(кн; т(,1)!. то при формировании в регистре 3 двоичной суммы по моду:тю два но (0ров битов последова .е lf I(00? If) c(3-держащих логическую едини«, иэ не исключаются все номера битов пое:(едовательности, H 1 м )зазр?(г-,:. ко ор пх содержится логическая единя l t.

В качестве примера лскап: .!„=i;.Гн ошибочных разрядов рассматр..наю г л-.:-кализацию однобитовой и дву;:6«т»)",." ошибок (табл. 1 и 2,) .

После первого ц?(и((((ра(:0 "-,! 0)ь зятОря получа(ОТ TJH(Io .", 0)t(13lH (у

ЛЕВОГО И ПЕРВОГО РЯЭРЯ;(Е гэ -ОР: . () показьпзает, (то про((зоп(Г(а Гп>н.бк: четной кратности — сумма lto мо-(, два этих разрядотт в,-т -„-а нул(() >, ) ) »з)1. сывая нулевой раэр? д (Hc?(;)

ВаЯ РаВЕНСтВО (7),: (Ог(.-:а. ;;т

А=Т= + г)

ГДЕ 1. — НОМЕ)3c. ОПН(бГЧ 3(:..

Р а 3 Р Я, -.> (3

Так как J.» 4-?,, то > -", О, СОГЛаСНО фИГ, 3, г .. -- Л 1((3..-(ЬП :-ется 1 переключаге:1-»,, пв! . м разряд числа Z такой, ч го Х; т,:

После проделанно. 0 T(B))cKT ю . !.:J( и erne одного цикла р;.(!)oòû а!.а, ";,".,- .: ра номер од!Io>i из;t(!inoк и(),.?)и)-чается из суммы, ): n. ó-(а е.-.,- . ре 3, номер;тругай 00 -=,0? C(T получен (oe число В бу:ет г к;(! номер Одного из ()п(ь(0(,н((т( номер рругого ош«60- но. и р (:= р!. >(Г дет равен Z + В.

Если проверка ра.»р!i i. 1> ег Г тельности покажет,! )то э,а !.Яэ):.:, Верны, то это зн» (и „-. го:: .(О(, (. вательности более четывсх (: битов; если о пибоче(> они((«э,":!у?( проверяемых разря„си, -тс; oзна ЧТО В ПО СЛЕДО?)Ят»- . !J>((OCT I - «1 ." >(В(бочных бита (в "(c Г.. у (а(0 . г!»:(,.)(ь(> три нелокализован«ы:; 0((!(16(3)(ип. : да локализую: ся а! Я!(0«и но 03 6 ( вой ошибке), Особенность(о -(ока i (зац(»« товой о)пибки яв:(яе- c;(.-o, т(т ) пючатели замыкаются последов» ге,".1; 0

Один 3 я дг)уt им нячl(:»а?(н е >)в 0(И ПОСЛЕ КажДОГО ПЕ 3(=O .Ë,.)cieи(Я Г.Р0-::;— водится цик.i работы Г(. !!Jзат<)ра пе!.Г: (()тт 1- 11. -, . 13, >е, ! .(.>(;г(>Top! (,:)1,:, > Г(!1ИЧЕ(.; (;г (! .р(тМЕ тот С ЛС:)6:13((;

;::1H 0(ПИб ЕЧНЬ>Х б«тап — КО : -t>(j)==x (трет() ошибочных .; ) (Га (T.З Я—

Г !та 0 гтнп !." 3 б",-,-, о.-- g?же э;)ка:IH30?! Н, ° >.РН Е ((В 0)(Г(-((. >НЬ(Х

> Ст. ((>На?(O СЕ> II>:)>:3ÕO T?

i!(-, ГJ) т Ticficc! де:-.((тl!!»i.:

:--»Гl)яетГя д л -(0Â з; иэа . ! . j) -(- -"х -oпlибо ill>;Iх б (тс)1;.

:)п», бонн:,(E(бH;:..31(?:ере <0;,я (г?(О.: е".()-(? ности дей т)>I!,I

6«70.i, Ic а -". т к тo« tio ко- овал

IlJiH О T)TTO Го а 11 )/11 т к ?o! по=которая

Ti;(r): -1 н(>(-: = нн! (- 1;»(д.,т-, това

". 01. 11! то(1. К() :O J(Ò) O. I c!(I.Л?(СУ (i! (! I. Н 01 :! i ) П O К Л !.l :3 1 З q> I I!:;;, (. 0 Г Г И . О. 0 бит;-..

1 (1((! 6 т.-., 3! f :. Г т) а; 0 J (а.т: -, l 3 0 ц я (" ((:гт (>1! >: .. >(! () (3 1 К:т(ЭЧЯП)тел И 3

Г !(О-((>) ". l,i! l3" 0i 1»!)OЧ I (X (i -) Гt)1:. 1 130 .>МОЖНО С: т-, .-Iol;a

>г )г)НН;-; 0?(«(1 ((3 (Е . Р -X. На«РИ (ЕР., г>гг=г >(>1!> г, )i> (13 1((1>(ЯЛ;! )Онc1 ГT> г„. НЕЕ- :,:эй .- тр:. " !»й и: гc)3 ый, г

i(6(т (--; 2, .:- Г б«ар ж« i .. и .и

;-! т,:-, г-,: T(>6;и-г Г,;>)1> i ";;.),> .пи>б—

l, г )-3 уь);;, i(i6"" ., l, - i ..- О,): 06— .--="! -" ! -(,;,,-! !! »О", т - п.10 "!) pe:.— !.l.. . г" 1" )Эг

-.с ..TTЕ 01 C н г->

1(i !1 „;1,, i 11 (;,! (.(О; (,.!!,; . .."..:() !;: !0 I3 !.

1I(-. (:I! i . (;1(i (:::l В Я i !! 1- .: т(;! . 0 ()):: . т !!1, l .;- )у! .:::. ку г", )-,, г!. г т—

;КГIT;ci" с

6 . >!J 106 IТО 13() l! 1г!" ():,;"

: .1. -хб (-,.01 е Р 1! I> (:»:.» и:, ), !) ", ((;(Ь T (c-. ),.(;)3 ?(ОК ", Iт(з ((НИ ЦБ УХ 0 ПИ, c«,ã;. би ггз?3,, (той T!!:!,ü особеп

T.(Э .:: 1 Н, (!(>1!i т ..М((! 0 >(И i » . 3Я, " JT . i H У ж (- тl (1 =; а:: И .1 (: 13 а! ..и ЫХ -3 .) г Е (1 О тт (:;iTl ) 1! (Ь:КЯЕ"., — >" П ЕВЕт.-:тЮЧа), >., 3 (., т! - З 3(). -(!!-„--11) >» 1 И г!," С! I> Эc! . ж(> .;!О .Я) T! 3 гз?3 c>IIНГ) 1 0

; -тнГ: 0 бит:- ра(3(:1:-»у.".ю, тэ к пе>1311011

Формула изобретения

Логический анализатор по авт.св, 1! - 1091339, отличающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения локализации двух-, трех- и четырехбитовой ошибок, он содержит элемент И-НЕ и группу переключателей, подвижные контакты

Таблица I

Состояние регистра (фактич.) Состояние счетчика, .h х хЗ х х, Последовательность с ошибками

Состояние

Входная регистра (эталон после" довательность с

I т2 1

Гф Г3 Г2 Г1 Го

I 1 0

0 О О

0 0 0

1 1 О

0 0 0

I 1 О

1 I 0 I 1 I

1 001

001 1

П римечание, I 0

0 О

1 О

1 0 1 О

О О

1 О

0 О 0

0 О О

О О 1 1

0 1 О О

О 1 О

О 1 1 0

0 1 1

) 0 О О

1 О 0 l

1 О 1 0

1 О I 1

1 1. О 0

0 1

1 1 1 0 которых соединены .с входами элемента KIH-НЕ, выход которого соединен с третьим входом элемента К, замыкающие контакты группы переключателей подключены к соответствующим разрядным выходам двоичного счетчика с исключенным нулевым состоянием,, размыкающие контакты группы переключателей объединены и подключены к !

О шине нулевого потенциала, 0 0 О i 0 0 0,0 1 0

0 0 О 1 О 0 0 0 1 0

0 0 0 1 О 0 О I 0 0

О I О 1 I 0 I I О I

О О 0 0 1 0 0 I ! д I 1 О О 0 I 0 1 0

О 1 .1 О 0 0 1 0 0

1 1 1 О 1 1 I 0 1

О 1 1 l 1 0 1 0 0 1

0 ! 1 1 О I 0 0 I

О 1 1 1 l О 0 0 1

1 0 I 1 О I О 0 О О

1 О 1 I О 1 0 О 0 0

0 I 0 1 О 1 1 О !! О 1 0 1 1 0 0 1

) )1)n)) Таблица 2

ВходПослеСn стоянHP счет чика

Со стояние

Со сто я ние

Примечание регистра (фактич,) доваТЕЛЬ» ная регистра (эталон) НОС" ледо

НОСТЬ

) Х,! Х (ва-! тельс ошибг) 0

f ность, ка))и

)(" е

О О О 0 1 О С: О O i О О 0 О .. 0

0 0 О О 0 1 С Î 0 1 О О О 0: О

0 0 0 О 1 1 О О 0 0 1 О О О О О

0 1 О 1 О С О О 1 1 О 0 Г) I О

0 О 1 О 1 О О О 0 О О I С ) О

1 О О 1 1 О ) О О С О О 1 () О

О! О С О . О . 1

О О

1 1. О

1 ) ) 0 О О

1 1 О О С О

1 0 1 i О О

О 0 1 1 О 1! 1 С

О О

О О 1

1 О 1 1 1

0 1 (: 1 1 О

1 С О

1 0 1

1;) 1 0 1 1 С

0 1 О .). !

О ) О 1

0 О ) О

О

0 С С 1 О С (O

O 0

0 О

О 1 О ) С О

1 О О 1 О

1 0 0 i 1 О

1 i 0 ) ) 1

1 О 1 0 О О

О! О О О О 1 О 0

1 О 1 ) 1

1 0 1 О 0 О

1 О ) С 0 1

0 О 1 0 1 O

1 О О 0 О 1

О О О О ) 0

0 0 О О 1

0 1 О 1 О О

О О 1 ! О l О О О

О 1 О 1 О 1 О О О 1

О О О О ) С С С О 1 О О G 1

О С 3 О С О О 1 О

0 О О 0 1 О 1 О О О

О С О О 1 О 1 О О О

О О 0 О 1 О i О О О!

З! !О11

12

Продолжение табл.2

Входная

Состояние регистра (фактич. ) ПослеСостояние счетчика h

Со стояние регистра

{эталон) римечание довательность хЗ "

rz r< r0 r< Г3 Г Г1 с ошибками о

О 1 1 О.!

+1 О О О

О О О ггоследовательность

О О О О О О О 1О O О

О О О О О О О О О О

О О О ! О О О О О О О

О 1,О О ! О ! 1 О О О

О 1 1 1 1 О 1 O ! О О

О О 1 1 4 О 1 0 О = О 1 1 1

Составитель С,Старчихин

Техред М,Ходанич

Редактор N.Áàíäóðà

Корректор A.Òÿñêo

19О2!55 Тираж 902 Подписное

БНИИПИ Государственного комитета СССР

IIo делам изобретений и открытий I13Î35„ Москва, Ж-35, Рауыская наб,, д.4/5

Заказ

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4