Адаптивная система обработки данных

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах и автоматизированных системах управления на основе мультипроцессорных вычислительных систем. Целью изобретения является увеличение нропускной способности вычислительной системы. Данная цель достигается путем введения в процессоры 2 системы блока 9 регистров, элементов И и ИЛИ, элементов 8 коммутации, регистра 10 номера канала и схемы 11 сравнения. Пропускная способность системы при этом возрастает за счет согласования потоков заявок в блоке регистров, а также за счет обеспечения возможности параллельной работы процессоров по взаимозависимым заявкам. 9 з. i. ф-лы, 14 ил. (Л СО ГЧЭ ел со о: 15

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 6 06 F 15/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1,7

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3989509/24-24 (22) 16.12.85 (46) 23.05.87. Бюл. № 19 (72) В. М. Антонов, В. Н. Середкин, К. П. Тиханович и Е. В. Олеринский (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 742943, кл. G 06 F 15/16, 1980.

Авторское свидетельство СССР № 926662, кл. 6 06 F 15/16, 1982.

Авторское свидетельство СССР № 1241250, кл. G 06 F 15/16, 1984. (54) АДАПТИВНАЯ СИСТЕМА ОБРАБОТКИ ДАННЫХ (57) Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах и автоматизированных системах управления на основе мультипроцессорных вычислительных систем. Целью изобретения является увеличение пропускной способности вычислительной системы. Данная цель достигается путем введения в процессоры 2 системы блока 9 регистров, элементов И и ИЛИ, элементов 8 коммутации, регистра 10 номера канала и схемы ll сравнения. 11ропускная способность системы при этом возрастает за счет согласования потоков заявок в блоке регистров, а также за счет обеспечения возможности параллельной работы процессоров по взаимозависимым заявкам. 9 з. и. ф-лы, 14 ил.!

312596

55! зобрстш(ие относится к вычислительной ,» (ик», в ч:.стности к адаптивным мультиli HH1»ci орным сист»м<(м, перестраивающим

cD(1ю структуру в зависимости от заданных способов о(1р(1(1отки данных, и может быгь ярименс" (о D измерительно-вычислительных комплексах и в автоматизированных системах управления технологическими процессами, в системах автоматизации испытаний и контроля сложных объектов и в других подобных системах. !!елью изобретения является увеличение пропускной способности системы при обработк» взаимозависимых заявок, за счет введения возможности наралл»льной обработки таких заявок и vivl»llblllcllll)l времени простоя процессороз в посл»;.(с:в<этельном режиме работы системы.

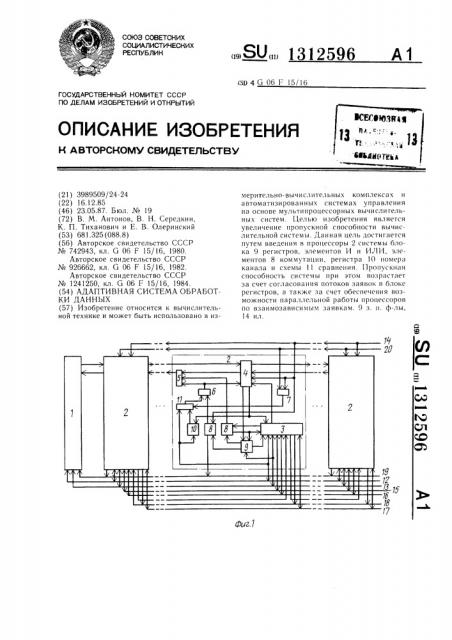

На фиг. 1 представлена схема предлага»мой системы; на фиг. 2 — — функциональная схема операционного блока; на фиг. 3 функциональная схема блока коммутации; на фиг. 4 -- функциональная схема элемента коммутации и блока регистров; на фиг. 5--функциональная схема арифметико-логического блока с временной диаграммой его работы; 113 фиг. 6 (11ункциональная схема блока обмена с врем»иной диаграммой его работы; на фиг. 7 — функциональная схема арифметического элемента коммутации; на фиг. 8 — — функциональная схема интерфер»йсного эл»M»í I а коммутацHH, входя(цего в состав блока обмена; на фиг 9 — функциональнаяя с хс ма блока интерфейса; Id фиг. !0 14 — блок-сх»мы à ll 01Ièòìîâ работы процессора cvстемы.

Адантиьч(ая система обработки данных со(1»р>кит блок 1 памяти, процессоры 2, каждый из которых содержит операционный блок 3, блок 4 коммутации, первый 5 и второй 6 элементы ИЛИ, элемент И 7, два элемента 8 коммутации, блок 9 регистров, регистр 10 номера канала и схему 11 сравнения.

Сист»л(а имеет и(нну 12 адреса, шину 13 данных, шину 14 задания режима, шину 15 сигналов выдачи, шипу 16 сигналов приема, шину 17 сигналон занятости, шину 18 сигна IoD D

Ои»р((ционный блок 3 содержит арифметико-логический блок 21, дешифратор 22, с гетчик 23 команд, элемент ИЛИ 24, блок 25 памяти, блок 26 обмена, блок 27 интерфейса, буф»рный 28 вход, вход-выход 29 адреса, вход-выход 30 х, вход-выход 31 признака выда IH, вход-выхог(32 признака прие111, первый 33 и второй 34 входы запуска, вход 35 признака захвата. вь(ход 36 признака о в»та, ьыхо<1, 37 признака запроса, входи>:.хо(38 признака занятости, вход 39 при на«» пр((»л(а, выход 40 опроса и выход 41

; ч1Р а П(»1(н Н .

Бло«:, коммутации содержит пять эле ;»IlaoH И -!2- — 46, четыре элемента 1-1Е 47—

50, элемент ИЛИ 51, вход 52 разрешения, информационный вход 53, задаю(ций вход 54, вход 55 запроса, выход 56 запуска, вход 57 обращения, выход 58 разрешения, выход 59 записи и выход 60 запроса.

Элемент 8 коммутации содержит два элемента И 61, два элемента НЕ 62, первый 63 и второй 64 входы, первый 65 и второй 66 выходы.

Блок 9 регистров содержит два счетчика 67 и 68 адреса, два дешифратора 69 и 70 адреса, счетчик 71 заполнения, регистровый накопитель 72, входной 73 и выходной 74 регистры, вход 75 записи, вход 76 считывания, выход 77 «Заполнен», выход 78 «Пуст», информационный 79 вход и информационный

80 выход.

Арифметико-логический блок 21 содержит регистр 8 микрокоманд, формирователь 82 синхросигналов, дешифратор 83, арифметический 84 элемент коммутации, приемо-передатчик 85, регистр 86, регистрову(о память 87, сумматор 88, сдвигатель 89, регистр 90 состояния, вход 91 кода микрокоманды, вход 92 запуска, вход-выход 93 данных, вход-выход 94 признака выдачи, вход-выход 95 адреса, информационный 96 выход, выход 97 сигнала исполнения.

Блок 26 обмена содержит регистр 98 микрокоманд, дешифратор 99, формирователь !

00 синхросигналов, элемент ИЛИ 101, элемент И 102, элемент HE 103, арифметический элемент 84 коммутации, интерфейсный элемент 104 коммутации, три приемо-цередатчика 105 — -107, коммутатор 108, регистр 109, вход 110 кода микрокоманды, первый 111 и второй 112 входы внешнего запуска, вход

113 внутреннего запуска, второй вход-выход

114 данных, второй вход-выход 115 признака выдачи, второй вход-выход 116 адреса, буферный вход 1! 7, первые вход-выходы адреса 118, данных 119, признака выдачи 120, вход-выход 121 признака приема, выход 122 захвата, вход 123 разрешения захвата, выход 124 приращения адреса.

Арифметический элемент 84 коммутации содержит два элемента И 125 и 126, элемент

HE 127, элемент ИЛИ 128, первый 129 и второй 130 входы, первый 131 и второй 132 входы-выходы и выход 133.

Интерферейсный элемент 104 коммутации содержит два элемента И 134 и 135, элемент ИЛИ 136, элемент HE 137, два ключа 138, первый 139 и второй 140 входы, первый 141 и второй 142 входы-выходы, третий 143 вход и выход 144.

Блок 27 интерфейса содержит триггер 145, четыре элемента И 146 — 149, два элемента НЕ 150, два ключа 151, вход 152 захвата, вход 153 признака захвата, выход

154 признака ответа, вход 155 признака приема, выход 156 разрешения захвата, входвыход 157 признака запроса и вход-выход

158 признака занятости.

1312596

Система работает следующим образом.

Работа системы определяется сигналами на шине 14 задания режима и шине 20 задания приоритета. В зависимости от значений этих сигналов в системе организуется один из режимов работы.

1. Режим параллельной обработки независимых заявок (фиг. 10). Исходное состояние: все процессоры 2 свободны, блок регистров пуст, сигнал на шине 14 задания режима равен «1», сигнал на шине 20 задания приоритета равен «О».

В этом случае каждый процессор 2 выдает сигнал запроса. Этот сигнал в процессоре 2 формируется операционным блоком 3 перед началом работы (или после окончания алгоритма обработки выборки). С выхода опроса блока 3 этот сигнал проходит на первый вход второго элемента 8 коммутации, на его первый выход (так как на его втором входе присутствует сигнал, пришедший с выхода «Пуст» блока 9 регистров) и поступает на вход первого элемента ИЛИ 5. На второй вход элемента ИЛИ 5 в параллельном режиме поступает сигнал от блока 4 коммутации, формирующийся из запросов последующих процессоров 2.

Объединяясь через элементы ИЛИ 5 процессоров 2, все запросы поступают на вход запроса блока 1 памяти. По сигналу запроса блок 1 выдает с адресного входа-выхода и входа-выхода данных код номера канала и код выборки соответственно, которые устанавливаются на шине 12 адреса и шине 13 данных. С выхода разрешения блока 1 памяти выдается сигнал разрешения.

Сигнал разрешения в параллельном режиме последовательно проходит через блоки 4 коммутации процессоров 2, анализируя их приоритет, и включает наиболее приоритетный процессор 2. Приоритет процессоров 2 в данном режиме повышается по мере возрастания их номеров. Поэтому сигнал разрешения, пройдя через блоки 4 коммутации всех процессоров 2, включает в работу последний процессор 2. Включение осуществляется сигналом, поступающим с выхода блока 4 коммутации на первый вход запуска блока 3. При этом в блок 3 считываются с шины 12 адреса и шины 13 данных коды номера канала и выборки. Одновременно код номера канала записывается в регистр

10 номера канала, снимается сигнал опроса, поступавший с выхода опроса блока 3 (т. е. исчезает запрос данного процессора 2), что служит разрешением включения в работу предыдущего процессора 2.

Так происходит начальное включение в работу (загрузка) каждого процессора 2.

В данном режиме включение процессора 2 в работу производится только при условии, что на входе разрешения блока 4 коммутации процессора 2 есть сигнал разрешения от предыдущего процессора 2, а на входе запроса отсутствует запрос от любо5

55 го последующего процессора 2. Тем самым создается повышение приоритета процессоров 2 по мере возрастания их номеров.

Записанный в регистр 10 код номера канала поступает на вход схемы 11 сравнения.

Так как схема 11 сравнения не включена из-за отсутствия на ее входе разрешения сигнала от элемента И 7, то в данном режиме регистр 10 никакой роли в работе процессора 2 не играет.

По номеру канала, считанному в операционный блок 3, определяется программа обработки заявки. Так как длительность обработки, в общем случае, является величиной произвольной, то произвольной (случайной) будет и последовательность включения процессоров 2 в работу по мере их освобождения. Тем самым обеспечиваются непрерывность работы всех процессоров 2 и минимальность их простоев.

Блок-схема алгоритма работы процессора 2 в режиме параллельной обработки независимых заявок показана на фиг. 11.

2. Режим параллельной обработки зависимых заявок. Исходное состояние: все процесоры 2 свободны, блок 9 регистров пуст, сигналы на шине 14 задания режима и шине

20 задания приоритета равны «1».

В этом случае начальное включение (загрузка) каждого процессора 2 осуществляется, как и в первом режиме, сигналом с Bblхода опроса операционного блока 3. Отличие заключается в том, что в каждом процессоре 2 включена схема 11 сравнения сигналом с выхода элемента И 7.

Запись следующей заявки в процессор 2, занятый обработкой выборки какого-либо канала, осуществляется следующим образом. Этот процессор 2 пе выдает своего запроса к блоку 1 памяти. Но запросы к блоку 1 могут прийти от другого (других) процессоров 2. При этом блок 1 выдает на шину 12 адреса и шину 13 данных очередную заявку. Так как шина 12 адреса соединена с первыми входами схем 11 сравнения всех процессоров 2, то в каждом процессоре 2 происходит сравнение выданного на шину 12 адреса кода номера канала с кодом номера канала, записанным в регистр 10 номера канала при включении процессора 2 в работу, Если эти коды в данном процессоре 2 совпали (это значит, что поступила выборка того же канала, который обрабатывается в этом процессоре 2), то схема 11 сравнения со своего выхода выдает сигнал, который через элемент ИЛИ 6 поступает в элемент ИЛИ 5 и на информационный вход блока 4 коммутации, являясь соответственно сигналом

«своего» запроса от данного процессора 2 к блоку 1 памяти и признаком режима параллельной обработки зависимых заявок, блокирующим сквозное прохождение через бпок 4 сигнала разрешения. Таким образом, этот сигнал превращает данный процессор 2 в процессор с наивысшим приоритетом.

13

Сигнал с выхода разрешения блока 1 памяти (он выдается с некоторой задержкой относительно выдачи заявки из блока 1), пройдя все предыдущие процессоры 2, поступает па вход разрешения блока 4 коммутации данного процессора 2 и инициирует появление на выходе записи блока 4 сигнала записи, поступающего на вход записи блока 9 регистров; этот сигнал осуществляет запись в блок 9 кода выборки с шины 13 данных. При окончании передачи заявки по шине 12 адреса и шине 13 данных сигнал на выходе схемы 11 сравнения снимается.

Таким образом, в системе осуществляется фиксированное распределение зависимых заявок по процессорам 2 и тем самым обеспечивается строгая последовательность обработки выборок одного канала. В то же время в системе нет строгой привязки номеров каналов к конкретным процессорам 2, т. е. фиксация распределения заявок существует только при появлении фактора опережения: во всех остальных случаях распределение остается достаточно произвольным, так как учитывается только приоритетность процессоров 2 (как и в первом режиме).

Это значительно повышает живучесть системы и сокращает затраты времени и оборудования на организацию распределения заявок.

После записи кода выборки в регистр блока 9 регистров процессop 2 работает следующим образом.

По окончании алгоритма обработки предыдущей заявки блок 3 выдает сигнал опроса во второй элемент 8 коммутации. Так как сигнал «Пуст» теперь отсутствует (в блоке 9 находится выборка), то второй элемент 8 коммутации выдает сигнал, поступающий на второй вход запуска блока 3, для запуска блока 3 и на вход считывания блока 9 регистров. При этом выборка передается с информационного выхода блока 9 в блок 3 для обработки.

В блоке 9 регистров может находиться одновременно несколько выборок одного канала. Считывание их из блока 9 осуществляется последовательно в порядке их поступления. При полном заполнении блока 9 выдается сигнал с его выходя «Заполнен». Этот сигнал проходит через первый элемент 8 коммутации и поступает в виде сигнала блокировки на шину 19 блокировки, обьединяющую выходы блокировок от всех процессоров 2. Появление сигнала блокировки ня входе блокировки блока l памяти запрещает считывание заявок из блока 1 и тем самым исключает возможность появления фактора опережения в системе при заполнении блока 9 регистров какого-либо процессора 2.

Простои процессоров 2 системы из-зя возникающих блокировок несколько снижают ее пропускную способность по сравнению с первым режимом.

12596

1О 5

6

Ллгоритм раооты процессора 2 в режиме параллельной обработки зависимых заявок показан на фиг. 12; алгоритм записи заявки в процессор 2 в этом режиме представлен на фиг. 13.

3. Режим последовательной обработки заявок. Исходное состояние: все процессоры 2 свободны, блок 9 регистров пуст, сигнал на шине 14 задания режима отсутствует, сигнал на шине 20 задания приоритета никакой роли не играет.

В этом режиме во всех процессорах 2 блок 4 коммутации может организовывать связь только между двумя смежными процессор а м и 2.

В начальный момент в каждом процессоре 2 формируготся одновременно два сигнала запроса: во-первых, свободный операционный блок 3 выдает сигнал с выхода опроса, поступающий через второй элемент 9 коммутации на второй вход элемента ИЛИ 5; во-вторых, на втором выходе первого элемента 8 коммутации формируется сигнал (так как отсутствует сигнал «Заполнен» на выходе блока 9 регистров), поступающий через элемент ИЛИ 6 на третий вход элемента

ИЛИ 5 и на информационный вход блока 4 коммутации. Сигнал при работе в последовательном режиме постоянно поступает через элемент ИЛИ 5 на вход запроса блока 4 коммутации предыдущего процессора 2 до тех пор, пока не заполнится блок 9 регистров.

При поступлении сигнала запроса на его вход запрося блок 1 памяти выдает с выхода разрешения сигнал разрешения в первый процессор 2 и выдает заявку на шины 12 и 13. B этом режиме все заявки из блока 1 памяти последовательно поступают только па первый процессор 2, так как отсутствие сигнала по шине 14 задания режима на задающем входе блоков 4 коммутации запрещает сквозное прохождение через них сигнала разрешения.

Появление сигнала разрешения на входе разрешения блока 4 коммутации первого процессора 2 инициирует выдачу с выхода записи блока 4 сигнала, записи, который записывает в блок 9 регистров код выборки с шины 13 данных. Поскольку блок 9 теперь не пуст, то сигнал запроса, поступающий с выхода опроса блока 3 во второй элемент 8 коммутации, сформирует на выходе управления этого элемента 8 сигнал, который включит блок 3, а также передаст в него из блока 9 выборку, которую блок 3 начнет обрабатывать. При этом сигнал с выхода опроса блока 3 снимается.

B то время, как блок 3 выполняет первую часть алгоритма обработки заявки, сигнал запроса от первого процессора 2 сохраняется, поэтому блок 1 памяти продолжает выдавать заявки, которые записываются в блок 9 регистров данного процессора 2; эта передача заявок заканчивается при полном заполнении блока 9.

1312596

Форт za изобретения

Блок 3 первого процессора 2, выполнив первую часть алгоритма обработки заявки, выдает с выхода обращения сигнал обращения в блок 4 коммутации. Если при этом на входе запроса блока 4 имеется сигнал запроса от второго процессора 2, то блок 4 выдает с выхода разрешения сигнал, поступающий на вход разрешения блока 4 второго процессора 2.

Во втором процессоре 2 блок 4 коммутации сигналом с выхода записи передает в блок 9 регистров этого процессора 2 результат частичной обработки заявки (проведенной первым процессором 2) с шины !3 данных, куда он поступил из первого процессора 2. По сигналу с выхода опроса операционного блока 3 второй элемент 8 коммутации выдает сигнал с выхода управления (так как блок 9 регистров теперь не пуст), который поступает на второй вход запуска блока 3, а также передает информацию из блока 9 регистров в блок 3 для последующей обработки, т. е. для выполнения второй части алгоритма.

Этот режим наиболее эффективен при обработке выборок одного канала. Так как формирование сигнала запроса и прием информации в блок 9 регистров процессора 2 не связаны с окончанием выполнения части алгоритма, то существенно сокращаются простои процессоров 2 из-за неравномерности длин частей алгоритмов. Подобрав нужное количество буферных регистров, можно полностью исключить простои в системе.

Алгоритм работы процессора 2 в режиме последовательной обработки заявок показан на фиг. 14.

Коммутация сигналов, управляющих работой системы в нужном режиме, производится блоком 4 коммутации и элементами 8 коммутации.

Блок 4 коммутации (фиг. 3) управляется сигналом разрешения из предыдущего процессора 2, поступающим на вход разрешения блока 4, соединенный с входами элементов

И 42 — 44.

С выхода разрешения блок 4 выдает сигнал разрешения в блок 4 последующего процессора 2 при наличии на входе запроса блока 4 данного процессора 2 сигнала запроса от последующего процессора 2 в следующих случаях: при параллельном режиме обработки независимых заявок (т. е. при наличии на задающем входе блока 4 сигнала по шине 14 задания режима системы и при отсутствии сигнала «своего» запроса на информационном входе блока 4) — при подаче на входе разрешения блока 4 сигнала разрешения; таким образом, в этом случае разрешается сквозное прохождение сигнала разрешения через элементы И 42 и ИЛИ 51 блока 4 данного процессора 2 в направлении к одному из последующих свободных процессоров 2 с более высоким приоритетом; при последовательном режиме (т. е. прп отсутствии на задающем входе блока 4 сигнала по шине 14 системы) — при подаче на вход обращения блока 4, соединенный с входом элемента И 46 сигнала обрап)ения из блока 3 после осуществления этим блоком частичной обработки заявки.

С запускаюгцего выхода, подключенного к выходу элемента И 43 блок 4 выдает сигнал запуска на первый запускающий вход блока 3; это происходит в параллельном режиме обработки независимых заявок в том случае, когда в момент прихода на вход разрешения блока 4 сигнала разрешения на входе запроса блока 4 нет сигнала запроса от послсдуloщих процессоров 2, т. е. данный процессор 2 является последним (и, значит, няиболес приоритетным) из процессоров 2, выдавших запрос к блоку 1 памяти.

При последовательном режиме, я также при параллельном режиме обработки зависимых заявок поступивший на вход разрешения блока 4 сигнал разрешения проходит (при подаче на информационный вход сигнала «своего» запроса с выхода элемента

ИЛИ 6) через элемент И 44 на выход записи блока 4, чтобы дялсс в качестве сигнала записи поступить в блок 9 регистров для записи в него кода выборки с шины 13 данных.

Ня выход запроса блока 4 в параллельном режиме разрешается сквозное прохождение сигнала запроса от последующего процессора 2 с входа запроса блока 4 через элемент И 45.

1. Адаптивная система обработки данных, содержащая блок памяти и А процессоров, каждый из которых содержит . ti ðaöèoínûé блок, блок коммутации и перь; ». элемент

ИЛИ, причем входы-выходы адреса и данных операционных блоков каждого процессора и блока памяти подключен; оответственно к входам-выходам а;. .. д;:. ных системы, вход запроса блока памяти г, дK;lloчен к выходу первого элемента ИЛИ первого процессора, выход разрешения блока памяти подключен к входу разрешения блока коммутации первого процессора, первый вход первого элемента ИЛИ каждого процессора подключен к выходу запроса блока коммутации того же процессора, выход разреше° ии блоИИ иоии|уеассии t-ãà ороиессори (i=1, A — 1) подключен к входу разрешения блока коммутации (i+1) -го процессора, выход первого элемента ИЛИ с-го процессора (i=2, %) подключен к входу запроса блока коммутации (i — 1) -го процессора, первый вход запуска операционного блока каждого процессора подключен к выходу запуска блока коммутации того же процессора, выход обращения операционного блока каждого процессора подключен к входу об1312596 ращения блока коммутации ТОГО же процессора, задающие входы блоков коммутации всех процессоров подкл1очены к входу з-.дания режима системы. отличающаяся Toм, что, с целью увеличения пропускной спо< обности системы при обработке взаимозависимых заявок за счет введения возможности параллельной обработки таких заявок и уменьшения времени простоя процессоров в последовательном режиме работы системы, в каждый процессор введены второй элемент

ИЛИ, элемент И, два элемента коммутации, блок регистров, регистр номера канала и схема сравнения, причем входы и выходы признаков выдачи, приема, занятости и выходы признака запроса операционных блоков каждого процессора подключены соответственно к входам и выходам сигналов выда1и, приема, занятости и запроса системы, вход признака захвата операционного блока первого процессора подключен к входу запроса системы, выход признака ответа операционного блока i-го (i= l, V-- 1) процессора подключен к входу признака захватd операционного блока (1+1) -го процессора, первый вход элемента И каждого процессора подключен к первому входу первого элемс1гга коммутации того же процессора и входу задания режима системы, первый выход первого элемента коммутации каждого Ilpoцессора подключен к выходу блокировки системы и входу блокировки блока памяти, в каждом процессоре второй вход IlcpBok элемента ИЛИ подключен к первому выходу второго элемента коммутации, первый и второй входы которого подключены соответственно к выходу опроса операционного блока и к выходу «Г1уст» блока регистров, второй выход второго элемента коммутации подключсH к второму входу запуска операционного блока и входу считывания блока регистров, информационныс вход и выход которого подключены соответственно к входу данных и буферному входу опер;щионпогo блока, вход записи блока регистров подключен к выходу записи блока коммутации, выход

«ЗаПОЛПЕН» 6ЛОКа р гГИСтрОВ 1ЮдКЛЮЧСН К второму входу первого элемента коммутации выход элемента И подкл1очен к входу разрешения схемы сраьч<сния, первый информационный вход которой подключен к информационному входу регистра номера канала и адресному входу операционного блока, второй информационный вход схемы сравнечия подключен к выходу регистра номера канала, синхровход которого подключен к выходу запуска блока коммутации, выход схемы сравнения подключен к первому входу второго элемента ИЛИ, второй вход которо1о подключен к вгорому выходу первого элемента коммутации, выход которого подключен к второму выходу первого элемента коммутации, выход второго элемента ИЛИ подключен к информационному входу блока коммутации и третьему входу первого эле5

55 мента ИЛИ, второй вход элемента И каждого процессора подключен к шине задания приоритета си TOME I.

2. Система по п. ., отличающаяся тем, l1 o операционный блок содержит арифметико-логический блок, дешифратор, счетчик команд, элемент ИЛИ, блок памяти, блок обмена и блок интерфейса, причем разряды входа дешифратора подключены к соответствующим разрядам кода операции числового выхода блока памяти, разряды адреса перехода числового ьы хода которого подключены к соответствующим разрядам входа адреса перехоца счетчика команд, разряды кода микрокоманды числового выхода блока памяти подключены к соответствующим разрядам входа кода микрокоманды арифметико-логическо" î блока и блока обмена, буферный вход, первые вход-выходы адреса, данных, признака выдачи и вход-выход признака приема которого являются соответственно буферным входом, входами-выходами адреса, д3lkkkhlx, признака выдачи и признака приема операционного блока, первый, второй и третий выходы деп1ифратора подключены соответственно к входам разрешения записи адреса перехода, начального адреса и модифицированного адреса счетчика команд, счетный вход которого подключен к выходу элемента ИЛИ, первый и второй входы коlopolo подключены соответственно к выходу сигнапа исполнения арифметико-логического блока и к выходу приращения адреса блока обмена, вторые входы-выходы адреса, данHbIx и признака выда1и которого Ilogl;IIOBEны соответственно к входам-выходам адреса, данных и признака выдачи арифметикологического блока, информационный выход которого подключен к входу модифицированного адреса счетчика команд, вход на IBëüíoãо адреса которого подключен к входу выходу данных арифметико-логического блока, вход запуска которого подключен к четHLðòoìó выходу дешифратора, пятый выход которого подкл ючен к входу внутреннего запуска блока обмена, первый и второй входы внешнего запуска которого являются соответственно первым и вторы xl входа м и запуска операционного блока, выход счетчика команд подключен к первому адресному входу блока памяти, второй адресный и числовой входы которого подключены соответстве IHO и первым входам-вы одам адреса и данных блока обмена, вход-выход признака приема которого подключен к входу-Ekblходу признака приема блока интерфейса, вход признака захвата, выход признака ответа, выход признака запроса, вход-выход признака занятости и вход признака приема которого являются соответственно входом признака захвата, выходом признака ответа, выходом признака запроса, входом-выходом признака занятости и входом признака приема операционного блока, шестой и седьмой выходы дешифратора являются соотвстст1312596 венно выходами опроса и обращения операционного блока, выход захвата блока обмена подключен к входу захвата блока интерфейса, выход разрешения захвата которого подключен к входу разрешения захваты блока обмена.

3. Система по и. 1, отличающаяся тем, что блок коммутации содержит пять элементов И, четыре элемента НЕ и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И подключены к Входу разрешения блока, входы первого и второго элементов HF подключены к Второму входу третьего элемента И и к информационному входу блока, выходы первого и второго элементов HF. подключены к Вторым входам соответствующих элементов И, третьи входы которых подключены к входу третьего элемента НЕ, первому входу четвертого элемента И и задак>щсму входу блока. Выход третьего элемента j(L подключен к первому входу пятого элементы И, второй Вход которого подключен к четвертому входу первого элемента И, входу четвертого элемента 1(Г, второму входу четвертого элемента И и является входом запроса блока, выход четвертого элемента j-!Å Ilo,t,êëloчен к <ствертому входу второго элемента И, выход которого является выходом запуска блока, Tpcòий вход пятого элемента И является входом обращения блока, Выходы первого и пятого элеме!)гов И IIO;Lhëþ÷åíû к входам элементы

ИЛИ, выход которого является Bblxo,LO÷ разрешения блока, Выходы третьего и ч Tвертого элементов И являются соответственно Выходами записи и запроса блока.

4. Система по и. 1, отличающаяся тем, что элемент коммутации содержит два элемента И и д83 элемента HF, причем первый вход первого элемента И подключен к входу первого элемента Н(= и является первым входом элемента коммутации, второй вход первого элемента И подключен к входу второго элемента 1(F и является вторым входом элемента коммутации, Выходы элементов НЕ подключены к соответствующим входам ВТорого элемента И, выход которого является первым выходом элемента коммутации, вы.ход первого элемента И является вторым выходом элемента коммутации.

5. Система по и. 1, отличающаяся тем, что блок регистров содержит два счетчика адреса, два дешифратора адреса, счетчик заполнения, регистровый накопитель, входной и выходной регистры, причем входы прямого и обратного счета счетчика заполнения подключены соответственно к счетным входам первого и второго счетчиков адреса и являются соответственно входами записи и считывания блока, входы разрешения первого дешифратора адреса и входного perèñòðà подключены к счетному входу первого счетчика адреса, выходы признаков заполнения и равенства нулю счетчика заполнения являются соответственно выходами «Запо 15

55 нен» и «Пуст» блок», Выходы сч T÷HKOB ыдРСС3 IIOДК ЗЮ i(> ОД)l М соответствуK)ll!Hx L(Ill)t(j)p;)TO()013;3;Lрсс l, рызР>)ды Bblxo<(08 котОР!>1\ ИОДклк) !(il)>! к ))хо,«) 11 соответственно за циси и сч иты Вы !4 и я ()OTветствующих регистров регистрового ныкоПИТЕЛЯ, И))фОРМВЦИОННЫЙ В\ОД 13ХОДIIOCO регистра является информационным Входом блока, выход Bxo;Ll!010 pcãHñòð» подключен

K ИНфоРМ3ЦИ011140ММ В\ОДМ P(Гi)<;Tj)OBOI

H 3 KÎIIi4т<,lЯ, ин фОP . 1131(140H Ii ый Вы хс)д котОРО г0 подключен к иticj)0()xi<3LLHoltltO)tx Входх

BI>IX0. LHÎÃÎ ре! НК(тр(). ВЫ. ОД VOTOрС>ГО яВЛя(тсН информационным Выходом блок;3.

6. Системы I!0 Il. 1 или 2, от.it, <с)((эщ(.>я"я

ТСМ, ЧТО Ы()!)ф .1<>ÒIIК(1 — ГIОГII !ССКИЙ ()10i. <. 0— держит рсг))стр )и к() окох!(3 д, фс)р и и ров»тс,1 b С И нх ро 14 Гll i. 1013,, !<. Ill)t(f) p >!TO();3 рп(4<)м(тически и элс мент ком мечтании.; 3t H(мси!средытчик, регистр, реги(тровую;!»мя > ь, сх мм3тор. сдвиг»тель и регистр сост()HH)tя, приЧС.1 И))фОРX 3(L)IOIt)41>IИ 13XO;I, РС Гli(ГP, Xt tthj)0кОма))Д ЯВ;IЯ(.тсЯ В хо !Ом KO, Ii) м))кР()ко)11) tl. Lû б;IOK13, Вход за пс с)сы фОр м и рОВ>)т(ля (H I I x j)0СИГllа, !ОВ ЯВ, 1>Я T(. Я ВXО.LОМ Зilн > СК(3 (1,!ОV;1, П С Р В bi и И В ТО Р 0 i ) В Ы Х ОД Ы ф 0 Р М И Р (1! 3 i 1 (CI Я

СИ!)ХрОСИГНЫ;!С)В ПО IK.i)0>10141>i СО(1!Ч)с !С! ВСIIHO к синхровходым регистры микроком»)11 и,)сшифраторы, информ»)lиоиный Вх()д vOT(>j)ol подключен к выходу рс)ч)стр» микроком»1, L и Bx0;L> и(. Ре)ОГО сл)1! ;Iсмо Го i х м хl»)ОРы, )E(Pвый и Второй Вы;0;ц l,;(ï>lôð»òop» !10;iv.lloч с н ы к с 00 1 Б с т с т В >Гк ) 3 ц и м B x o;3» м 13 (1 H (1) x (. T H . чсского элемсн Га коммуTL) ILIitt. )ц рвый il !3) с>РОИ ВХОДЫ-ВЫХОДЫ КОТОРОГО ЯВ.IЯ)ОТ<. Я 13XO, (3М И - В Ы Х 0 Д 3 М И . 4 Н 14! >l Х l t l t P I t » i i 13 l(» 13 ) >I, L It < H t

О. 1 0 K 3, It bt X O J, » Р И ф "i (. Т И > I (. С КО Г 0 -. Г (. " 1 (. l i T 3 коммм Гыции подкГIK) 40)l к стробиj)(to)!Гсх!

Входх приемо- перс ", »ò i it)(», нс р Вы и 1)х()дВЫ ХО,! KOTOPOCO Я В. i Hi. ГСЯ !3 XO L()>t - Hl>1 X();!0 %t

3ДРЕС» 0,)ока, Ы i> i OPOII ПО.)К, IK)Ч(. ii К il0,)!30МСУ

HH+O0Xt3IL)tOI4H0XtX I)X<> L) -и)>!ХО.!Х 3;(ГИ TP!3. второй информ»циси)пый !3х<)д-13!>!x(i.ii ко) Op(>ГО ПОДК, К)ЧBii К it il фоi) Xi» !))(>1. :Н()(1 > l> X(i.lм выходу регистров(.il И3 мяти, к иф()р,l»ЦИОННОММ ВХОД > PC! HCT!>c3 СОСTOHI!)IH lt ВЫ \О.!

СДВИГ»те, lя, Инфо(1)1 подключен к В));<)Г!1 (х))мы c xl)t» l lj);!. (>»3>РЯД!>! ВХОД3 11(. P)3(,! (i СГI;l I IC >)()! (> К(>l >(> >I (i

ПОДKC) !0j 5I,L;)X; первой группы Вы;;) I» pi t i)0òp0>3()é н)) х)яти, Р !ЗРЯДЫ ВТОРОИ I 110,1К1К)Ч\

)!bi h СООТВЕТ TBVIO I i I . >1 ()»»PS!.i» М li H()0() Ма—

Ционно ГО Вы xo;Lc Р(. Г!)с! ()13. P»3() )I I i) xl B>TOPoH группы Выходы рс: ис)рош)и памяти и разрядам первой гру);!ы 3).xo,ш;>сгистр» соСТОЯН!)Я, РЗЗРЯ 1Ы BTOPOII ГPX i) )tK !3!>)ХОД(! последнего образуют информационный Выход блока, Bxo Lbl мир(31)лс ))ия Ol<(!)>3!Lit(и рс Гистра, рРГистрОВОи и 4 м))ти, сух! матAj);l, сдВЯгателя и регистр» сост;)HH)i)i подключены соответственно к т; .тьсму, четвертому, !)ятому, шестому, седьмому Выходам дсшифратора, BxO Ibl синхронизации реги(тры, регистровой памяти, с, м»)ор)3. сдв:!гытсля !1 рс1312596

14 гистра состояния подключеill>l соответствсilно к выходам с третьего по седьмой формирователи синхросигпалов, восьмой Выход которого является выходом сигнала исполнения блока.

7. Система по п. 1 или 2, отлинающатя тем„что блок обмена содержит регистр микрокоманд, дешифратор, формирователь синхросигналов, элемент ИЛИ, элемент И, элемент НЕ, арифметический элемент коммутации, интерфейсный элемент коммутации, три приемо-передатчика, коммутатор и регистр, причем информационный вход регистра микрокоманд является входом кода микрокоманды блока, первый и второй входы разрешения приема рсгисгра микрокоманд подключены к первому и второму входам элемента ИЛИ и являются соответственно первым и вторым входами внешнего запуска блока, третий Вход элемс(!та И,(1И является вхо,!ом внутреннего 33HóñKB блока, выход элем HTB

ИЛИ подключен к входу запуска формировате.lH сии хросигHd ioB, >!срв!>!Й выходы которого подключены соотвстсгвспно к синхровходам дешифратора и регистра микрокоманд, выход которого подключен к информационному входу деп!ифратора, первый и Второй выходы которого подключены к соответствующим ьходам арифметического элемента коммутации, первый и нтоРОИ 13X011>I-ВЫХОДbl KOTОРО! О 5IB, 11!IOTCЯ COOTветственно вторыми входами-выходами данНЫХ И H P HB Н с! Ка В1>1Дс1>! И 0, IOKd, а ВЫХОД ПОД клк)чен к стробирук)и!ему входу первог0 приемо-передатчика, первый информационный Вход-Выход которого и информационный вход второго приемо-передатчика являются соответственно вторым входом-выходом адреса и буферным входом олока, второй i!Iiформационный вход-Выход первог0 приемопередатчика подключен к первому информационному вход-выходу коммутатора, ВТорой и третий информационныс входы-выходы которого подклк)чены соответстBBHHo к первому иHôормациоIIHОму входу-выходу трс(ьего приемо-передатчика и информационному входу-выходу регистра, адресный вход коммутатора нодклк)чен к и формационному

Bblx0$1) B (0p0I IlpHci>I0- передатчика, ВТороН и третий информационные входы-выходы третьего приемо-передатчика яьляются COOTветственно первыми входами-выходами адреса H данных блока, стробирующий Вход третьего приемо-передатчика подключен к выходу интерфейсного элемснта коммутации, первый и второй входы-выходы которого являются соответственно IiepBBIII входомВыходом признака выда IH и входом-выходoM признака приема блока, первый, второй и третий Входы ин гсрфсйсного э;!емснта коммута(!ии подключены соответственно к третьему Выходу де!ппфратора, Входу элемента

1!Г и чстве!Хгому выходу дешифратора, выход элемента НЕ подклк)чен к первому входу элемента И. второй Вход которого подключен

5 !

О 15

cg к третьему выходу деп!ифратора, третий вход элемента И подключен к первому входу-выходу арифметического элемента коммутации, выход элемента И и вход элемента HE являются соответственно выходом захвата и Входом разрешения захвата блока, пятый и шестой выходы дешифратора подключены соответственно к входам управления операцией регистра H коммутатора, синхровходы которых подключены соответственно к третьему и четвертому выходам формирователя синхросигналов, пятый выход которого является

Выходом прира!цения адреса блока.

8. Система по п. 1 или 2, или 6, или 7, отличающаяся тем, что арифметический элемент коммутации содержит два элемента И, элемент НЕ и элемент И:!И, причем первые входы элементов И являк)тся соответственно первым и вторым входами арифметического элемента коммутации, Выходы первого и второгO элемсHToB И подключены соответственно к Второму входу второго элемента И и к ВХОД>> элемента 111 ., ВыхОд KoTopol подкл!очен к второму В. оду первог0 элемента И, первый и второй входы элемента ИЛИ поTключены соответственно к Выходам первого и второго элементов И и являются соо