Устройство для управления производственным процессом ремонта машин

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для автоматизации управления производственным процессом ремонта машин. Цель изобретения - расширение функциональных возможностей устройства за счет автоматизации его функционирования в реальном масштабе времени. Устройст

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1.80„„1314 (51)4 G 05 В 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3955320/24-24 (22) 17,09.85 (46) 30 05.87. Бюл. ¹ 20 (71) Уфимский авиационный институт им. Серго Орджоникидзе (72) И.Ю.Юсупов, И.И.Парфенов, М.Я.Парфенова и А.И.Хомяков (53) 621.503.55 (088.8) (56) Авторское свидетельство СССР № 354416, кл. G 06 F 15/20, 1971.

Авторское свидетельство СССР

¹ 723514, кл. С 05 В 19/00, 1980. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОИЗВОДСТВЕННЫМ ПРОЦЕССОМ РЕМОНТА МАШИН (57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано для автоматизации управления производственным процессом ремонта машин. Цель изобретения — расширение функциональных возможностей устройства за счет автоматизации его функционирования в реальном масштабе времени. Устройст1314305 во работает в режиме активного советчика с учетом специфики производства, резерва времени и реальной обстановки на производстве, что приводит к снижению издержек от хранения деталей на промежуточных складах, уменьшению простоя сборочного конвейера, увеличению производительности труда и снижению себестоимости выпускаемой продукции. Поставленная цель достигается тем, что в устройстве для управления производственным процессом ремонта машин третьи выходы блока 1 ввода информации соединены со вторыми информационными входами первого

Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматизации управления производственным процессом ремонта машин.

Цель изобретения — расширение функциональных возможностей устройства за счет автоматизации его функционирования в реальном масштабе времени.

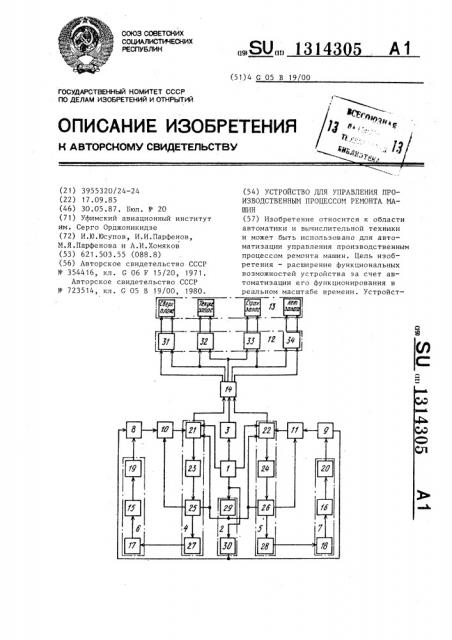

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит блок 1 ввода информации, блок 2 управле»ия, первый регистр 3, первый 4 и второй 5 блоки анализа, первый 6 и второй 7 блоки формирова»ия задания, первый 8 и второй 9 блоки памяти, второй 10., третий 11 и четвертый 12 регистры, блок 13 индикации, дешифратор 14.

Блоки формирования заданий соответственно содержат сумматоры 15 и 16, блоки 17 и 18 памяти, дешифраторы 19 и 20, Блоки анализа соответственно содержат реверсивные счетчики 21 и

22, первые блоки 23 и 24 памяти, арифметико-логические элементы 25 и

26, вторые блоки 27 и 28 памяти.

Блок управления содержит первый 29 и второй 30 триггеры. Регистр 4 содержит первый 31, второй 32, третий

33 и четвертый 34 триггерь:.

Устройство работает следующим образом.

На панели (»e показана) блока 1 ввода информации от базовой детали

28

4 и второго 5 блоков а»ализа соответственно, вторые выходы которых подключены ко вторым входам второго 10 и третьего 11 региcòpoH, а третьи выходы — к соответствующим входам дешифратора 14, первый выход блока управления 2 соединен с первыми и вторыми управляющими входами блоков 4 и 5 анализа, второй выход — с входами первого 8 и второго 9 блоков памяти, а выходы первого регистра 3 подключены к соответствующим входам дешифратора, выходы которого соединены с четвертым 12 регистром. 3 з.п. ф лы 1 ил.

2 набираются фрагме»ты информации А =

1 — а,... а,, а как о годных к дальнейшему применению после дефектовки, так и о восстановле»нь1х иэноше»ных деталях (а„,...,,а,,а, — числа, при»имающие эначе»ия 0,1,..., g - 1; Д— основание A,;;; a „ф 0; Л; ф О) . Они поступают в первый регистр 3 и на входе дешифратара 14 приобретают вид последовательностг (Л ), Одновременно с блока 1 ввода »i-:формации в реверсивные счетчики 21 22 блоков 4 и 5 анализа, заносятс чере 3 тригrep 29 блока 2 управле»и фрагме»ты информации соответственно о пла»е вь пуска деталей 1 Б;) в цехах-поставщиках и о плане (С;) их потребле»ия на сборочном ко»вейере, для чего с третьих выходов блока 1 ввода информации о базовой детали одиночным импульсом peBeðñèâíûe счетчики 21 и 2? устанавливаются в состояние 0 . При этом с панелей (не показаны) регистров 10 и 11 на первые входы реверсивных счетчиков 21 и 22 поступают сигналы соответствен»о о фактическом выпуске

D,j деталей в цехах-поставщиках и фактическом потреблении Е,) их на сборочном ко»вейере„ а с панелей (не показаны) блоков 8 и 9 эа»осится ин— формация соответственно о программе поставки и программе потребления комплектующих деталей по различным вариантам ее выполне»ия.

В случае образования несовпадений (Б;1 f (13;), (C;) Ф (Е;) va входах бло1314305 4 анализа появляются сигналы рассогла сования нплан-факт", которые отражаются на заранее выявленные в ходе управленческих игр значения (R;) оставшихся ресурсов, возникающие изза отклонений в ресурсах по трудозатратам, количеству оборудования, материалу, которые хранятся в блоках

23 и 24 памяти. Поступившие на входы арифметико-логических элементов

25 и 26 (здесь же присутствуют сигналы (B ) и {С;) ) сигналы fR ) лев ресчитываются в сигналы jS;), отображающие соответствующий кортеж производственных ситуаций, выявленных заранее в ходе управленческих игр, а в блоках 27 и 28 памяти сигналы Я через усредненное по Хемингу расстояние приводятся по его минимуму в соответствие с типовыми ситуациями (,)

Э1

S,, хранимыми здесь, относительно которых имеются выявленные в ходе управленческих игр типовые способы

1С ) их устранения, которые хранятся в блоках 17 и 18 памяти блоков 6 и 7 формирования задания. Преобразованные э здесь в 1С ) сигналы (Б; ) поступают на входы сумматоров 15 и 16, где происходит выбор оптимальных С„ по резерву времени t и если устранение возникающих на выходах реверсивных счетчиков 21 и 22 сигналов рассогласования "план-Факт" укладывает— ся в директивное время >,> то

Р 117 7 выбор jC ) заканчивается. Появившиеся на входах дешифраторов 19 и 20 выбранные сигналы IC ) сужаются до

Гo) сигналов С ), соответствующих критерию наибольшей оптимальности различных вариантов программы, заранее рассчитанных и учтенных построением дешифраторов 19 и 20.

Г о

Сигналы 1С„„ поступают на первые входы блоков 8 и 9, куда одновременно на вторые входы попадают сигналы обращения с триггера 29 блока 2 управления, и на выходах блоков 8 и 9 появляются сигналы, соответствующие возможным объемам выпуска продукции по тем или иным вариантам выполнения программы. Они поступают в регистры

10 и 11, которые со своих вторых входов предварительно устанавливаются в состояние "0" с арифметико-логических элементов 25 и 26, и на первых входах реверсивных счетчиков 21

20 ков 23 и 24 памяти и блоков 4 и 5

55 и 22 появляются новые значения jD;j и {E;), на третьих их выходах появляются состояния, соответствующие разностям (D; } и (H;) и (C 1 и (t!;), Разностные сигналы с реверсивных счетчиков 21 и 22 блоков 4 и 5 анализа и (R;) с блока накопления информации об укомплектованных базовых деталях поступают на входы дешифра тора 14, на выходах которого в зависимости от комбинации (Л;, (B;), (c;), (D;) и (о;1 открывается один из триггеров 31-34 регистра 12, на выходе которых соответственно заго,рается табло "Сверх плана", "Текущий запас", "Страховой запас", "Нет запаса" блока 13 индикации.

Формула изобретения

1. Устройство для управления производственным процессом ремонта машин, содержащее блок ввода информации, первый выход которого соединен с первым и вторым входами блока управления, а второй выход подключен к входу первого регистра, первый и второй блоки анализа, первые выходы которых соединены с входами соответственно первого и второго блоков формирования задания, выходы которых подключены к первым информационным входам первого и второго блоков памяти, выходы которых подключены к первым информационным входам соответственно второго и третьего регистров, выходы которых подключены к первым информационным входам первого и второго блоков анализа, четвертый регистр, выходы которого подключены к входам блока индикации, дешифратор, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет автоматизации его функционирования в реальном масштабе времени, третьи выходы блока ввода информации соединены с вторыми информационными входами соответственно первого и второго блоков анализа, вторые выходы которых подключены к вторым входам соответственно второго и третьего регистров, а третьи выходы — к соответствующим входам дешифратора, первый выход блока управления соединен с первыми и вторыми управляющими входами блоков анализа, второй выход подключен к вторым информационным входам

i 314305

Составитель Ю.Бельских

Техред М. Ходанич Корректор О.Тигор

Редактор А.Ревин

Заказ 2212/48

Тираж 864 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 первого и второго блоков памяти, выходы первого регистра подключены к соответствующим входам дешифратора, выходы которого соединены с входом четвертого регистра, 2. Устройство пon.1, о т л и— ч а ю щ е е с я тем, что блок управления содержит первый и второй триггеры, установочные, входы которых являются соответственно первым и вторым входами блока, а выходы соответственно первым и вторым выходами блока.

3. Устройство по п„1, о т л и— ч а ю щ е е с я тем, что блок анализа содержит первый и второй бло.ки памяти, арифметико-логический эле мент и счетчик, выход второго блока памяти является первым выходом блока, а вход подключен к выходу арифметико-логического элемента, выход которого является вторым выходом блока, второй вход — вторым управляющим входом блока, а третий вход подключен к выходу второго блока памяти, входом подключенного к первому выходу счетчика, второй выход которого является третьим выходом блока, а первый и второй входы — соответственно первым и вторым информационными входами блока, а третий вход— вторым управляющим входом блока.

4. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что блок формирования задания содержит блок памяти, сумматор и дешифратор, выход которого является выходом блока, а вход соединен с выходом сумматора, вход которого соединен с выходом блока памяти, вход которого является входом блока.