Устройство для ввода информации от двухпозиционных датчиков

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода информации от ДВУХПОЗИЦИОННЫХ датчиков в устройствах сбора и обработки информации. Целью изобретения является повышение достоверности вводимой информации. Цель достигается благодаря возможности вести опрос датчиков с частотой, изменяющейся по геометрической прогрессии. Датчики объединяются по степени важности (частоте срабатывания)в Р групп опрос наиболее важных групп датчиков ведется с более высокой частотой. Устройство содержит генератор импульсов, счетчик, два триггера, блок памяти (ОЗУ), коммутатор и шифратор (ПЗУ). С помощью шифратора задается частота опроса отдельных групп датчиков. 2 ил., 1 табл. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (39> Я 0 (11) (5D 4 G 06 F 3/05

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4052928/24-24 (22) 03.03.86 (46) 30.05.87. Бюл. Ф 20 (72} И.А.Козачук, В.Г.Руденко, В.Ф.Плюснин и Н.Г.Тимоха (53) 681.32(088.8) (56) Авторское свидетельство СССР

У 614434, кл. G 06 F 3/05, !976.

Авторское свидетельство СССР

И - 1019430, кл. G 06 F 3/05, 1983. (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ

ОТ ДВУХПОЗИЦИОННЫХ ДАТЧИКОВ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода информации от двухпозиционных датчиков в устройствах сбора и обработки информации. Целью изобретения является повьппение достоверности вводимой информации. Цель достигается благодаря возможности вести опрос датчиков с частотой, изменяющейся по геометрической прогрессии. Датчики объединяются по степени важности (частоте срабатывания) в P групп, опрос наиболее важных групп датчиков ведется с более высокой частотой. Устройство содержит генератор импульсов, счетчик, два триггера, блок памяти (ОЗУ), коммутатор и шифратор (ПЗУ), С помощью шифратора задается частота опроса отдельных групп датчиков.

2 ил., 1 табл.

1 l3)

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода информации от двухпозиционных датчиков в устройства сбора и обработки информации.

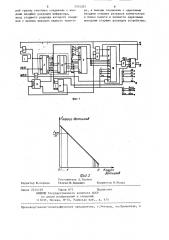

Целью изобретения является повышение достоверности вводимой информации, На фиг.l приведена функциональная схема предлагаемого устройства; на фиг.2 — график зависимости частоты опроса датчиков от номера группы датчиков.

Устройство содержит генератор импульсов, первый элемент И вЂ” НЕ 2, счетчик 3, первый элемент И 4, первый триггер 5, коммутатор 6, второй

7 и третий 8 элементы И, элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ 9, блок IO памяти, второй элемент И-НЕ Il, второй триггер 12, шифратор 13. Кроме того, дополнительно на фиг.l обозначены, позицией 14 условно функциональные датчики, позициями 15-19 входы и выходы устройства.

Блок 10 памяти представляет собой оперативное запоминающее устройство, состояние триггеров их ячеек памяти которого после включения устройства не определено. Поэтому в устройстве предусмотрен режим начальной установ ки, при котором в ячейки памяти блока 10 производится запись логических

О. После начальной установки устройство переходит в режим опроса датчиков.

Устройство работает следующим образом.

В режим начальной установки устройство переходит при подачи на его вход 16 импульса начальной установки. По этому импульсу триггер 5 устанавливается в единичное, а счетчик

3 — в нулевое состояние. Тактовые импульсы от генератора 1 через элемент И-НЕ 2, открытый по второму входу уровнем с выхода триггера 12, поступают на счетчик 3, работающему в режиме суммирования, а так же через элемент И 4 — на вход синхронизации блока 10. На информационном входе и входе задания режима блока

10 устанавливаются логические 0— режим записи 0 в ячейку счета блока 10, соответствующую состоянию его адресных входов. При осуществлении записи "0" в последнюю ячейку блока

4331 I0

10 на выходе элемента И-НЕ 11 выраба. тывается импульс отрицательной полярности, переводящий триггер 5 в нулевое состояние ° Устройство переходит в режим опроса датчиков по информационным входам коммутатора 6. На входе выбора режима блока 10 устанавливается "1", переводящая блок

l0 в режим чтения, а на информационный вход блока 10 поступает сигнал состояния опрашиваемого датчика. Этот же сигнал поступает на информационный выход устройства и на первый вход элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 9, где сравнивается с содержимым соответствующей ячейки памяти блока 10. При их несоответствии на выходе элемента ИСКЛЮЧА1О1ЦЕЕ ИЛИ 9 возникает сигнал, который переводит триггер 12 в единичное состояние, формируя сигнал готовности устройства. Логический 0 с инверсного выхода триггера 12 запрещает прохождение тактовых импульсов и на входе синхронизации блока 10 устанавливается сигнал логической 1, а на входе выбора режима — логический 0 (режим записи). По сигналу готовности 3ВМ считывает состояние информационно— го и адресных выходов устройства и выдает на вход 15 записи устройства импульс, по которому информация, присутствующая на информационном входе блока 10 записывается в соответствующую ячейку памяти и сбрасывает триггер 12

При этом разрешается счет счетчика 3 и устанавливается режим чтения блока 10, Устройство переходит к дальнейшему опросу датчиков.

Датчики, исходя из степени важности (частота. переключений), объединяются в Р групп. Весовые коэффициенты счетчика 3 от 0 до (k-1) опк ределяют количество датчиков f =2 в каждой группе Р;,и посредством которых опрашиваются датчики внутри групп

P. Сигналы, поступающие из 1-разрядного шифратора 13 на старшие адресные входы коммутатора, определяют номер соответствующей опрашиваемой группы датчиков P.. т.е. максимальное количество групп датчиков определяется разрядностью шифратора 13 и равно е+

P = 2 . Данные, приведенные в таблице, отражают содержимое шифратора.

Для опроса групп датчиков с частотой. убываюшей по геометрической

131 331 4 пы с К по Р, и опрос каждого датчика ведется через опрос группы. прогрессии по отношению к номеру. группы, начиная с первого, необходи мо составить массив содержимого шифратора 13, имеющий (и+1).-разрядный вход и 1-разрядный выход.

Для зоны старших адресных разрядов, когда (и+1) разряд равен 1, что определяется состоянием триггера 5, выходная информация равна входной Е ы„ =F „, содержимое шифрато- 10 ра определяется информацией на выходе счетчика 3, т.е. опрос датчиков ведется с одной частотой. Это необходимо в начальный момент времени при записи первоначальной информации о состоянии всех датчиков в блок 1О памяти. При опросе последнего дат(+! чика f в последней группе 2, на выходе элемента И-НЕ 11 появляется сигнал логического О, который пере- 20 водит триггер 5 в состояние логического 0 и сигнал, с выхода которого поступает на (n+1) разряд шифратора 13.

Тогда для зоны младших разрядов, 25 когда (и+1) разряд равен нулю, содержимое шифратора 13 по адресу п; должно быть численно равным номеру первого младшего разряда двоичного числа адреса, начиная с нулевого, имею- 30 .щего значение логической I.

Например,для адреса 66 о=1000100

Согласно сказанному по адресу

66„ 13 будет составлять Fsbix 2, так как самый младший разряд, имеющий значение логической 1, является вторым, т.е. опрашивается вторая группа датчиков.

Содержимое шифратора 13 при 16разрядном адресе определяется исходя 40 из данных таблицы при количестве групп датчиков m=0...15.

Частота опроса датчиков обратно пропорциональна группам датчиков (фиг.2). В соответствии с графиком 45 на фиг.2 группа датчиков с первого генео по К-й имеет f а с К-го опроса ш

55 ген по P-й опроса ниже чем †--., где

Э

m ген

m — общее число датчиков — — часj тота опроса датчиков при последовательном опросе.

Наиболее важные датчики, опрос которых необходимо вести с высокой частотой, объединяют группы с первой по К, а менее важные — в групФо р мул а и з о б р е т ения

Устройство для ввода информации от двухпозиционных датчиков, содержащее генератор, счетчик, коммутатор, блок памяти, первый и второй триггеры, с первого по третий элементы И, первый и второй элементы И-НЕ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход генератора соединен с первым входом первого элемента И-НЕ, выход которого соединен со счетным входом счетчика и первым входом первого элемента И, второй вход которого является входом запуска устройства, вход сброса счетчика и вход установки первого триггера являются входом начальной установки устройства, выходы первой группы счетчика соединены с входами второго элемента И-НЕ, с адресными входами младших разрядов коммутатора и с адресными входами младших разрядов блока памяти и являются адресными выходами младших разрядов устройства, информационные входы коммутатора являются информационными входами устройства, выход коммутатора соединен с вторым входом третьего элемента И, выход которого соединен с информационным входом блока памяти, с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является информационным выходом устройства, выход блока памяти соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, выход которого соединен с синхровходом второго триггера, инверсный выход которого соединен с вторыми входами первого элемента И-НЕ и второго элемента И, а прямой выход является выходом готовности устройства, выход второго элемента И-НЕ сое-. динен с входом сброса первого триггера, инверсный выход которого соединен с первыми входами второго и третьего элемента И, выход второго элемента И соединен с входом задания режима блока памяти, выход первого элемента И соединен с входом синхронизации блока памяти и входом сброса второго триггера, информационный вход которого соединен с шиной логической единицы, о т л и ч а ю щ ее с я тем, что,с целью повышения достоверности вводимой информации, в него введен шифратор, выходы вто» фие. 1

Кгж

Р / групп дот ил 8

Составитель А.Трунов

Техред М. Ходанич Корректор И.!Чулла

Редактор Ю,Середа

Заказ 2214/49 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная, 4

5 1314331 6 рой группы счетчика соединены с вхо- ра, а выходы соединены с адресными дами младших разрядов шифратора, входами старших разрядов коммутатора вход старшего разряда которого соеди- и блока памяти и являются адресными нен с прямым выходом первого тригге- выходами старших разрядов устройства.